- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

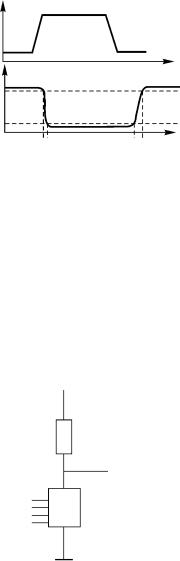

UВХ

UВЫХ |

t |

|

|

0,9 |

|

0,1 |

t |

|

|

~ IРАЗРЯДА |

~ IЗАРЯДА |

Рис.9.21. Переходная характеристика инвертора на полевых транзисторах

Исключением является КМОП-инвертор, в котором U0 = 0 и для выравнивания фронтов переключения задают Kn0 = Kp0.

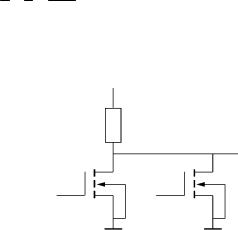

9.8. Логические элементы на МОП-транзисторах

Логическая функция в элементах выполняется с помощью группы переключающих транзисторов, к затворам которых подключены входные напряжения (рис.9.22).

UИП

ZН

UВЫХ

UВХn

UВХ1

Рис.9.22. Обобщенная схема многовходового логического элемента

193

При этом необходимо отметить, что нагрузка к группе переключающих транзисторов подключается единая.

1. Группа переключающих транзисторов, включенных последовательно.

Рассмотрим ее на примере двухвходового логического элемента (рис.9.23).

UИП

ZН

F

AMА

BMВ

Рис.9.23. 2И-НЕ логический элемент

В табл.9.1 приведены режимы работы транзисторов логического элемента.

Таблица 9.1

Таблица истинности элемента с последовательно включенными транзисторами

А |

В |

F |

Примечания |

0 |

0 |

1 |

МА, МВ закрыты |

0 |

1 |

1 |

МА закрыт |

1 |

0 |

1 |

МВ закрыт |

|

|

|

Сквозной ток протекает |

1 |

1 |

0 |

через открытые МА-, МВ- |

|

|

|

транзисторы |

Считав логическую функцию с таблицы истинности в совершенной конъюнктивной форме для F = 0, получим:

194

F = A + B = A× B.

Таким образом, последовательно включенные транзисторы в переключающей группе выполняют логическую функцию И-НЕ.

2. Группа переключающих транзисторов, включенных параллельно (рис.9.24).

UИП |

|

ZН |

|

|

F |

MА |

MB |

A |

B |

Рис.9.24. 2ИЛИ-НЕ логический элемент

В табл.9.2 приведены режимы работы транзисторов логического элемента.

|

|

|

|

Таблица 9.2 |

|

|

Таблица истинности элемента |

|

|||

с параллельно включенными транзисторами |

|

||||

А |

В |

F |

Примечания |

|

|

0 |

0 |

1 |

МА, МВ закрыты |

|

|

|

|

|

Сквозной ток протекает |

||

0 |

1 |

0 |

через |

открытый |

МВ- |

|

|

|

транзистор |

|

|

|

|

|

Сквозной ток протекает |

||

1 |

0 |

0 |

через |

открытый |

МА- |

|

|

|

транзистор |

|

|

|

|

|

Сквозной ток протекает |

||

1 |

1 |

0 |

через открытые МА-, МВ- |

||

|

|

|

транзисторы |

|

|

Считав логическую функцию с таблицы истинности в совершенной дизъюнктивной форме для F = 1, получим:

195

F = A× B = A + B .

Таким образом, параллельно включенные транзисторы в переключающей группе выполняют логическую функцию ИЛИ-НЕ.

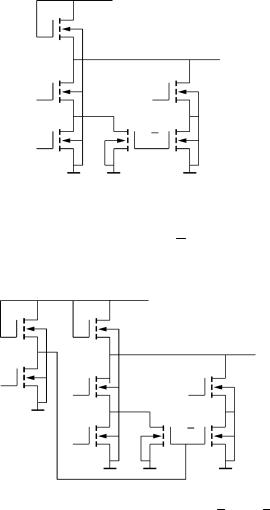

Пример. Разработать электрическую схему для выполнения логической функции

F= (A + CD)× (B + C)

вn-МОП-базисе с нелинейной нагрузкой.

1. Поскольку в n-МОП базисе логическая функция всегда имеет инверсию, то необходимо преобразовать заданную логическую функцию с помощью правила двойной инверсии к базису И- ИЛИ-НЕ:

F= (A + CD)× (B + C)= (A + CD)+ (B + C)=

=А×CD + В ×С = А×(С + D)+ B ×С .

2.Для разработки электрической схемы учтем, что логиче-

ское умножение реализуется последовательным включением транзи-

сторов переключающей группы, а логическое сложение - параллельным включением транзисторов (рис.9.25).

|

UИП |

|

|

|

ZН |

F |

|

|

|

||

M1 |

B |

M4 |

|

A |

|

||

M2 |

M3 |

M5 |

|

C |

|||

D |

|

Рис.9.25. Электрическая схема соединения n-МОП переключающих транзисторов логического элемента

196

3. Теперь необходимо подключить единую нагрузку, соответствующую заданному типу логики (рис.9.26).

MН |

UИП |

|

|

|

|

|

|

F |

M1 |

|

M4 |

A |

|

B |

M2 |

M3 |

M5 |

|

||

D |

|

C |

Рис.9.26. Электрическая схема логического элемента с нелинейной нагрузкой

4. Для задания инверсного сигнала C в электрическую схему включается инвертор (рис.9.27).

|

MН |

MН |

UИП |

|

|

|

|

||

|

|

|

|

F |

С |

M6 |

M1 |

|

M4 |

|

A |

|

|

B |

|

|

M2 |

M3 |

M5 |

|

D |

|

||

|

|

|

C |

Рис.9.27. Полная электрическая схема логического элемента, выполняющего логическую функцию F = (A + CD)(B + C)

197