- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

4. Элементная база на биполярных транзисторах

По технологическим и ряду других причин, связанных с электрофизическими параметрами полупроводниковых материалов, в интегральных схемах часто используют кремниевую технологию. Наиболее широко применяют n–p–n-транзисторы, так как вследствие большей подвижности электронов в базе они имеют лучшие электрические параметры - более высокие граничные частоты и быстродействие.

4.1. Формирование биполярных транзисторов

Основные различия интегральных биполярных транзисторов (ИБТ) полупроводниковых ИС от дискретных транзисторов:

1)ИБТ содержат дополнительные области, изолирующие их от общей подложки и друг от друга;

2)все выводы от областей ИБТ располагаются в одной плоскости на поверхности подложки; такая структура

называется планарной. Требования к структурам:

1)площадь, занимаемая ИБТ на полупроводниковой подложке, должна быть минимально возможной для повышения плотности упаковки элементов и степени интеграции;

2)конструкция и технология изготовления ИБТ должны обеспечивать возможность одновременного создания других элементов (диодов, резисторов, конденсаторов) на основе полупроводниковых слоев, исполь-

зуемых при формировании ИБТ. Используемые методы изоляции элементов:

1)с помощью обратносмещенных p–n-переходов;

2)с помощью окисных диэлектрических областей;

3)посредством комбинированной изоляции.

50

Метод изоляции с помощью обратносмещенных p–n-переходов по сравнению с другими характеризуется большими площадями изолирующих областей и более значительными паразитными емкостями.

Широкое распространение получили ИС, создаваемые по изопланарной технологии с диэлектрической изоляцией.

4.2. Основные операции в изопланарной технологии

Исходным материалом является подложка p-типа N 1015 см–3,

ориентированная по плоскости (111) или (100) (рис.4.1).

p

Рис.4.1. Исходная полупроводниковая пластина

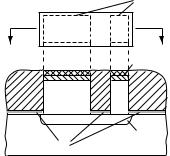

1. Формирование скрытого слоя (рис.4.2):

A A

Фоторезист

SiO2

p n+

Рис.4.2. Формирование скрытого слоя: шаблон и структура

1)окисление SiO2;

2)покрытие фоторезистом;

3)фотолитография (т.е. засвечивание активных областей элементов);

4)вскрытие окон в маскирующем слое SiO2;

51

5) диффузия скрытого слоя (ионная имплантация мышьяка или сурьмы).

Имплантированный слой путем термической обработки разгоняют в глубь подложки

Nc.c = 1015 ÷1016 см−3;

ρ ( + ) = 15 ÷ 20 Ом/квадрат ;

S n − c.c

n+-скрытый слой используется в качестве сильнолегированной области коллектора, предназначенной для уменьшения сопротивления коллектора.

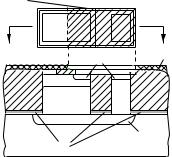

2. Наращивание эпитаксиального слоя (рис.4.3):

n-эп.сл

n+

p

Рис.4.3. Формирование эпитаксиального слоя

1)удаление окисла со всей поверхности подложки;

2)эпитаксиальное наращивание слоя n-типа, являющегося коллекторной областью n–p–n-транзистора.

3. Формирование на поверхности пластины защитных слоев

(рис.4.4):

Si3N4

n-эп.сл SiO2 p n+

Рис.4.4. Формирование защитных слоев

1)выращивание путем термического окисления SiO2 50 нм;

2)осаждение на поверхность Si3N4 100 нм.

52

SiO2 - буферный слой, предназначенный для защиты кремния от возникновения дефектов, обусловленных упругими напряжениями в ходе последующего высокотемпературного окисления.

Si3N4 плохо окисляется, предотвращая окисление лежащих под ним слоев.

4. Формирование изоляции (рис.4.5):

|

|

|

Шаблон |

|

|

|

изоляции |

A |

|

|

A |

|

|

|

Si3N4 |

|

n |

n |

SiO2 |

p |

p+ |

|

n+ |

|

|

Рис.4.5. Формирование изолирующих областей: шаблон и структура

1)покрытие фоторезистом;

2)фотолитография изолированных областей;

3)удаление Si3N4, SiO2 и половины эпитаксиального слоя путем травления в местах изоляции элементов;

4)ионная имплантация бора в протравленные участки для формирования областей, ограничивающих распространение канала n- типа.

Цель операции - увеличение уровня легирования подложки p-типа под изолирующим окислом, предотвращающим инверсию проводимости поверхности слаболегированной подложки p-типа;

5)удаление фоторезиста;

6)термическое окисление SiO2;

7)удаление Si3N4.

Отметим, что высокотемпературные и длительные циклы проводятся до формирования активных областей транзистора, чтобы избежать слишком глубокой разгонки мелких p–n-переходов.

53

5. Формирование области базы (рис.4.6):

Шаблон

базы

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Фоторезист

|

p |

|

SiO2 |

|

n |

n |

|

p |

p+ |

|

n+ |

|

|

Рис.4.6. Формирование базовой области: шаблон и структура

1)окисление поверхности SiO2;

2)нанесение фоторезиста;

3)фотолитография области базы;

4)ионная имплантация бора в базовую область.

Имплантация бора проводится через пленку окисла, поэтому процесс каналирования ионов примеси ослабевает и отпадает необходимость в послеимплантационном отжиге в окисляющей среде;

NБ = 1016 |

см–3; |

|

|

5) удаление фоторезиста. |

|

|

|

6. Вскрытие контактных окон (рис.4.7): |

|||

|

Шаблон |

|

|

|

КО |

|

|

|

A |

|

A |

|

|

|

Фоторезист |

|

|

p |

n SiO2 |

|

|

n |

|

|

p |

p+ |

n+ |

|

|

||

Рис.4.7. Формирование контактных окон: шаблон и структура |

|||

54

1)нанесение фоторезиста;

2)фотолитография контактных окон;

3)травление в областях контакта.

Расстояние между базой и эмиттером определяется по минимально допустимому размеру расположения контактных окон, что приводит к уменьшению размеров транзистора и снижению сопротивления базы, т.е. увеличению быстродействия; 4) удаление фоторезиста.

7. Формирование областей эмиттера и подлегирование контакта к коллектору (рис.4.8):

Шаблон |

|

эмиттера |

|

A |

A |

|

|

n+ Фоторезист |

|

|

p |

|

SiO2 |

|

n |

n |

|

p |

p+ |

|

n+ |

|

|

||

Рис.4.8. Формирование областей эмиттера и подлегирование области контакта к коллектору: шаблон и структура

1)нанесение фоторезиста;

2)фотолитография областей эмиттера и коллектора;

3)ионная имплантация n+-ионов мышьяка с малой энергией, но большой дозой.

Площадь эмиттера определяется минимально допустимым размером контактного окна;

4)разгонка на нужную глубину.

Поверхность покрывается тонким слоем окисла

NЭ =1020 см−3 , Х j Э = 0,5 мкм .

55