- •1. Основы микросхемотехники ИС

- •1.1. Основные термины и определения

- •1.2. Этапы и направления развития ИС

- •1.3. Классификация ИС

- •1.3.4. Классификация по степени интеграции

- •1.4. Последовательность разработки ИС

- •2. Основы цифровой техники

- •2.3. Основные логические операции

- •2.4. Формы представления логической функции

- •2.5. Структурное проектирование цифровых схем комбинационного типа

- •3. Основные параметры и характеристики ЦИС

- •3.1. Основные параметры ЦИС

- •3.2. Характеристики ЦИС

- •3.3. Определение измеряемых параметров по характеристикам

- •4.1. Формирование биполярных транзисторов

- •4.3. Эквивалентная модель интегрального n–p–n биполярного транзистора

- •4.4. Режимы работы биполярного транзистора

- •4.6. Статические ВАХ транзистора

- •5. Диоды в интегральных схемах

- •5.1. Модель идеального диода

- •5.2. Эквивалентная схема интегрального диода

- •5.3. Аппроксимации ВАХ диода

- •5.4. Варианты реализации интегральных диодов

- •6. Пассивные элементы ИС

- •6.1. Основные параметры резисторов

- •6.2. Реализация интегральных резисторов

- •6.4. Реализация интегральных конденсаторов

- •7. Элементная база статических ЦИС на биполярных транзисторах

- •7.1. Резисторно-транзисторная логика (РТЛ)

- •7.1.1. Характеристики РТЛ

- •7.2. Эмиттерно-связанная логика (ЭСЛ)

- •7.2.1. Принцип работы

- •7.2.2. Входная характеристика

- •7.2.3. Передаточная характеристика

- •7.2.4. Выходная характеристика

- •7.2.6. Многоярусные ЭСЛ (МяЭСЛ)

- •7.3. Диодно-транзисторная логика

- •7.3.1. Расчет передаточной и входной характеристик

- •7.3.2. Выходная характеристика

- •7.3.3. Влияние нагрузки на логические уровни

- •7.4. Транзисторно-транзисторная логика

- •7.4.1. ТТЛ-элемент с простым инвертором

- •7.4.2. Передаточная характеристика

- •7.4.3. Входная характеристика

- •7.4.4. Выходная характеристика

- •7.4.6. Основные параметры

- •7.4.7. Многоэмиттерный транзистор

- •7.4.8. ТТЛ-элемент со сложным выходным каскадом

- •7.4.9. Модификация логического элемента

- •7.5. Интегральная инжекционная логика

- •7.5.2. Реализация логических функций

- •8. Полевые транзисторы

- •8.1. Типы полевых транзисторов

- •8.2. Определение физических параметров

- •8.3. модель полевого транзистора

- •8.4. Режимы работы и уравнения ВАХ полевого транзистора

- •9. Элементная база на полевых транзисторах

- •9.2. Передаточная характеристика и параметры инвертора с линейной нагрузкой

- •9.3. Передаточная характеристика и параметры инвертора с нелинейной нагрузкой

- •9.4. Передаточная характеристика и параметры инвертора с квазилинейной нагрузкой

- •9.5. Передаточная характеристика и параметры инвертора с токостабилизирующей нагрузкой

- •9.6. Передаточная характеристика и параметры комплементарного инвертора

- •9.8. Логические элементы на МОП-транзисторах

- •9.9. Определение эквивалентной крутизны группы переключающих транзисторов

- •9.11. Влияние параметров транзисторов на характеристики логического элемента

- •9.12. Сопряжение ТТЛ- и КМОП-схем

9. Элементная база на полевых транзисторах

Как отмечалось ранее, цифровые схемы можно создавать, используя элементы, выполняющие основные логические операции: инверсию, дизъюнкцию и конъюнкцию. Рассмотрим основные логические элементы на полевых транзисторах.

9.1. Классификация инверторов на МОПтранзисторах

Структурная схема ключа, или инвертора, или логического элемента, выполняющего функцию НЕ, показана на рис.9.1: М0 - n-МОП-транзистор с индуцированным каналом, выполняющий функцию переключения; ZН - нагрузочный элемент.

UИП

IН ZН

IС UВЫХ

UВХ M0

Рис.9.1. Структурная схема инвертора

Для уменьшения влияния паразитных подложечных переходов необходимо задать на них обратные смещения, т.е. подложку p-типа подключить к наименьшему потенциалу, который используется в питании схемы (при положительном напряжении питания p-подложку соединяют с землей).

При UВХ = U0 так как U0 < UПОР, то М0 работает в РО и IC = 0. Поскольку при подключении к выходу подобных логических

160

элементов мы получим только емкостную нагрузку, то IC = IН = 0

и UВЫХ = UИП = U1.

При UВХ = U1 М0 работает в крутой области и его IC определяется нагрузочным током IН:

IС = IН = UИП -UВЫХ ;

ZН

UВЫХ = U 0 .

По типу нагрузочного элемента различают следующие инверторы.

1. Инвертор с линейной нагрузкой (рис.9.2)

ZН Þ RН;

R |

= |

UИП -UВЫХ0 |

. |

|

|||

Н |

|

IС0 |

|

|

|

||

|

|

UИП |

|

|

|

RН |

|

UВХ |

|

IС |

|

|

M0 |

||

|

|

|

UВЫХ |

Рис.9.2. Инвертор с линейной нагрузкой

2. Инвертор с нелинейной нагрузкой (рис.9.3):

ZН Þ М Н - n-МОП-транзистор с индуцированным каналом, работающий всегда в пологой области

UСИН ³ |

UЗИ |

Н |

- U |

ПОР |

Н |

. |

|

1+ h |

|

|

|||

|

|

|

|

|

||

161

Так как UСИН = UЗИН , это условие всегда выполняется.

UИП

MН

IС |

UВЫХ |

UВХ M0

Рис.9.3. Инвертор с нелинейной нагрузкой

3. Инвертор с квазилинейной нагрузкой (рис.9.4):

ZН Þ М Н - n-МОП-транзистор с индуцированным каналом, работающий всегда в крутой области

UСИН £ |

UЗИ |

Н |

-U |

ПОР |

Н |

. |

|

1+ h |

|

||||

|

|

|

|

|||

|

|

|

UИП |

|

|

|

UЗ |

|

|

MН |

|

|

|

IС |

|

|

UВЫХ |

|||

UВХ |

|

|

M0 |

|

|

|

Рис.9.4. Инвертор с квазилинейной нагрузкой

162

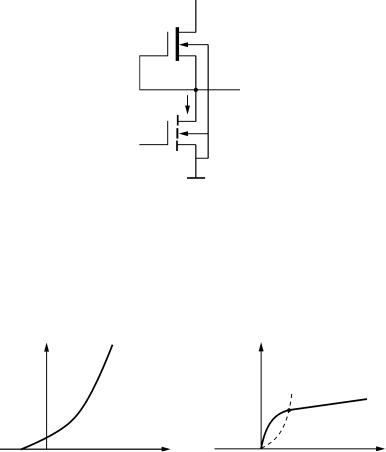

4. Инвертор с токостабилизирующей нагрузкой (рис.9.5): ZН Þ МН - n-МОП-транзистор со встроенным каналом (НО).

UИП

MН

UВЫХ

IС

UВХ M0

Рис.9.5. Инвертор с токостабилизирующей нагрузкой

Из ВАХ МН-транзистора можно определить, что:

при UЗИН = 0 МН открыт (рис.9.6,а);

= UИП UВЫХ (рис.9.6,б);

при UВЫХ = U1 МН работает в крутой области; при UВЫХ = U0 МН работает в пологой области.

IC |

IC |

Н |

Н |

UЗИН |

|

UCИН |

−UОТС |

UИП − U 1 |

UИП − U 0 |

а |

|

б |

Рис.9.6. Режимы работы n-МОП со встроенным каналом: а - проходная ВАХ; б - выходная ВАХ

163

5. Комплементарный МОП-инвер-тор, у которого в паре с n- МОП-тран-зистором Мn используется транзистор Мp дополняющего типа проводимости, т.е. p-МОП с индуцированным каналом

(рис.9.7).

UИП

Mp

UВЫХ

UВХ IС

Mn

Рис.9.7. КМОП-инвертор

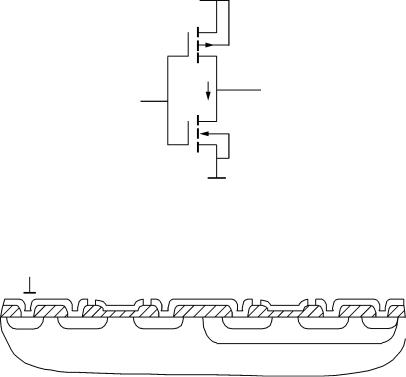

На рис.9.8 приведена структура КМОП-инвертора на p- подложке с n-карманом для p-канального транзистора.

|

Исток Затвор |

Сток |

UВЫХ |

Затвор Исток |

UИП |

|

Сток |

||||

p+ |

n+ |

n+ |

p+ |

n-карман p+ |

n+ |

|

p-подложка |

|

|

|

|

Рис.9.8. Структура КМОП-инвертора

В КМОП-элементах для уменьшения влияния паразитных p– n-переходов выполняют дополнительные контакты. Контакт в подложке p-типа соединяют с шиной земли, а контакт к карману n-типа - с шиной питания. Как правило, такие контакты выполняют на группу транзисторов, топологически расположенных рядом.

164