- •Navigating This Book

- •Table of Contents

- •Introduction

- •The History of Programmable Logic

- •Complex Programmable Logic Devices (CPLDs)

- •Why Use a CPLD?

- •Field Programmable Gate Arrays (FPGAs)

- •Design Integration

- •The Basic Design Process

- •HDL File Change Example

- •Before (16 x 16 multiplier):

- •After (32 x 32 multiplier):

- •Intellectual Property (IP) Cores

- •Design Verification

- •Xilinx Solutions

- •Introduction

- •Xilinx Devices

- •Platform FPGAs

- •Virtex FPGAs

- •Virtex-II Pro FPGAs

- •Virtex FPGAs

- •Spartan FPGAs

- •Spartan-3 FPGAs

- •Spartan-IIE FPGAs

- •Spartan-IIE Architectural Features

- •Xilinx CPLDs

- •XC9500 ISP CPLD Overview

- •XC9500XL 3.3V Family

- •XC9500XV 2.5V CPLD Family

- •CoolRunner Low-Power CPLDs

- •CoolRunner-II CPLDs

- •CoolRunner Reference Designs

- •Military and Aerospace

- •Automotive and Industrial

- •Design Tools

- •Design Entry

- •Synthesis

- •Implementation and Configuration

- •Board-Level Integration

- •Verification Technologies

- •Advanced Design Techniques

- •Embedded SW Design Tools Center

- •Xilinx IP Cores

- •Web-Based Information Guide

- •End Markets

- •Silicon Products and Solutions

- •Design Resources

- •System Resources

- •Xilinx Online (IRL)

- •Configuration Solutions

- •Processor Central

- •Tools and Partnerships

- •Memory Corner

- •Silicon

- •Design Tools and Boards

- •Technical Literature and Training

- •Connectivity Central

- •High-Speed Design Resources

- •Signal Integrity Tools

- •Partnerships

- •Signal Integrity

- •Services

- •Xilinx Design Services

- •Education Services

- •Live E-Learning Environment

- •Day Segment Courses

- •Computer-Based Training (CBT)

- •University Program

- •Design Consultants

- •Technical Support

- •Module Descriptions

- •WebPACK Design Suite

- •WebPACK Design Entry

- •WebPACK StateCAD

- •WebPACK MXE Simulator

- •WebPACK HDL Bencher Tool

- •WebPACK FPGA Implementation Tools

- •WebPACK CPLD Implementation Tools

- •WebPACK iMPACT Programmer

- •WebPACK ChipViewer

- •XPower

- •WebPACK CD-ROM Installation

- •Getting Started

- •Licenses

- •Projects

- •Summary

- •Introduction

- •Design Entry

- •The Language Template

- •Close the Language Templates

- •Edit the Counter Module

- •Save the Counter Module

- •Functional Simulation

- •State Machine Editor

- •Top-Level VHDL Designs

- •Top-Level Schematic Designs

- •ECS Hints

- •I/O Markers

- •Implementing CPLDs

- •Introduction

- •Synthesis

- •Constraints Editor

- •CPLD Reports

- •Timing Simulation

- •Configuration

- •Implementing FPGAs

- •Introduction

- •Synthesis

- •The Constraints File

- •FPGA Reports

- •Programming

- •Summary

- •Design Reference Bank

- •Introduction

- •Get the Most out of Microcontroller-Based Designs

- •Conventional Stepper Motor Control

- •Using a Microcontroller to Control a Stepper Motor

- •Stepper Motor Control Using a CPLD

- •PC-Based Motor Control

- •Design Partitioning

- •Conclusion

- •Documentation and Example Code

- •Website Reference

- •ACRONYMS

- •GLOSSARY OF TERMS

PROGRAMMABLE LOGIC DESIGN: QUICK START HANDBOOK • CHAPTER 1

There are also costs associated with inventory and reliability. PLDs can reduce inventory costs by replacing standard discrete logic devices. Standard logic has a predefined function. In a typical design, lots of different types have to be purchased and stocked. If the design is changed, there may be excess stock of superfluous devices.

This issue can be alleviated by using PLDs. You only need to stock one device; if your design changes, you simply reprogram. By utilizing one device instead of many, your board reliability will increase by only picking and placing one device instead of many.

Reliability can also be increased by using ultra-low-power CoolRunner CPLDs. Their lower heat dissipation and lower power operation leads to decreased FIT.

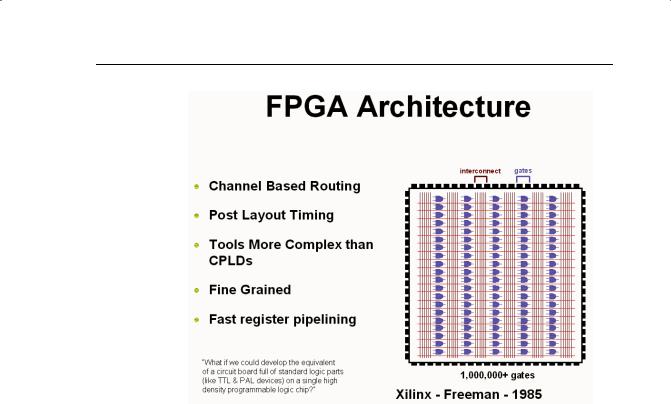

Field Programmable Gate Arrays (FPGAs)

In 1985, a company called Xilinx introduced a completely new idea: combine the user control and time to market of PLDs with the densities and cost benefits of gate arrays.

Customers liked it – and the FPGA was born. Today Xilinx is still the num- ber-one FPGA vendor in the world.

An FPGA is a regular structure of logic cells (or modules) and interconnect, which is under your complete control. This means that you can design, program, and make changes to your circuit whenever you wish.

With FPGAs now exceeding the 10 million gate limit (the Xilinx Virtex™-II FPGA is the current record holder), you can really dream big.

Xilinx • 6

INTRODUCTION

FIGURE 1-4: FPGA ARCHITECTURE

With the introduction of the Spartan series of FPGAs, Xilinx can now compete with gate arrays on all aspects – price, gate, and I/O count, as well as performance and cost.

The Spartan-IIE FPGA provides as many as 300,000 gates at a price point that enables application specific standard product (ASSP) replacement. For example, a Reed Solomon IP core implemented in a Spartan-II XC2S100 FPGA has an effective cost of $9.95, whereas the equivalent ASSP would cost around $20.

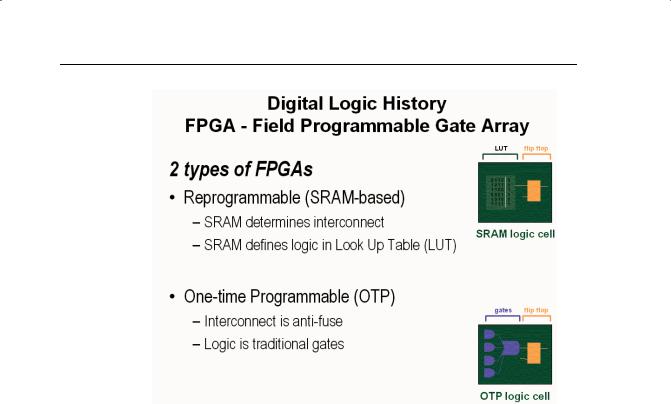

There are two basic types of FPGAs: SRAM-based reprogrammable and OTP. These two types of FPGAs differ in the implementation of the logic cell and the mechanism used to make connections in the device.

The dominant type of FPGA is SRAM-based and can be reprogrammed as often as you choose. In fact, an SRAM FPGA is reprogrammed every time it’s powered up, because the FPGA is really a fancy memory chip. That’s why you need a serial PROM or system memory with every SRAM FPGA.

Xilinx • 7

PROGRAMMABLE LOGIC DESIGN: QUICK START HANDBOOK • CHAPTER 1

FIGURE 1-5: DIGITAL LOGIC HISTORY

In the SRAM logic cell, instead of conventional gates, an LUT determines the output based on the values of the inputs. (In the “SRAM logic cell” diagram above, six different combinations of the four inputs determine the values of the output.) SRAM bits are also used to make connections.

OTP FPGAs use anti-fuses (contrary to fuses, connections are made, not “blown,” during programming) to make permanent connections in the chip. Thus, OTP FPGAs do not require SPROM or other means to download the program to the FPGA.

However, every time you make a design change, you must throw away the chip! The OTP logic cell is very similar to PLDs, with dedicated gates and flipflops.

DESIGN INTEGRATION

The integration of 74 series standard logic into a low-cost CPLD is a very attractive proposition. Not only do you save PCB area and board layers – thus reducing your total system cost – but you only have to purchase and stock one generic part instead of as many as 20 pre-defined logic devices.

In production, the pick and place machine only has to place one part, therefore speeding up production. Less parts means higher quality and better FIT factor.

Xilinx • 8