- •Микропроцессорные средства автоматизации

- •Содержание

- •Глава 14. Применение микро-эвм в системах регулирования и управления 184

- •Введение

- •1. Основные определения и классификация микропроцессорных средств автоматизации

- •2. Дискретная автоматика

- •2.1. Формы представления информации

- •2.2. Способы представления дискретной информации

- •2.3. Системы счисления, используемые в вычислительной технике

- •2.3.1. Способы представлений информации для микропроцессора

- •2.4. Булевы функции

- •2.4.1. Система равносильных преобразований

- •2.5. Синтез систем дискретной автоматики

- •2.5.1. Синтез дискретных схем по таблицам состояний.

- •2.5.2. Синтез многотактных систем дискретной автоматики

- •3. Промышленные сети

- •3.1. Структура промышленных сетей

- •3.1.1. Топология промышленных сетей

- •3.2. Аппаратные интерфейсы пк

- •3.2.1. СтандартRs-232c

- •3.2.2. Последовательная шинаUsb

- •3.3. Универсальный асинхронный приемопередатчик

- •3.4. Физические интерфейсы

- •3.4.1. ИнтерфейсRs-485

- •3.4.1.1. Автоматический преобразователь интерфейсовUsb/rs-485 овен ас4

- •3.4.2. Интерфейс «Токовая петля»

- •3.4.2.1. Адаптер интерфейса овен ас 2

- •3.5. Протоколы промышленных сетей

- •3.5.1. ПротоколModbus

- •3.5.2.Hart-протокол

- •3.5.4. Сеть profibus

- •3.5.5. Описание шиныCan

- •2.8.1.1. Организация сети can

- •2.8.1.2. Физический уровень канала can.

- •2.8.1.3. Арбитраж шины can.

- •2.8.1.4. Структура формата передачи данных

- •2.8.1.1. Форматы кадра

- •Механизм обработки ошибок.

- •Адресация и протоколы высокого уровня

- •5.8. Универсальная сеть Foundation Fieldbus

- •5.9. Физическая среда передачи данных

- •3. Языки программирования логических контроллеров

- •3.1 Объекты адресации языков программирования плк

- •3.2 ЯзыкLadderDiagram(ld)

- •3.3 Язык Functional Block Diagrams (fbd)

- •3.4 ЯзыкInstructionList(il)

- •3.5. Язык структурированного текста

- •3.5.1. Применение управляющих структур Условное действиеIf...End_if

- •Условное итеративное действие while...End_while

- •Условное итеративное действиеRepeat...End_repeat

- •Повторяющееся действиеFor...End_for

- •Выход из цикла посредством инструкции exit

- •3.6. Язык последовательных функциональных схем

- •5.4. Пример

- •4. Элементы микропроцессорных устройств

- •4.1 Цифро-аналоговые преобразователи

- •4.1.1 Принципы построения основных узлов цап.

- •4.2 Аналого-цифровые преобразователи

- •4.2.1 Метод последовательного счета

- •4.2.2 Метод поразрядного кодирования

- •4.2.3 Метод считывания

- •5. Мини-контроллеры

- •5.1. Мини-контроллеры серииAlpha

- •5.2. Миниатюрные программируемые устройстваEasy

- •5.2.1. Управляющее релеEasy500

- •5.2.2. Управляющее реле Easy 700

- •5.2.3. Управляющее реле Easy 800

- •5.2.4. Модули расширенияEasy

- •5.2.5. Средства коммуникации устройств Easy

- •5.3. Интеллектуальные релеZelioLogic

- •5.3.1. Компактные и модульные интеллектуальные реле

- •5.3.2. Общие технические характеристики релеZelio Logic

- •5.3.3. ПреобразователиZelioAnalog

- •5.3.4. Средства коммуникации интеллектуальных релеZelio Logic

- •5.3.4.1. Коммуникационный модемный интерфейс

- •5.3.4.2. Протокол связиModbusslave

- •5.3.4.3. Протокол связиEthernetserver

- •5.3.5. Программное обеспечение интеллектуального реле

- •5.4. Универсальный логический модульLogo!

- •5.4.1. Типы базовых модулей logo!Basic

- •5.4.2. Модули расширения ввода/вывода сигналовLogo!

- •5.4.3. Коммуникационные модули logo!

- •5.4.4. ФункцииLogo!

- •5.4.4.1.6. Биты регистра сдвига

- •5.4.4.1.7. Клавиши управления курсором

- •5.4.4.1.8. Постоянные уровни

- •5.4.4.2. Группа базовых функций

- •5.4.4.3. Специальные функции

- •5.4.4.3.1. Список специальных функций

- •5.4.4.3.2. Примеры специальных функций

- •5.4.5. Объем памяти и размер коммутационной программы

- •6. Программируемы логические контроллеры

- •6.1. Программируемые контроллеры simatic s7-22x

- •6.1.1. Модули расширения вводов-выводов

- •6.1.2. Коммуникационные модули

- •6.1.3. Человеко-машинный интерфейс

- •6.2. Программируемый логический контроллер simatics7-224xp

- •6.2.1. Основы функционирования плк

- •6.2.1.1. Порядок чтения входов

- •6.2.1.2. Исполнение программы

- •6.2.1.3. Запись значений в выходы

- •6.2.2. Доступ к данным s7-200

- •6.2.3. Адресация встроенных входов/выходов и входов/выходов модулей расширения

- •6.2.4. Обмен данными в сети

- •6.3. Программируемые контроллеры simatic s7-300

- •6.3.1. Области применения

- •6.3.2. Состав

- •6.3.3. Сертификаты

- •6.4. Программируемые контроллеры simatic s7-400

- •Модификации контроллеров

- •6.4.1. Области применения

- •6.4.2. Состав

- •6.4.3. Сертификаты

- •6.6 Контроллер логический программируемый овен плк150

- •Глава 14. Применение микро-эвм в системах регулирования и управления

- •14.1. Управляющие эвм

- •14.2. Использование микро-эвм для оптимизации резки катаной заготовки ножницами

- •14.4. Система управления положением вторичного зеркала телескопа

- •14.5. Прямое цифровое регулирование

- •14.8. Микропроцессор как универсальный регулятор

- •14.9. Микропроцессор как основа нового поколения систем автоматизации

- •7 Системы диспетчерского управления и сбора данных

- •7.1 Scada-система InTouch ("Wonderware", сша)

- •7.2 Scada-система Trace Mode ("AdAstra Research Group", Россия)

- •7.3Scada-системаSimaticWinCc("Siemens", Германия)

- •7.4Scada-системы, встраиваемые в плк

- •9. Методика выбора по различных производителей

- •Список литературы

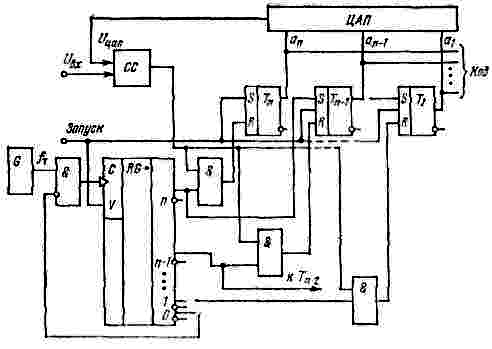

4.2.2 Метод поразрядного кодирования

Метод поразрядного кодирования (уравновешивания) предусматривает наличие нескольких эталонов, обычно пропорциональных по величине степеням числа 2, и сравнение этих эталонов с аналоговой величиной. Сравнение начинается с эталона старшего разряда. В зависимости от результата этого сравнения формируется значение старшего разряда выходного кода. Если эталон больше входной величины, то в старшем разряде ставится 0 и далее производится уравновешивание входной величины следующим по значению эталоном. Если эталон равен или меньше входной величины, то в старшем разряде выходного кода ставится 1 и в дальнейшем производится уравновешивание разности между входной величиной и первым эталоном.

Для построения преобразователей с более высоким быстродействием используется метод поразрядного кодирования. Схема одного из вариантов подобного преобразователя приведена на рис. 4.7.

Рис. 4.7. АЦП поразрядного кодирования

При подаче импульса запуска триггер

старшего разряда Тnустанавливается в состояние 1, а остальные

триггеры – в 0, одновременно записывается 1 в

старший разряд регистра сдвига. В первом

такте работы на компаратор подаютсяUвхиUэп, снимаемое

с выхода ЦАП и соответствующее 1 старшего

разряда. ЕслиUвх>Uэп, на выходе

СС сигнала не будет и в старшем разряде

(Tn) сохранится 1. ЕслиUвх<Uэп, то СС

выдает сигнал, который через компаратор

вернетТnв

состояние 0. Одновременно произойдет

сдвиг 1 в регистре в (n– 1) разряд, что обеспечит подачу

эталонного напряженияUэ(n–1)с ЦАП на СС. Далее процесс преобразования

идет аналогично. В результате преобразованияUвхуравновешивается суммой

эталонных напряжений, снимаемых с ЦАП:

– в 0, одновременно записывается 1 в

старший разряд регистра сдвига. В первом

такте работы на компаратор подаютсяUвхиUэп, снимаемое

с выхода ЦАП и соответствующее 1 старшего

разряда. ЕслиUвх>Uэп, на выходе

СС сигнала не будет и в старшем разряде

(Tn) сохранится 1. ЕслиUвх<Uэп, то СС

выдает сигнал, который через компаратор

вернетТnв

состояние 0. Одновременно произойдет

сдвиг 1 в регистре в (n– 1) разряд, что обеспечит подачу

эталонного напряженияUэ(n–1)с ЦАП на СС. Далее процесс преобразования

идет аналогично. В результате преобразованияUвхуравновешивается суммой

эталонных напряжений, снимаемых с ЦАП:

где ai– коэффициенты 1 и 0 в разрядах выходного кода, снимаемого с триггеровТn–Т1;Uэi– эталонное напряжение ЦАП, соответствующееi-разряду.

В рассмотренном АЦП время преобразования постоянно и определяется числом разрядов и тактовой частотой Tпр=n/fт. Погрешность преобразования зависит от ошибок ЦАП и чувствительности СС. Имеются более сложные модификации рассмотренного преобразователя, которые характеризуются повышенным быстродействием и точностью.

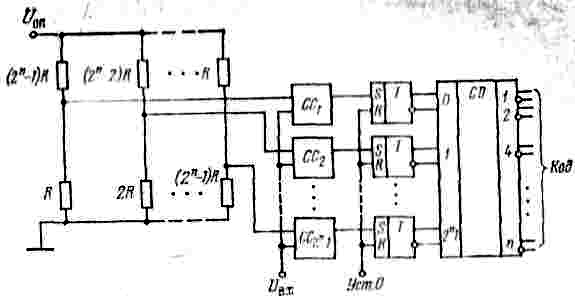

4.2.3 Метод считывания

Метод считывания (параллельного преобразования) подразумевает наличие 2n–1 эталонов приn-разрядном двоичном коде. Входная величина одновременно сравнивается со всеми эталонами. В результате преобразования получается параллельный код в виде сигналов на выходах 2n–1 схем сравнения (компараторов).

Наибольшим быстродействием обладают преобразователи, построенные по методу считывания. Пример такого преобразования показан на рис. 4.8.

Рис. 4.8. АЦП, построенный по методу считывания

В этом преобразователе 2n– 1 опорных напряжений формируются с помощью резистивного делителя. Каждое из опорных напряжений подается вместе сUвхна соответствующий компаратор. Срабатывают лишь те компараторы, у которыхUвх>Uопi. Результат сравнения через фиксирующие триггеры подается на шифратор, преобразующий его в код. Преобразование производится за два такта, время преобразования 10…100 нс. Недостаток этого преобразователя в большом числе компараторов, которое быстро возрастает с ростом числа разрядовn.