- •Техническая Электроника

- •Оглавление

- •Предисловие

- •Введение

- •Глава 1 пассивные компоненты электронных устройств

- •1.1. Резисторы

- •Числовые коэффициенты первых трех рядов

- •Допустимые отклонения сопротивлений

- •Основные параметры резисторов

- •1.1.1. Система условных обозначений и маркировка резисторов

- •Специальные резисторы

- •1.2. Конденсаторы

- •1.2.1. Система условных обозначений конденсаторов

- •1.2.2. Параметры постоянных конденсаторов

- •1.2.3. Конденсаторы переменной ёмкости

- •1.3. Катушки индуктивности

- •Параметры катушек индуктивности

- •Глава 2 полупроводниковые диоды

- •2.1. Физические основы полупроводниковых приборов

- •2.2. Примесные полупроводники

- •2.3. Электронно-дырочный переход

- •2.4. Физические процессы в p–n переходе

- •2.5. Контактная разность потенциалов

- •2.6. Прямое включение p–n перехода

- •2.7. Обратное включение p–n перехода

- •2.8. Вольт–амперная характеристика p–n перехода

- •2.9. Пробой p–n перехода

- •2.10. Емкостные свойства p–n перехода

- •2.11. Полупроводниковые диоды

- •Система обозначения полупроводниковых диодов

- •2.12. Выпрямительные диоды

- •Параметры выпрямительных диодов

- •2.13. Стабилитроны

- •Параметры стабилитрона

- •2.14. Варикапы

- •Параметры варикапов

- •2.15. Импульсные диоды

- •Параметры импульсных диодов

- •2.15.1. Диоды с накоплением заряда и диоды Шотки

- •2.16. Туннельные диоды

- •Параметры туннельных диодов

- •2.17. Обращенные диоды

- •Глава 3 биполярные транзисторы

- •3.1. Режимы работы биполярного транзистора

- •3.2. Принцип действия транзистора

- •3.3. Токи в транзисторе

- •3.4. Статические характеристики

- •3.4.1. Статические характеристики в схеме с об входные характеристики

- •Выходные характеристики

- •Характеристики прямой передачи

- •Характеристики обратной связи

- •3.5. Статические характеристики транзистора в схеме с оэ

- •3.6. Малосигнальные параметры Дифференциальные параметры транзистора

- •Система z–параметров.

- •Система y–параметров

- •Система h–параметров

- •Определение h–параметров по статическим характеристикам

- •3.7. Малосигнальная модель транзистора

- •3.8. Моделирование транзистора

- •3.9. Частотные свойства транзисторов

- •3.10. Параметры биполярных транзисторов

- •Глава 4 полевые транзисторы

- •4.1. Полевой транзистор с управляющим p-n переходом

- •Статические характеристики

- •4.2. Полевые транзисторы с изолированным затвором

- •4.2.2. Статические характеристики мдп-транзистора с

- •4.3. Полевые транзисторы со встроенным каналом

- •4.4. Cтатические характеристики транзистора со

- •4.5. Cпособы включения полевых транзисторов

- •4.6. Полевой транзистор как линейный четырехполюсник

- •4.7. Эквивалентная схема и частотные свойства

- •4.8. Основные параметры полевых транзисторов

- •Глава 5 полупроводниковые переключающие приборы

- •5.1. Диодный тиристор

- •5.2. Триодный тиристор

- •5.3. Симметричные тиристоры (симисторы)

- •5.4. Параметры тиристоров

- •Глава 6 электронно-лучевые приборы

- •6.1. Электростатическая система фокусировки луча

- •6.2. Электростатическая отклоняющая система

- •6.3. Трубки с магнитным управлением электронным лучом

- •6.4. Экраны электронно-лучевых трубок

- •6.5. Система обозначения электронно-лучевых трубок

- •6.6. Осциллографические трубки

- •6.7. Индикаторные трубки

- •6.8. Кинескопы

- •6.9. Цветные кинескопы

- •Глава 7 элементы и устройства оптоэлектроники

- •7.1. Источники оптического излучения

- •7.2. Характеристики светодиодов

- •7.3. Основные параметры светодиодов

- •7.4. Полупроводниковые приемники излучения

- •7.5. Фоторезисторы

- •7.6. Характеристики фоторезистора

- •7.7. Параметры фоторезистора

- •7.8. Фотодиоды

- •7.9. Характеристики и параметры фотодиода

- •7.10. Фотоэлементы

- •7.11. Фототранзисторы

- •7.12. Основные характеристики и параметры фототранзисторов

- •7.13. Фототиристоры

- •7.14. Оптопары

- •7.15. Входные и выходные параметры оптопар

- •7.16. Жидкокристаллические индикаторы

- •Параметры жки

- •Глава 8 элементы интегральных микросхем

- •8.1. Пассивные элементы интегральных микросхем

- •8.1.1. Резисторы

- •8.1.2. Конденсаторы

- •8.1.3. Пленочные конденсаторы

- •8.2. Биполярные транзисторы

- •8.3. Диоды полупроводниковых имс

- •8.4. Биполярные транзисторы с инжекционным питанием

- •8.5. Полупроводниковые приборы c зарядовой связью

- •Применение пзс

- •Параметры элементов пзс

- •Глава 9 основы цифровой техники

- •9.1. Электронные ключевые схемы

- •9.2. Ключи на биполярном транзисторе

- •9.3. Ключ с барьером Шотки

- •9.4. Ключи на мдп транзисторах

- •9.5. Ключ на комплементарных транзисторах

- •9.6. Алгебра логики и основные её законы

- •9.7. Логические элементы и их классификация

- •Классификация ис по функциональному назначению

- •Классификация ис по функциональному назначению

- •9.8. Базовые логические элементы цифровых

- •9.9. Диодно–транзисторная логика

- •9.10. Транзисторно–транзисторная логика (ттл)

- •9.11. Микросхемы ттл серий с открытым коллектором

- •9.12. Правила схемного включения элементов

- •9.13. Эмиттерно–связанная логика

- •9.14. Интегральная инжекционная логика (и2л)

- •9.15. Логические элементы на мдп-транзисторах

- •9.16. Параметры цифровых ис

- •9.17. Триггеры

- •Параметры триггеров

- •9.18. Мультивибраторы

- •9.18.1. Мультивибраторы на логических интегральных элементах

- •9.18.2. Автоколебательный мультивибратор с

- •9.18.3. Автоколебательные мультивибраторы с

- •9.18.4. Ждущие мультивибраторы

- •Глава 10 аналоговые устройства

- •10.1. Классификация аналоговых электронных устройств

- •10.2. Основные технические показатели и характеристики аналоговых устройств

- •10.3. Методы обеспечения режима работы транзистора в каскадах усиления

- •10.3.1. Схема с фиксированным током базы

- •10.3.2. Схема с фиксированным напряжением база–эмиттер

- •10.3.3. Схемы с температурной стабилизацией

- •10.4. Стабильность рабочей точки

- •10.5. Способы задания режима покоя в усилительных

- •10.6. Обратные связи в усилителях

- •10.6.1. Последовательная обратная связь по напряжению

- •10.6.2. Последовательная обратная связь по току

- •10.7. Режимы работы усилительных каскадов

- •10.8. Работа активных элементов с нагрузкой

- •10.9. Усилительный каскад с общим эмиттером

- •10.10. Усилительный каскад по схеме с общей базой

- •10.11. Усилительный каскад с общим коллектором

- •10.12. Усилительные каскады на полевых транзисторах

- •10.12.1. Усилительный каскад с ои

- •10.12.2. Усилительный каскад с общим стоком

- •10.13. Усилители постоянного тока

- •Глава 11 Дифференциальные и операционные усилители

- •11.1. Дифференциальные усилители

- •11.2. Операционные усилители

- •11.3. Параметры операционных усилителей

- •11.4. Амплитудно и фазочастотные характеристики оу

- •11.5. Устройство операционных усилителей

- •11.6. Оу общего применения

- •11.7. Инвертирующий усилитель

- •11.8. Неинвертирующий усилитель

- •11.9. Суммирующие схемы

- •11.9.1. Инвертирующий сумматор

- •11.9.2. Неинвертирующий сумматор

- •11.9.3. Интегрирующий усилитель

- •11.9.4. Дифференцирующий усилитель

- •11.9.5. Логарифмические схемы

- •11.9.6. Антилогарифмирующий усилитель

- •Глава 12 компараторы напряжения

- •Глава 13 Цифро-аналоговые преобразователи

- •13.1. Параметры цап

- •13.2. Устройство цап

- •Глава 14 Аналого-цифровые преобразователи

- •14.1. Параметры ацп

- •14.2. Классификация ацп

- •14.3. Ацп последовательного приближения

- •ЛитературА

9.15. Логические элементы на мдп-транзисторах

Полевые транзисторы являются наиболее перспективными полупроводниковыми приборами для создания логических и других интегральных схем большой и сверхбольшой степени интеграции. Практическое применение при разработке интегральных логических схем получили полевые транзисторы с МДП структурой и индуцированным каналом n– или p–типов. Наибольшее распространение получили две разновидности логических схем:

1. МДП-логика с нагрузочным транзистором.

2. Логика на комплементарных транзисторах.

Особенностью интегральных микросхем на МДП-транзисторах является возможность реализации любых логических функций с помощью только МДП-транзисторов.

Кроме того МДП-транзисторы имеют следующие достоинства:

– возможность использования транзистора в качестве нагрузки, что обеспечивает высокую однородность интегральных схем;

– высокая помехоустойчивость (2…6 В) по сравнению с 0,6 В для биполярных транзисторов;

– малая мощность рассеяния в статическом режиме, особенно при использовании в схеме транзисторов разного типа проводимости канала;

– используется один источник питания, что обеспечивает простоту схемы;

– устойчивость к нейтронной составляющей радиационного воздействия.

К недостаткам МДП-транзисторов следует отнести:

– большое пороговое напряжение;

– высокое напряжение питания;

– относительно невысокое быстродействие;

– малая крутизна, что снижает нагрузочную способность элементов по току и ухудшает отношение скорости переключения к мощности рассеяния.

Схемы на МДП-транзисторах с каналом p-типа имеют малую стоимость и более технологичны, имеют время прохождения сигнала в 8…10 раз меньше, чем схемы на транзисторах с каналом n–типа. По быстродействию схемы на МДП-транзисторах с каналом n–типа не уступают ТТЛ схемам, обеспечивая меньшую мощность рассеяния и более высокую плотность размещения компонентов, чем ТТЛ схемы.

Логические интегральные микросхемы на МДП-транзисторах бывают следующих типов: статические, динамические и квазистатические. Элементной базой для построения таких схем являются простейшие логические элементы, реализующие логические функции И–НЕ (схемы типа ЛА), ИЛИ–НЕ (схемы типа ЛЕ), И (схемы типа ЛИ), НЕ (схемы типа ЛН) и комбинированные (схемы типа ЛП, ЛС). Использование базовых элементов позволяет построить цифровое устройство с любым алгоритмом функционирования. В логических схемах получили распространение схемы статического типа.

Типовые схемы МДП-логики с нагрузочным транзистором, реализующие логические функции ИЛИ–НЕ и И–НЕ, показаны на рис. 9.25. В этих двух схемах транзисторы VТ1 и VТ2 выполняют роль ключевых элементов. Транзисторы VТ3 выполняют роль нагрузки. Ключевые транзисторы можно соединять последовательно (рис. 9.25,б) и параллельно (рис. 9.25,а). Параллельное соединение нескольких ключевых транзисторов ограничено снижением уровня логического нуля на выходе схемы за счет падения напряжения на нагрузке от суммарного тока утечки всех ключевых МДП–транзисторов. Поскольку ток утечки мал и составляет порядка 10-10 А, то число параллельно включенных транзисторов может достигать 10 и более.

При последовательном соединении в цепь между нагрузкой и землей включают несколько МДП-транзисторов. При этом исток нижнего МДП-транзистора подключается к земле, его сток – к истоку вышестоящего и т.д. Протекание тока через нагрузку к земле может происходить только, если открыты все ключевые транзисторы. Обычно число последовательно соединяемых транзисторов не более трех. Это связано с тем, что с увеличением числа последовательно соединенных транзисторов повышается уровень логического нуля на выходе схемы, ибо суммарное сопротивление открытых ключевых транзисторов возрастает. Последовательное включение требует применения МДП-транзисторов с более высокой крутизной характеристик, чем при параллельном включении. Последовательное включение транзисторов усложняет топологию и уменьшает степень интеграции, ухудшается быстродействие, но позволяет создавать логические микросхемы, обладающие большей гибкостью, чем микросхемы на биполярных транзисторах.

Реализация функции ИЛИ–НЕ осуществляется схемой, представленной на рис. 9.25,а, там же представлено условное обозначение и таблица истинности.

При подаче на один из входов положительного сигнала логической единицы соответствующий логический (ключевой) транзистор открывается. Если одновременно на все входы подается логическая единица, то все логические транзисторы открыты. Выходное напряжение схемы равно падению напряжения на открытых логических транзисторах и близко к нулю. Если на входах отсутствует сигнал, т.е. действует логический нуль, то логические транзисторы закрыты, выходное напряжение приближается по величине к источнику питания.

Последовательное включение транзисторов позволяет реализовать логическую операцию И–НЕ (рис. 9.25,б). При одновременной подаче положительных сигналов логической единицы на все входы, все МДП-транзисторы открываются, и на выходе схемы – логический нуль.

Достоинством логики этого типа является простота схем, применение транзисторов одного типа проводимости, высокое входное сопротивление порядка 1012 Ом, высокая нагрузочная способность (n = 10…20), технологичность в изготовлении. Недостатком логики данного типа является низкое быстродействие, обусловленное влиянием паразитной емкости.

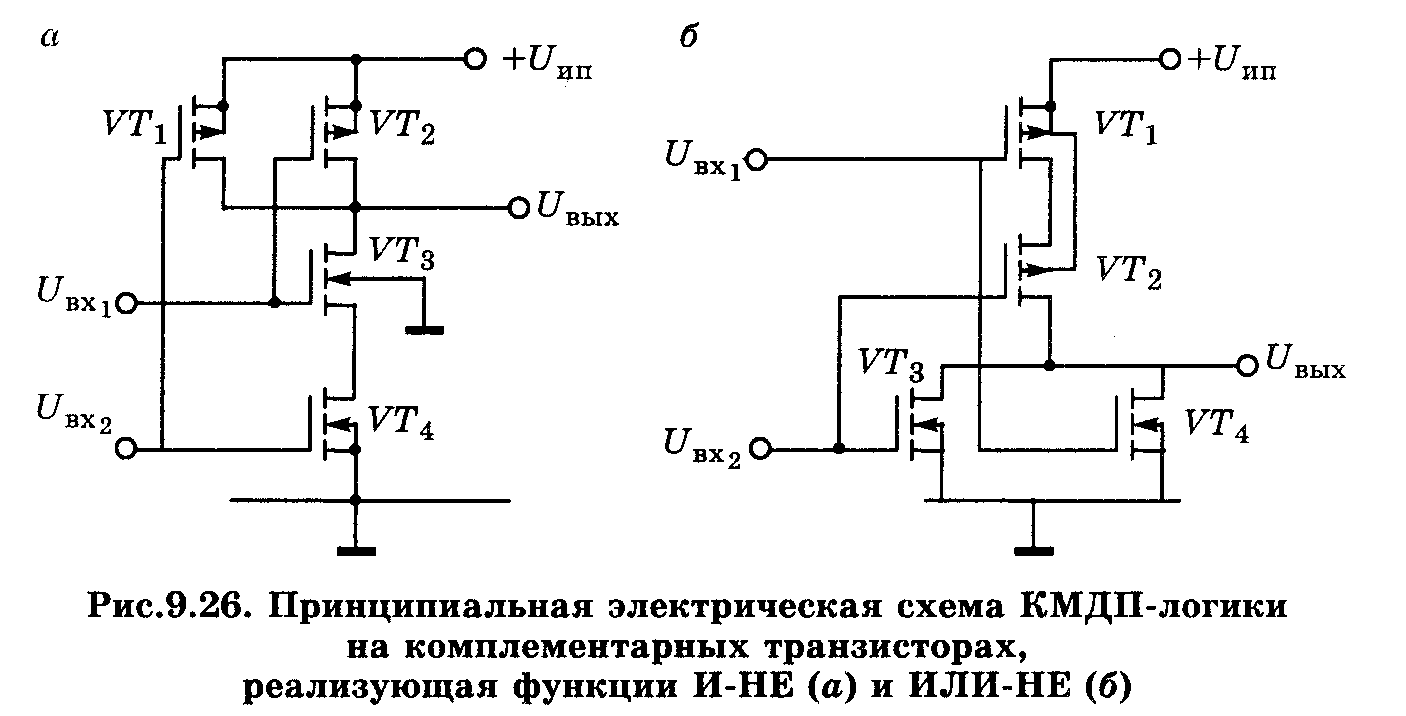

Наиболее перспективными являются логические схемы, выполненные на комплементарных МДП-транзисторах (КМДП). Комбинируя различные включения этих транзисторов можно получить заданную логическую функцию. Если транзистор с каналом n–типа непосредственно подключен к шине "земля", а транзистор с каналом p–типа – к источнику питания, то логическая схема работает в режиме положительной логики. На рис. 9.26,а и б представлены схемы КМДП-логики, реализующие логические операции И–НЕ и ИЛИ–НЕ.

Реализация логической функции И–НЕ осуществляется последовательным соединением МДП-транзисторов с каналом n–типа и параллельным соединением МДП-транзисторов с каналом p–типа, которые открыты при напряжениях затворов, близких к нулю. Предположим, что на вход 1 (рис. 9.26,а) подается сигнал логического нуля, транзистор VТ3 закрыт, а транзистор VТ2 открыт и выходное напряжение близко к напряжению источника питания. Если на все входы подается сигнал логической единицы, то транзисторы VТ3 и VТ4 открыты, а транзисторы VТ1 и VТ2 закрыты. Выходное напряжение стремится к потенциалу земли – (логический нуль).

Для построения схемы ИЛИ–НЕ требуется последовательное включение МДП-транзисторов с каналом p–типа и параллельное включение транзисторов с каналом n–типа (положительная логика) рис. 9.26,б.

Схема работает так же, как и предыдущая. Когда на всех входах действует высокий потенциал логической единицы, транзисторы VТ3 и VТ4 открываются, а p–канальные транзисторы закрываются. Выходное напряжение определяется падением напряжения на открытых транзисторах и соответствует логическому нулю. Если на один из входов подается сигнал логической единицы, то этот n–канальный транзистор открывается, и выходное напряжение определяется этим открытым транзистором.

Микросхемы на КМДП транзисторах потребляют очень малую мощность при сравнительно высоком быстродействии.

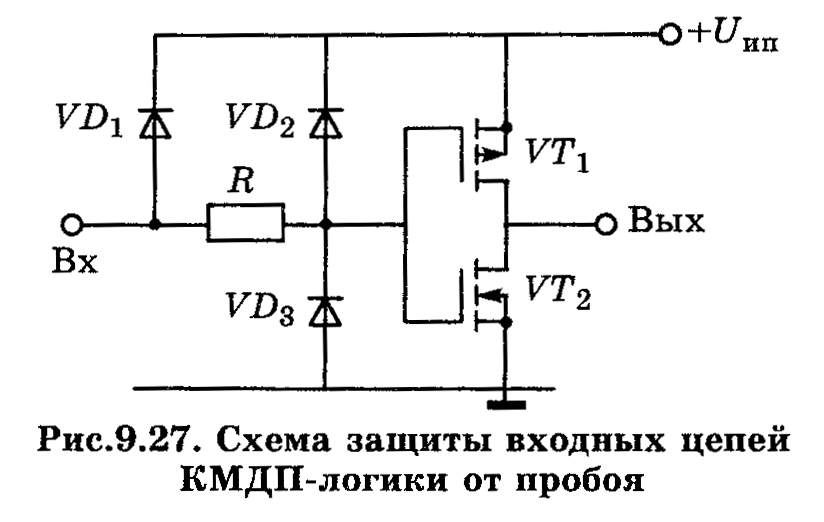

Затвор транзистора МДП и подложка, разделенные слоем диэлектрика, образуют конденсатор. Емкость конденсатора невелика, а сопротивление утечки очень велико, что способствует накоплению статических зарядов. Электрическая прочность тонкого слоя диэлектрика составляет порядка 150…200 В. Статический заряд малой энергии, попав на затвор, может произвести пробой диэлектрика. Для защиты транзистора от пробоя каждый вход современных микросхем КМДП-логики снабжается защитной цепью (рис. 9.27).

П одложки

каждого из транзисторов соединены с их

истоками, что предотвращает открывание

p–n переходов.

Затворы в обоих транзисторах объединены,

и на них подается входной сигнал.

Особенностью схемы защиты является

наличие защитных VD1–VD3

диодов, шунтирующих затворы входных

транзисторов и препятствующих пробою

диэлектрика под затвором от действия

электростатического заряда. Защитные

диоды смещаются в обратном направлении.

Резистор R1

(0,2…2 кОм) совместно с барьерными

емкостями диодов VD2

и VDЗ

образуют интегрирующую цепь, это

уменьшает скорость нарастания напряжения

на затворе, при котором диоды VD2,

VD3

успевают открыться.

одложки

каждого из транзисторов соединены с их

истоками, что предотвращает открывание

p–n переходов.

Затворы в обоих транзисторах объединены,

и на них подается входной сигнал.

Особенностью схемы защиты является

наличие защитных VD1–VD3

диодов, шунтирующих затворы входных

транзисторов и препятствующих пробою

диэлектрика под затвором от действия

электростатического заряда. Защитные

диоды смещаются в обратном направлении.

Резистор R1

(0,2…2 кОм) совместно с барьерными

емкостями диодов VD2

и VDЗ

образуют интегрирующую цепь, это

уменьшает скорость нарастания напряжения

на затворе, при котором диоды VD2,

VD3

успевают открыться.

Если входное напряжение Uвх подается от источника с малым внутренним сопротивлением и амплитудой больше Uип, то через VD1 будет протекать большой прямой ток. Поэтому при использовании таких схем рекомендуется включать напряжение питания раньше входного сигнала, а при выключении – наоборот.

В тех узлах, где по необходимости на входы поступают напряжения Uвх>Uип, следует в цепь входа включать резисторы, ограничивающие входной ток на уровне 1…2 мА.

На неиспользованные входы КМДП-логики подают постоянный потенциал (+Uип или 0 в зависимости от функции элемента) или объединяют их с другими, задействованными входами.