- •Техническая Электроника

- •Оглавление

- •Предисловие

- •Введение

- •Глава 1 пассивные компоненты электронных устройств

- •1.1. Резисторы

- •Числовые коэффициенты первых трех рядов

- •Допустимые отклонения сопротивлений

- •Основные параметры резисторов

- •1.1.1. Система условных обозначений и маркировка резисторов

- •Специальные резисторы

- •1.2. Конденсаторы

- •1.2.1. Система условных обозначений конденсаторов

- •1.2.2. Параметры постоянных конденсаторов

- •1.2.3. Конденсаторы переменной ёмкости

- •1.3. Катушки индуктивности

- •Параметры катушек индуктивности

- •Глава 2 полупроводниковые диоды

- •2.1. Физические основы полупроводниковых приборов

- •2.2. Примесные полупроводники

- •2.3. Электронно-дырочный переход

- •2.4. Физические процессы в p–n переходе

- •2.5. Контактная разность потенциалов

- •2.6. Прямое включение p–n перехода

- •2.7. Обратное включение p–n перехода

- •2.8. Вольт–амперная характеристика p–n перехода

- •2.9. Пробой p–n перехода

- •2.10. Емкостные свойства p–n перехода

- •2.11. Полупроводниковые диоды

- •Система обозначения полупроводниковых диодов

- •2.12. Выпрямительные диоды

- •Параметры выпрямительных диодов

- •2.13. Стабилитроны

- •Параметры стабилитрона

- •2.14. Варикапы

- •Параметры варикапов

- •2.15. Импульсные диоды

- •Параметры импульсных диодов

- •2.15.1. Диоды с накоплением заряда и диоды Шотки

- •2.16. Туннельные диоды

- •Параметры туннельных диодов

- •2.17. Обращенные диоды

- •Глава 3 биполярные транзисторы

- •3.1. Режимы работы биполярного транзистора

- •3.2. Принцип действия транзистора

- •3.3. Токи в транзисторе

- •3.4. Статические характеристики

- •3.4.1. Статические характеристики в схеме с об входные характеристики

- •Выходные характеристики

- •Характеристики прямой передачи

- •Характеристики обратной связи

- •3.5. Статические характеристики транзистора в схеме с оэ

- •3.6. Малосигнальные параметры Дифференциальные параметры транзистора

- •Система z–параметров.

- •Система y–параметров

- •Система h–параметров

- •Определение h–параметров по статическим характеристикам

- •3.7. Малосигнальная модель транзистора

- •3.8. Моделирование транзистора

- •3.9. Частотные свойства транзисторов

- •3.10. Параметры биполярных транзисторов

- •Глава 4 полевые транзисторы

- •4.1. Полевой транзистор с управляющим p-n переходом

- •Статические характеристики

- •4.2. Полевые транзисторы с изолированным затвором

- •4.2.2. Статические характеристики мдп-транзистора с

- •4.3. Полевые транзисторы со встроенным каналом

- •4.4. Cтатические характеристики транзистора со

- •4.5. Cпособы включения полевых транзисторов

- •4.6. Полевой транзистор как линейный четырехполюсник

- •4.7. Эквивалентная схема и частотные свойства

- •4.8. Основные параметры полевых транзисторов

- •Глава 5 полупроводниковые переключающие приборы

- •5.1. Диодный тиристор

- •5.2. Триодный тиристор

- •5.3. Симметричные тиристоры (симисторы)

- •5.4. Параметры тиристоров

- •Глава 6 электронно-лучевые приборы

- •6.1. Электростатическая система фокусировки луча

- •6.2. Электростатическая отклоняющая система

- •6.3. Трубки с магнитным управлением электронным лучом

- •6.4. Экраны электронно-лучевых трубок

- •6.5. Система обозначения электронно-лучевых трубок

- •6.6. Осциллографические трубки

- •6.7. Индикаторные трубки

- •6.8. Кинескопы

- •6.9. Цветные кинескопы

- •Глава 7 элементы и устройства оптоэлектроники

- •7.1. Источники оптического излучения

- •7.2. Характеристики светодиодов

- •7.3. Основные параметры светодиодов

- •7.4. Полупроводниковые приемники излучения

- •7.5. Фоторезисторы

- •7.6. Характеристики фоторезистора

- •7.7. Параметры фоторезистора

- •7.8. Фотодиоды

- •7.9. Характеристики и параметры фотодиода

- •7.10. Фотоэлементы

- •7.11. Фототранзисторы

- •7.12. Основные характеристики и параметры фототранзисторов

- •7.13. Фототиристоры

- •7.14. Оптопары

- •7.15. Входные и выходные параметры оптопар

- •7.16. Жидкокристаллические индикаторы

- •Параметры жки

- •Глава 8 элементы интегральных микросхем

- •8.1. Пассивные элементы интегральных микросхем

- •8.1.1. Резисторы

- •8.1.2. Конденсаторы

- •8.1.3. Пленочные конденсаторы

- •8.2. Биполярные транзисторы

- •8.3. Диоды полупроводниковых имс

- •8.4. Биполярные транзисторы с инжекционным питанием

- •8.5. Полупроводниковые приборы c зарядовой связью

- •Применение пзс

- •Параметры элементов пзс

- •Глава 9 основы цифровой техники

- •9.1. Электронные ключевые схемы

- •9.2. Ключи на биполярном транзисторе

- •9.3. Ключ с барьером Шотки

- •9.4. Ключи на мдп транзисторах

- •9.5. Ключ на комплементарных транзисторах

- •9.6. Алгебра логики и основные её законы

- •9.7. Логические элементы и их классификация

- •Классификация ис по функциональному назначению

- •Классификация ис по функциональному назначению

- •9.8. Базовые логические элементы цифровых

- •9.9. Диодно–транзисторная логика

- •9.10. Транзисторно–транзисторная логика (ттл)

- •9.11. Микросхемы ттл серий с открытым коллектором

- •9.12. Правила схемного включения элементов

- •9.13. Эмиттерно–связанная логика

- •9.14. Интегральная инжекционная логика (и2л)

- •9.15. Логические элементы на мдп-транзисторах

- •9.16. Параметры цифровых ис

- •9.17. Триггеры

- •Параметры триггеров

- •9.18. Мультивибраторы

- •9.18.1. Мультивибраторы на логических интегральных элементах

- •9.18.2. Автоколебательный мультивибратор с

- •9.18.3. Автоколебательные мультивибраторы с

- •9.18.4. Ждущие мультивибраторы

- •Глава 10 аналоговые устройства

- •10.1. Классификация аналоговых электронных устройств

- •10.2. Основные технические показатели и характеристики аналоговых устройств

- •10.3. Методы обеспечения режима работы транзистора в каскадах усиления

- •10.3.1. Схема с фиксированным током базы

- •10.3.2. Схема с фиксированным напряжением база–эмиттер

- •10.3.3. Схемы с температурной стабилизацией

- •10.4. Стабильность рабочей точки

- •10.5. Способы задания режима покоя в усилительных

- •10.6. Обратные связи в усилителях

- •10.6.1. Последовательная обратная связь по напряжению

- •10.6.2. Последовательная обратная связь по току

- •10.7. Режимы работы усилительных каскадов

- •10.8. Работа активных элементов с нагрузкой

- •10.9. Усилительный каскад с общим эмиттером

- •10.10. Усилительный каскад по схеме с общей базой

- •10.11. Усилительный каскад с общим коллектором

- •10.12. Усилительные каскады на полевых транзисторах

- •10.12.1. Усилительный каскад с ои

- •10.12.2. Усилительный каскад с общим стоком

- •10.13. Усилители постоянного тока

- •Глава 11 Дифференциальные и операционные усилители

- •11.1. Дифференциальные усилители

- •11.2. Операционные усилители

- •11.3. Параметры операционных усилителей

- •11.4. Амплитудно и фазочастотные характеристики оу

- •11.5. Устройство операционных усилителей

- •11.6. Оу общего применения

- •11.7. Инвертирующий усилитель

- •11.8. Неинвертирующий усилитель

- •11.9. Суммирующие схемы

- •11.9.1. Инвертирующий сумматор

- •11.9.2. Неинвертирующий сумматор

- •11.9.3. Интегрирующий усилитель

- •11.9.4. Дифференцирующий усилитель

- •11.9.5. Логарифмические схемы

- •11.9.6. Антилогарифмирующий усилитель

- •Глава 12 компараторы напряжения

- •Глава 13 Цифро-аналоговые преобразователи

- •13.1. Параметры цап

- •13.2. Устройство цап

- •Глава 14 Аналого-цифровые преобразователи

- •14.1. Параметры ацп

- •14.2. Классификация ацп

- •14.3. Ацп последовательного приближения

- •ЛитературА

9.13. Эмиттерно–связанная логика

Цифровые микросхемы эмиттерно–связанной логики составляют схемы на переключателях тока с объединенными эмиттерами, обладающие по сравнению с другими типами цифровых схем наибольшим быстродействием и большой потребляемой мощностью.

Большое быстродействие ЭСЛ логики обеспечивается:

– за счет работы транзисторов в ненасыщенном (линейном) режиме;

– за счет применения на выходах схемы эмиттерных повторителей, ускоряющих процесс заряда и разряда нагрузочных емкостей;

– за счет ограничения перепада выходного напряжения, что приводит к снижению статической помехоустойчивости.

Наибольшее распространение получили ЭСЛ серии 100, 500, К500, 700, К1500, обеспечивающие выполнение любых арифметических и логических операций.

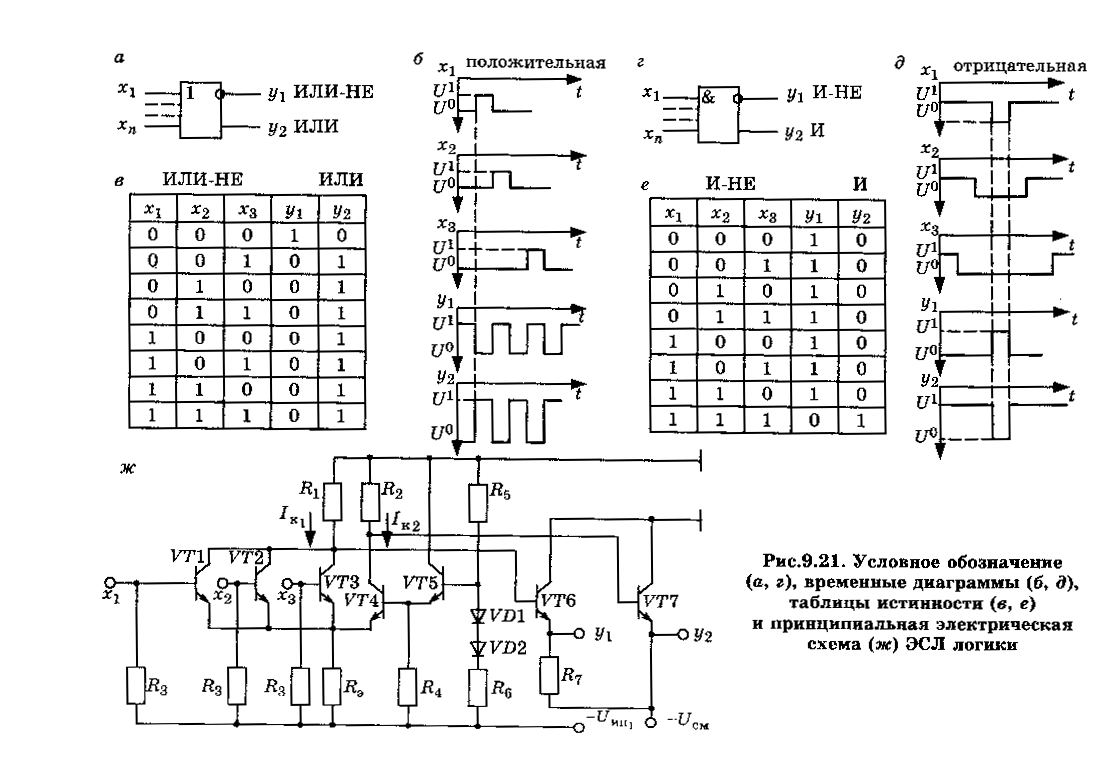

На рис. 9.21 представлены: условное графическое обозначение базового элемента, временные диаграммы, поясняющие работу элемента, таблица истинности и принципиальная электрическая схема ЭСЛ-логики. В зависимости от способа кодирования входной информации ("1" и "0") одна и та же схема (рис. 9.21,ж) может реализовать либо функции ИЛИ–НЕ, ИЛИ для положительной логики, либо функции И–НЕ, И для отрицательной логики. Для положительной логики "1" и "0" представляются напряжениями U0 = –1,45…–1,9 В; U1= –0,7…–0,95 В, а для отрицательной логики –напряжениями U1= –0,7…–0,95 В; U0= –1,45…–1,9 В.

В схемах ЭСЛ серий эмиттеры транзисторов токового переключателя через резистор Rэ подключаются к отрицательной шине источника напряжения Uип= –5,25 % В; коллекторные цепи заземляются. Такое включение обеспечивает меньшую зависимость выходного напряжения от наводок по цепи питания и лучшую помехозащищенность. Для повышения нагрузочной способности и расширения функциональных возможностей на выходах токового переключателя (VТЗ, VT4) включены транзисторы VТ6, VТ7, предназначенные для использования в качестве выходных эмиттерных повторителей с резисторами в цепи эмиттеров порядка 240…50 Ом. Для уменьшения потребляемой мощности при малых сопротивлениях нагрузок используют второй источник питания – Uсм. Для исключения влияния на логическую часть схемы импульсных помех, возникающих в коллекторных цепях эмиттерных повторителей в момент переключения схемы при работе на низкоомную нагрузку, используются две шины земля. Кроме того, выходные эмиттерные повторители смещают уровни сигналов по напряжению и обеспечивают совместимость ЭСЛ элементов по входу и выходу.

На транзисторах VТ1–VТ4 собран токовый переключатель, содержащий две ветви, работающие в режиме ключа и связанные эмиттерами через резистор Rэ. Транзисторы VТ1–VТЗ первой ветви и транзистор VТ4 второй ветви работают в активной области и не входят в режим насыщения. Для создания опорного напряжения Uбэ транзистора VT4 используется температурно-компенcирующая цепь (транзистор VТ5, диоды VD1, VD2 и резисторы R5, R6).

Рассмотрим

принцип работы базового логического

элемента для положительной логики. Если

на все логические входы подается

напряжение низкого уровня, соответствующее

логическому нулю, то транзисторы VТ1–VТ3

закрываются, а транзистор VТ4

открывается, так как напряжение на его

базе становится выше, чем на базах

входных транзисторов. Через открытый

транзистор протекает ток

![]() ,

значение которого задается резистором

Rэ,

и создает падение напряжения на резисторе

R2.

Потенциал коллектора транзистора VТ4

при этом понижается и подается на вход

эмиттерного повторителя, собранного

на транзисторе VТ7.

На выходе эмиттерного повторителя

получается низкий уровень напряжения,

соответствующий логическому нулю.

,

значение которого задается резистором

Rэ,

и создает падение напряжения на резисторе

R2.

Потенциал коллектора транзистора VТ4

при этом понижается и подается на вход

эмиттерного повторителя, собранного

на транзисторе VТ7.

На выходе эмиттерного повторителя

получается низкий уровень напряжения,

соответствующий логическому нулю.

В

это же время через резистор R1

левой ветви токового ключа протекает

небольшой обратный ток

![]() .

Потенциал коллектора транзистора VТ3

повышается и поступает на базу эмиттерного

повторителя транзистора VТ6.

На выходе транзистора VT6

имеем большой потенциал, логическую

единицу, при этом выполняется логическая

операция ИЛИ–НЕ.

.

Потенциал коллектора транзистора VТ3

повышается и поступает на базу эмиттерного

повторителя транзистора VТ6.

На выходе транзистора VT6

имеем большой потенциал, логическую

единицу, при этом выполняется логическая

операция ИЛИ–НЕ.

Предположим,

что на один из входов (вход 1) подается

напряжение логической единицы, а на

остальных входах действует логический

нуль. Под действием входного сигнала

транзистор VТ1

отрывается, через коллекторную и

эмиттерную цепь протекают большие токи

и Iэ.

Ток Iэ

создает падение напряжения на сопротивлении

резистора Rэ,

которое резко уменьшает напряжение

![]() ,

транзистор VТ4

закрывается. Перепады напряжений

коллекторных цепей транзисторов VТ1,

VТ4

подаются на входы соответствующих

эмиттерных повторителей. Таким образом

по выходу транзистора VТ6

выполняется логическая операция ИЛИ–НЕ,

а по выходу транзистора VТ7 –

логическая операция ИЛИ. Воздействие

входного сигнала приводит к переключению

тока эмиттера Iэ,

который проходит в зависимости от

амплитуды входного сигнала то через

левую, то через правую ветви, и при этом

на выходе создаются низкий и высокий

уровни напряжения одновременно. Поэтому

такую схему с объединенными эмиттерами

часто называют токовым ключом.

,

транзистор VТ4

закрывается. Перепады напряжений

коллекторных цепей транзисторов VТ1,

VТ4

подаются на входы соответствующих

эмиттерных повторителей. Таким образом

по выходу транзистора VТ6

выполняется логическая операция ИЛИ–НЕ,

а по выходу транзистора VТ7 –

логическая операция ИЛИ. Воздействие

входного сигнала приводит к переключению

тока эмиттера Iэ,

который проходит в зависимости от

амплитуды входного сигнала то через

левую, то через правую ветви, и при этом

на выходе создаются низкий и высокий

уровни напряжения одновременно. Поэтому

такую схему с объединенными эмиттерами

часто называют токовым ключом.

Резисторы в цепях базы токового ключа R3 служат для стекания обратного базового тока и надежного запирания незадействованных входных транзисторов. При их отсутствии самоотпирание незадействованных входных транзисторов будет мешать нормальной работе схемы, и потребуется внешнее принудительное подключение таких входов к источнику отрицательного напряжения.

Перспективными считаются ЭСЛ серии 500 и К1500. Серия К1500 относится к числу субнаносекундных и имеет время задержки менее 1 нс.

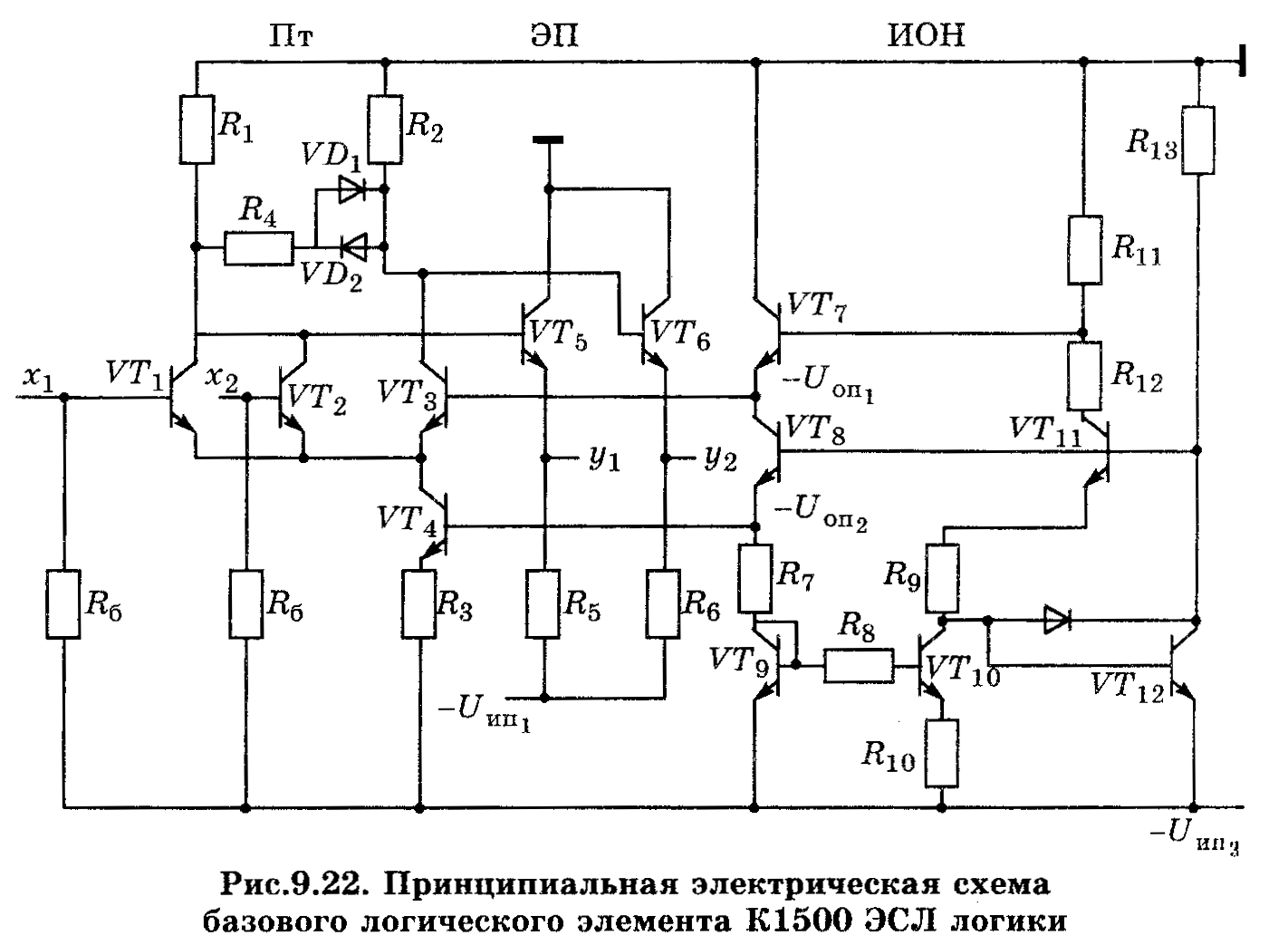

На рис. 9.22 приведена принципиальная электрическая схема базового логического элемента серии К1500, являющегося модернизацией базового логического элемента серии 500. Элемент реализует функции 2И/2И–НЕ, И для отрицательной логики.

Логический

элемент состоит из трех частей: токового

переключателя (ТП), эмиттерных повторителей

(ЭП), источника опорного напряжения

(ИОН). Назначение и функции указанных

частей соответствуют назначению и

функциям аналогичных цепей рассмотренного

базового логического элемента ЭСЛ

серий. В микросхеме К1500 используется

более стабильный генератор тока на

транзисторе VТ4

и резисторе R3,

термостабилизирующая цепочка на диодах

VD1,

VD2,

резисторе R4,

между коллекторами транзисторов

переключателя тока, усовершенствованный

источник опорного напряжения, раздельные

источники питания

![]() (для ЭП),

(для ЭП),

![]() (для ПТ и ИОН).

(для ПТ и ИОН).

Все это позволило стабилизировать статические и динамические параметры схемы:

– при

изменении напряжения питания

![]() в диапазоне –5,7…–4,2 В;

в диапазоне –5,7…–4,2 В;

– при изменении температуры на основании корпуса в пределах +1…+85 °С;

– увеличить помехозащищенность схемы по цепи питания.

Недостатком данной схемы является большая потребляемая мощность Pп ср = 50 мВт.

Интегральные схемы на эмиттерно–связанной логике используются в качестве элементной базы быстродействующих систем связи, вычислительной техники и радиоэлектронной аппаратуры. Они обладают следующими достоинствами:

1. Высокая помехоустойчивость.

2. Высокое быстродействие при средней потребляемой мощности и сверхвысокое быстродействие при большой потребляемой мощности.

3. Высокая стабильность динамических параметров при изменении рабочей температуры и напряжения питания.

4. Высокий коэффициент разветвления (высокая нагрузочная способность).

5. Возможность работы на низкоомные согласованные линии связи и нагрузки.

6. Малая мощность переключения и независимость тока потребления от частоты переключения.

7. Использование биполярной технологии изготовления.