- •Техническая Электроника

- •Оглавление

- •Предисловие

- •Введение

- •Глава 1 пассивные компоненты электронных устройств

- •1.1. Резисторы

- •Числовые коэффициенты первых трех рядов

- •Допустимые отклонения сопротивлений

- •Основные параметры резисторов

- •1.1.1. Система условных обозначений и маркировка резисторов

- •Специальные резисторы

- •1.2. Конденсаторы

- •1.2.1. Система условных обозначений конденсаторов

- •1.2.2. Параметры постоянных конденсаторов

- •1.2.3. Конденсаторы переменной ёмкости

- •1.3. Катушки индуктивности

- •Параметры катушек индуктивности

- •Глава 2 полупроводниковые диоды

- •2.1. Физические основы полупроводниковых приборов

- •2.2. Примесные полупроводники

- •2.3. Электронно-дырочный переход

- •2.4. Физические процессы в p–n переходе

- •2.5. Контактная разность потенциалов

- •2.6. Прямое включение p–n перехода

- •2.7. Обратное включение p–n перехода

- •2.8. Вольт–амперная характеристика p–n перехода

- •2.9. Пробой p–n перехода

- •2.10. Емкостные свойства p–n перехода

- •2.11. Полупроводниковые диоды

- •Система обозначения полупроводниковых диодов

- •2.12. Выпрямительные диоды

- •Параметры выпрямительных диодов

- •2.13. Стабилитроны

- •Параметры стабилитрона

- •2.14. Варикапы

- •Параметры варикапов

- •2.15. Импульсные диоды

- •Параметры импульсных диодов

- •2.15.1. Диоды с накоплением заряда и диоды Шотки

- •2.16. Туннельные диоды

- •Параметры туннельных диодов

- •2.17. Обращенные диоды

- •Глава 3 биполярные транзисторы

- •3.1. Режимы работы биполярного транзистора

- •3.2. Принцип действия транзистора

- •3.3. Токи в транзисторе

- •3.4. Статические характеристики

- •3.4.1. Статические характеристики в схеме с об входные характеристики

- •Выходные характеристики

- •Характеристики прямой передачи

- •Характеристики обратной связи

- •3.5. Статические характеристики транзистора в схеме с оэ

- •3.6. Малосигнальные параметры Дифференциальные параметры транзистора

- •Система z–параметров.

- •Система y–параметров

- •Система h–параметров

- •Определение h–параметров по статическим характеристикам

- •3.7. Малосигнальная модель транзистора

- •3.8. Моделирование транзистора

- •3.9. Частотные свойства транзисторов

- •3.10. Параметры биполярных транзисторов

- •Глава 4 полевые транзисторы

- •4.1. Полевой транзистор с управляющим p-n переходом

- •Статические характеристики

- •4.2. Полевые транзисторы с изолированным затвором

- •4.2.2. Статические характеристики мдп-транзистора с

- •4.3. Полевые транзисторы со встроенным каналом

- •4.4. Cтатические характеристики транзистора со

- •4.5. Cпособы включения полевых транзисторов

- •4.6. Полевой транзистор как линейный четырехполюсник

- •4.7. Эквивалентная схема и частотные свойства

- •4.8. Основные параметры полевых транзисторов

- •Глава 5 полупроводниковые переключающие приборы

- •5.1. Диодный тиристор

- •5.2. Триодный тиристор

- •5.3. Симметричные тиристоры (симисторы)

- •5.4. Параметры тиристоров

- •Глава 6 электронно-лучевые приборы

- •6.1. Электростатическая система фокусировки луча

- •6.2. Электростатическая отклоняющая система

- •6.3. Трубки с магнитным управлением электронным лучом

- •6.4. Экраны электронно-лучевых трубок

- •6.5. Система обозначения электронно-лучевых трубок

- •6.6. Осциллографические трубки

- •6.7. Индикаторные трубки

- •6.8. Кинескопы

- •6.9. Цветные кинескопы

- •Глава 7 элементы и устройства оптоэлектроники

- •7.1. Источники оптического излучения

- •7.2. Характеристики светодиодов

- •7.3. Основные параметры светодиодов

- •7.4. Полупроводниковые приемники излучения

- •7.5. Фоторезисторы

- •7.6. Характеристики фоторезистора

- •7.7. Параметры фоторезистора

- •7.8. Фотодиоды

- •7.9. Характеристики и параметры фотодиода

- •7.10. Фотоэлементы

- •7.11. Фототранзисторы

- •7.12. Основные характеристики и параметры фототранзисторов

- •7.13. Фототиристоры

- •7.14. Оптопары

- •7.15. Входные и выходные параметры оптопар

- •7.16. Жидкокристаллические индикаторы

- •Параметры жки

- •Глава 8 элементы интегральных микросхем

- •8.1. Пассивные элементы интегральных микросхем

- •8.1.1. Резисторы

- •8.1.2. Конденсаторы

- •8.1.3. Пленочные конденсаторы

- •8.2. Биполярные транзисторы

- •8.3. Диоды полупроводниковых имс

- •8.4. Биполярные транзисторы с инжекционным питанием

- •8.5. Полупроводниковые приборы c зарядовой связью

- •Применение пзс

- •Параметры элементов пзс

- •Глава 9 основы цифровой техники

- •9.1. Электронные ключевые схемы

- •9.2. Ключи на биполярном транзисторе

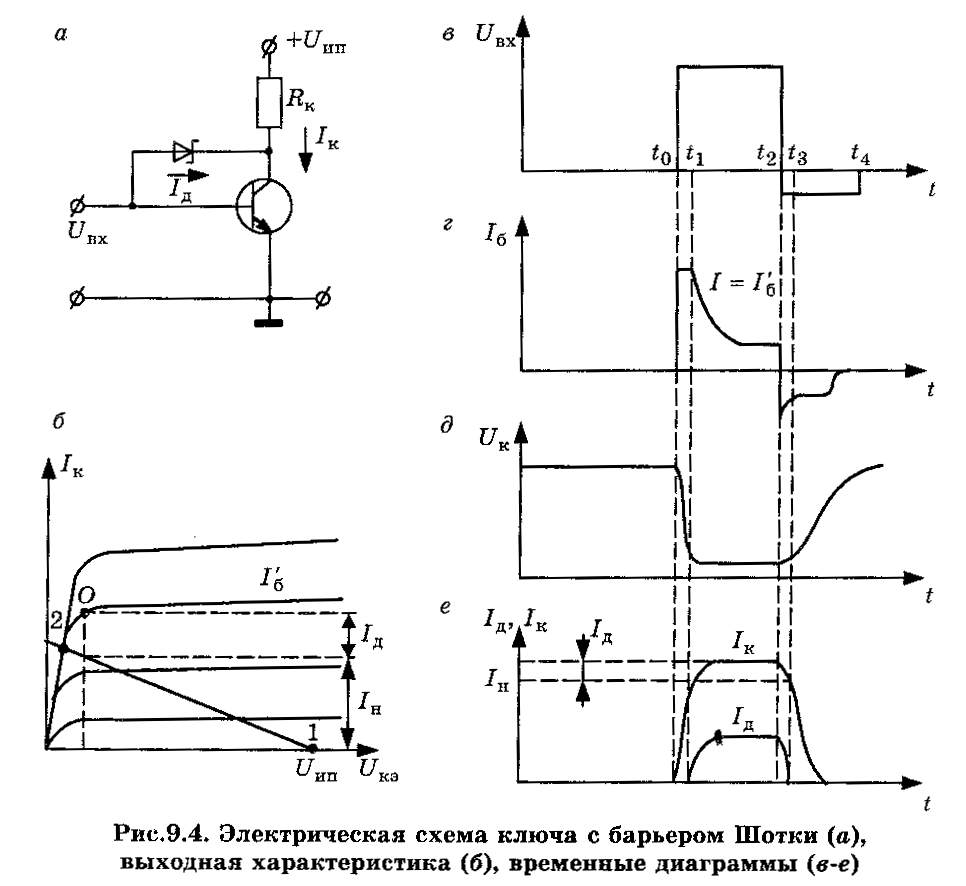

- •9.3. Ключ с барьером Шотки

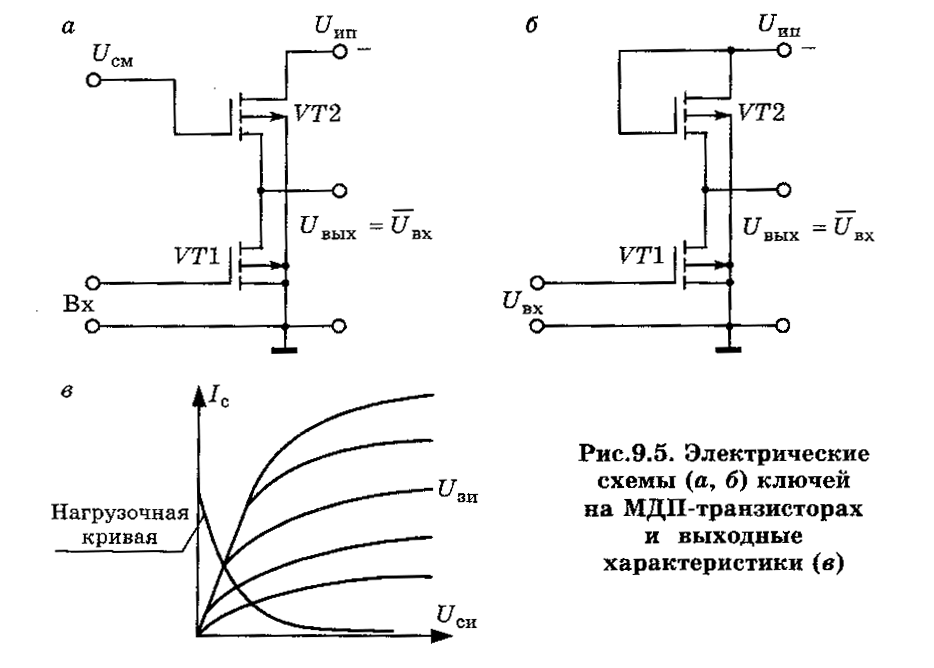

- •9.4. Ключи на мдп транзисторах

- •9.5. Ключ на комплементарных транзисторах

- •9.6. Алгебра логики и основные её законы

- •9.7. Логические элементы и их классификация

- •Классификация ис по функциональному назначению

- •Классификация ис по функциональному назначению

- •9.8. Базовые логические элементы цифровых

- •9.9. Диодно–транзисторная логика

- •9.10. Транзисторно–транзисторная логика (ттл)

- •9.11. Микросхемы ттл серий с открытым коллектором

- •9.12. Правила схемного включения элементов

- •9.13. Эмиттерно–связанная логика

- •9.14. Интегральная инжекционная логика (и2л)

- •9.15. Логические элементы на мдп-транзисторах

- •9.16. Параметры цифровых ис

- •9.17. Триггеры

- •Параметры триггеров

- •9.18. Мультивибраторы

- •9.18.1. Мультивибраторы на логических интегральных элементах

- •9.18.2. Автоколебательный мультивибратор с

- •9.18.3. Автоколебательные мультивибраторы с

- •9.18.4. Ждущие мультивибраторы

- •Глава 10 аналоговые устройства

- •10.1. Классификация аналоговых электронных устройств

- •10.2. Основные технические показатели и характеристики аналоговых устройств

- •10.3. Методы обеспечения режима работы транзистора в каскадах усиления

- •10.3.1. Схема с фиксированным током базы

- •10.3.2. Схема с фиксированным напряжением база–эмиттер

- •10.3.3. Схемы с температурной стабилизацией

- •10.4. Стабильность рабочей точки

- •10.5. Способы задания режима покоя в усилительных

- •10.6. Обратные связи в усилителях

- •10.6.1. Последовательная обратная связь по напряжению

- •10.6.2. Последовательная обратная связь по току

- •10.7. Режимы работы усилительных каскадов

- •10.8. Работа активных элементов с нагрузкой

- •10.9. Усилительный каскад с общим эмиттером

- •10.10. Усилительный каскад по схеме с общей базой

- •10.11. Усилительный каскад с общим коллектором

- •10.12. Усилительные каскады на полевых транзисторах

- •10.12.1. Усилительный каскад с ои

- •10.12.2. Усилительный каскад с общим стоком

- •10.13. Усилители постоянного тока

- •Глава 11 Дифференциальные и операционные усилители

- •11.1. Дифференциальные усилители

- •11.2. Операционные усилители

- •11.3. Параметры операционных усилителей

- •11.4. Амплитудно и фазочастотные характеристики оу

- •11.5. Устройство операционных усилителей

- •11.6. Оу общего применения

- •11.7. Инвертирующий усилитель

- •11.8. Неинвертирующий усилитель

- •11.9. Суммирующие схемы

- •11.9.1. Инвертирующий сумматор

- •11.9.2. Неинвертирующий сумматор

- •11.9.3. Интегрирующий усилитель

- •11.9.4. Дифференцирующий усилитель

- •11.9.5. Логарифмические схемы

- •11.9.6. Антилогарифмирующий усилитель

- •Глава 12 компараторы напряжения

- •Глава 13 Цифро-аналоговые преобразователи

- •13.1. Параметры цап

- •13.2. Устройство цап

- •Глава 14 Аналого-цифровые преобразователи

- •14.1. Параметры ацп

- •14.2. Классификация ацп

- •14.3. Ацп последовательного приближения

- •ЛитературА

9.3. Ключ с барьером Шотки

Для повышения быстродействия ключа необходимо уменьшить время рассасывания избыточных зарядов, т.е. транзистор должен работать на границе активного режима и режима насыщения. Для предотвращения насыщения транзистора в ключе используют нелинейную обратную связь, предложенную Б.Н. Кононовым в 1955 году. При микроэлектронном исполнении нелинейная обратная связь наиболее эффективна, если между коллектором и базой включается диод Шотки (рис. 9.4,а).

При отсутствии сигнала на входе схемы транзистор закрыт, закрыт и диод Шотки, выходное напряжение велико (точка 1 на рис. 9.4,6). При подаче на вход положительного сигнала транзистор открывается, и рабочая точка по нагрузочной прямой начинает перемещается в точку 2. Ток коллектора растет, а потенциал коллектора уменьшается, и в момент времени t1 открывается диод Шотки. После этого входной ток перераспределяется между базой транзистора и диодной цепью так, что рабочая точка перемещается в точку О, в которой Iк = Iд+Iн (рис. 9.4,в). Точка О располагается в непосредственной близости к границе насыщения в области линейного участка характеристик. При подаче запирающего сигнала на вход схемы начинается спад коллекторного тока. Задержка начала нарастания коллекторного напряжения (время t3) обусловлена временем, в течение которого ток диода уменьшается от начального значения Iд до нуля, и она составляет менее одной наносекунды. Спад коллекторного тока и нарастание коллекторного напряжения происходит как у обычного транзисторного ключа.

Наряду с высоким быстродействием транзисторные ключи с нелинейной обратной связью имеют следующие недостатки:

1. Относительно большее падение напряжения на открытом ключе (около 0,5 В).

2. Меньшая температурная стабильность.

3. Худшая помехоустойчивость, что объясняется более высоким входным сопротивлением в открытом состоянии.

9.4. Ключи на мдп транзисторах

МДП-транзисторы применяют при построении цифровых микросхем. Это обусловлено простотой их конструкции, малыми размерами и низкой потребляемой мощностью. Цифровые МДП микросхемы состоят только из МДП-транзисторов, функции пассивных элементов выполняют сами транзисторы. МДП микросхемы представляют собой схемы с непосредственными связями, поэтому в таких схемах отсутствуют конденсаторы связи. По принципу действия цифровые МДП микросхемы можно подразделить на статические и динамические. Логические микросхемы статического типа выполняются как на МДП-транзисторах с каналами одного типа проводимости, так и на комплементарных парах. Так называют пару транзисторов, имеющих примерно одинаковые значения основных параметров, но с полупроводниковыми структурами противоположного типа. В биполярной технологии – это транзисторы n–p–n и p–n–p, в полевой технологии ‑ транзисторы с n– и p–каналами. Такие МДП микросхемы называют комплементарными.

Базовым элементом логических МДП микросхем является инвентор (ключ). В качестве нагрузочного элемента в ключевой схеме используется линейный резистор или МДП-транзистор в качестве нелинейного резистора. Использование в качестве нагрузки нормально открытых МДП-транзисторов позволяет отказаться от применения высокоомных диффузионных резисторов, занимающих большую площадь на подложке. На рис. 9.5 приведены схемы инверторов на МДП-транзисторах с каналом p–типа.

Транзистор VT1, исток которого соединен с заземленной шиной питания, является ключевым (активным), а транзистор VТ2 ‑ нагрузочным, выполняющим роль резистора. Затвор нагрузочного транзистора подключается к источнику напряжения смещения Uсм (рис. 9.5,а), имеющему более высокий по абсолютному значению уровень напряжения, чем напряжение источника питания Uип, или непосредственно к источнику питания Uип (рис. 9.5,б). В ключе с источником смещения, нагрузочный транзистор VТ2 представляет собой квазилинейную нагрузку. Напряжение источника смещения такое, что он работает только в крутой области ВАХ. В ключе с одним источником питания нагрузочный транзистор используется в качестве нелинейной нагрузки и транзистор работает в пологой области ВАХ, где

![]() . (9.17)

. (9.17)

Ток, протекающий через нагрузочный транзистор, определяется из выражения

![]() , (9.18)

, (9.18)

где Sк, Sн – удельная крутизна ключевого и нагрузочного транзисторов.

На рис. 9.5,в приведены ВАХ ключа на МДП-транзисторе с транзистором в цепи нагрузки. Точка пересечения двух любых кривых дает совместное решение системы уравнений, описывающих состояние ключевого и нагрузочного транзисторов. А так как ток, протекающий в последовательно включенной цепи транзисторов одинаков, то работа транзистора в пологой области описывается следующим выражением

![]() . (9.19)

. (9.19)

В крутой области характеристик ключевого транзистора это уравнение имеет вид:

![]() .

(9.20)

.

(9.20)

Если напряжения Uвых и Uвх – Uзи пор пронормировать к разности Uип – Uзи пор, то получим

. (9.21)

. (9.21)

Выражение (9.21) позволяет получить выражение для величины остаточного напряжения на транзисторе

![]() . (9.22)

. (9.22)

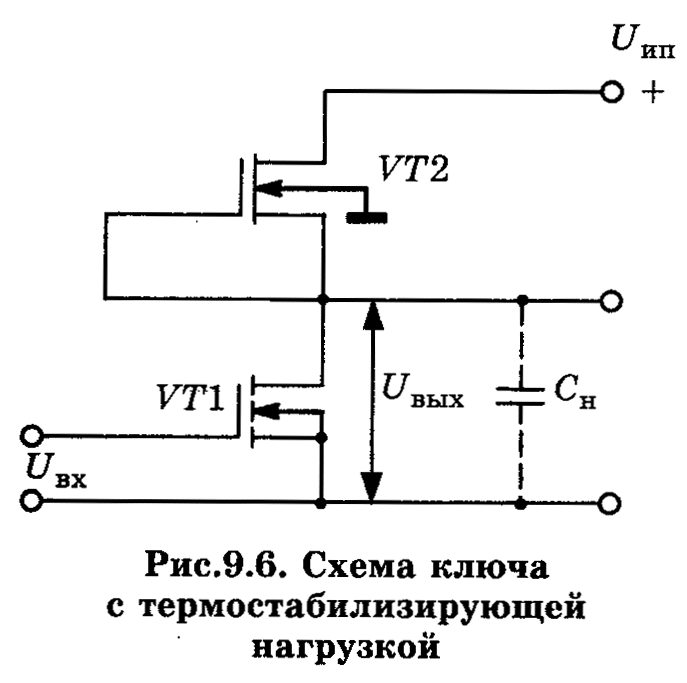

Для создания БИС и СБИС используют МДП-транзисторы с n–каналами. А ключи строят с токостабилизирующей нагрузкой (Д–нагрузкой) (рис. 9.6).

В

качестве нагрузки применяют МДП-транзистор

VT2

со встроенным каналом n–типа, у которого

затвор соединен с выходом схемы, а не с

источником питания. Нагрузочный

транзистор VТ2

всегда открыт, так как

![]() .

При

.

При

![]() транзистор VТ1

закрыт, и напряжение на выходе практиче-

транзистор VТ1

закрыт, и напряжение на выходе практиче-

с ки

равно +Uип.

При

ки

равно +Uип.

При

![]() оба транзистора открыты, на выходе

имеется минимальное напряжение. Ключи

с Д–нагрузкой увеличивают быстро-действие

и повышают помехо-устойчивость по

сравнению с МДП-ключами с нагрузочными

индуци-рованными МДП-транзисторами.

Низ-кая скорость переключения зависит

от величины паразитной емкости, которая

перезаряжается в течение переходного

процесса. Формирование фронтов на выходе

ключа определяется временем заряда и

разряда эквивалентной емкости. Емкость

заряжается через нагрузочный транзистор,

а разряжается через VТ1.

Сопротивление нагрузочного транзистора

VТ2 почти в 10…20 раз превышает сопротивление

открытого ключевого транзистора. Поэтому

время включения (определяется

сопротивлением VТ1) намного меньше

времени выключения, определяемого

нагрузочным транзистором (рис. 9.6). В

связи с этим быстродействие ключа

ограничено большим временем выключения,

в течении которого Cн

заряжается до выходного напряжения

током, протекающим через нагрузочный

транзистор. Длительность фронта

выключения определяется из решения

системы уравнений для токов заряда

емкости и нагрузочного транзистора

оба транзистора открыты, на выходе

имеется минимальное напряжение. Ключи

с Д–нагрузкой увеличивают быстро-действие

и повышают помехо-устойчивость по

сравнению с МДП-ключами с нагрузочными

индуци-рованными МДП-транзисторами.

Низ-кая скорость переключения зависит

от величины паразитной емкости, которая

перезаряжается в течение переходного

процесса. Формирование фронтов на выходе

ключа определяется временем заряда и

разряда эквивалентной емкости. Емкость

заряжается через нагрузочный транзистор,

а разряжается через VТ1.

Сопротивление нагрузочного транзистора

VТ2 почти в 10…20 раз превышает сопротивление

открытого ключевого транзистора. Поэтому

время включения (определяется

сопротивлением VТ1) намного меньше

времени выключения, определяемого

нагрузочным транзистором (рис. 9.6). В

связи с этим быстродействие ключа

ограничено большим временем выключения,

в течении которого Cн

заряжается до выходного напряжения

током, протекающим через нагрузочный

транзистор. Длительность фронта

выключения определяется из решения

системы уравнений для токов заряда

емкости и нагрузочного транзистора

(9.23)

(9.23)

Приравняв правые части уравнений и выполнив интегрирование, получим выражения для времени выключения

![]() . (9.24)

. (9.24)

Для уменьшения tвыкл необходимо увеличивать удельную крутизну нагрузочного транзистора. Быстродействие ключа значительно возрастает при работе нагрузочного транзистора в крутой области ВАХ, так как высокое напряжение на затворе предотвращает закрывание нагрузочного транзистора во время переходного процесса. Ключ реализует логическую функцию инверсии НЕ.