- •Техническая Электроника

- •Оглавление

- •Предисловие

- •Введение

- •Глава 1 пассивные компоненты электронных устройств

- •1.1. Резисторы

- •Числовые коэффициенты первых трех рядов

- •Допустимые отклонения сопротивлений

- •Основные параметры резисторов

- •1.1.1. Система условных обозначений и маркировка резисторов

- •Специальные резисторы

- •1.2. Конденсаторы

- •1.2.1. Система условных обозначений конденсаторов

- •1.2.2. Параметры постоянных конденсаторов

- •1.2.3. Конденсаторы переменной ёмкости

- •1.3. Катушки индуктивности

- •Параметры катушек индуктивности

- •Глава 2 полупроводниковые диоды

- •2.1. Физические основы полупроводниковых приборов

- •2.2. Примесные полупроводники

- •2.3. Электронно-дырочный переход

- •2.4. Физические процессы в p–n переходе

- •2.5. Контактная разность потенциалов

- •2.6. Прямое включение p–n перехода

- •2.7. Обратное включение p–n перехода

- •2.8. Вольт–амперная характеристика p–n перехода

- •2.9. Пробой p–n перехода

- •2.10. Емкостные свойства p–n перехода

- •2.11. Полупроводниковые диоды

- •Система обозначения полупроводниковых диодов

- •2.12. Выпрямительные диоды

- •Параметры выпрямительных диодов

- •2.13. Стабилитроны

- •Параметры стабилитрона

- •2.14. Варикапы

- •Параметры варикапов

- •2.15. Импульсные диоды

- •Параметры импульсных диодов

- •2.15.1. Диоды с накоплением заряда и диоды Шотки

- •2.16. Туннельные диоды

- •Параметры туннельных диодов

- •2.17. Обращенные диоды

- •Глава 3 биполярные транзисторы

- •3.1. Режимы работы биполярного транзистора

- •3.2. Принцип действия транзистора

- •3.3. Токи в транзисторе

- •3.4. Статические характеристики

- •3.4.1. Статические характеристики в схеме с об входные характеристики

- •Выходные характеристики

- •Характеристики прямой передачи

- •Характеристики обратной связи

- •3.5. Статические характеристики транзистора в схеме с оэ

- •3.6. Малосигнальные параметры Дифференциальные параметры транзистора

- •Система z–параметров.

- •Система y–параметров

- •Система h–параметров

- •Определение h–параметров по статическим характеристикам

- •3.7. Малосигнальная модель транзистора

- •3.8. Моделирование транзистора

- •3.9. Частотные свойства транзисторов

- •3.10. Параметры биполярных транзисторов

- •Глава 4 полевые транзисторы

- •4.1. Полевой транзистор с управляющим p-n переходом

- •Статические характеристики

- •4.2. Полевые транзисторы с изолированным затвором

- •4.2.2. Статические характеристики мдп-транзистора с

- •4.3. Полевые транзисторы со встроенным каналом

- •4.4. Cтатические характеристики транзистора со

- •4.5. Cпособы включения полевых транзисторов

- •4.6. Полевой транзистор как линейный четырехполюсник

- •4.7. Эквивалентная схема и частотные свойства

- •4.8. Основные параметры полевых транзисторов

- •Глава 5 полупроводниковые переключающие приборы

- •5.1. Диодный тиристор

- •5.2. Триодный тиристор

- •5.3. Симметричные тиристоры (симисторы)

- •5.4. Параметры тиристоров

- •Глава 6 электронно-лучевые приборы

- •6.1. Электростатическая система фокусировки луча

- •6.2. Электростатическая отклоняющая система

- •6.3. Трубки с магнитным управлением электронным лучом

- •6.4. Экраны электронно-лучевых трубок

- •6.5. Система обозначения электронно-лучевых трубок

- •6.6. Осциллографические трубки

- •6.7. Индикаторные трубки

- •6.8. Кинескопы

- •6.9. Цветные кинескопы

- •Глава 7 элементы и устройства оптоэлектроники

- •7.1. Источники оптического излучения

- •7.2. Характеристики светодиодов

- •7.3. Основные параметры светодиодов

- •7.4. Полупроводниковые приемники излучения

- •7.5. Фоторезисторы

- •7.6. Характеристики фоторезистора

- •7.7. Параметры фоторезистора

- •7.8. Фотодиоды

- •7.9. Характеристики и параметры фотодиода

- •7.10. Фотоэлементы

- •7.11. Фототранзисторы

- •7.12. Основные характеристики и параметры фототранзисторов

- •7.13. Фототиристоры

- •7.14. Оптопары

- •7.15. Входные и выходные параметры оптопар

- •7.16. Жидкокристаллические индикаторы

- •Параметры жки

- •Глава 8 элементы интегральных микросхем

- •8.1. Пассивные элементы интегральных микросхем

- •8.1.1. Резисторы

- •8.1.2. Конденсаторы

- •8.1.3. Пленочные конденсаторы

- •8.2. Биполярные транзисторы

- •8.3. Диоды полупроводниковых имс

- •8.4. Биполярные транзисторы с инжекционным питанием

- •8.5. Полупроводниковые приборы c зарядовой связью

- •Применение пзс

- •Параметры элементов пзс

- •Глава 9 основы цифровой техники

- •9.1. Электронные ключевые схемы

- •9.2. Ключи на биполярном транзисторе

- •9.3. Ключ с барьером Шотки

- •9.4. Ключи на мдп транзисторах

- •9.5. Ключ на комплементарных транзисторах

- •9.6. Алгебра логики и основные её законы

- •9.7. Логические элементы и их классификация

- •Классификация ис по функциональному назначению

- •Классификация ис по функциональному назначению

- •9.8. Базовые логические элементы цифровых

- •9.9. Диодно–транзисторная логика

- •9.10. Транзисторно–транзисторная логика (ттл)

- •9.11. Микросхемы ттл серий с открытым коллектором

- •9.12. Правила схемного включения элементов

- •9.13. Эмиттерно–связанная логика

- •9.14. Интегральная инжекционная логика (и2л)

- •9.15. Логические элементы на мдп-транзисторах

- •9.16. Параметры цифровых ис

- •9.17. Триггеры

- •Параметры триггеров

- •9.18. Мультивибраторы

- •9.18.1. Мультивибраторы на логических интегральных элементах

- •9.18.2. Автоколебательный мультивибратор с

- •9.18.3. Автоколебательные мультивибраторы с

- •9.18.4. Ждущие мультивибраторы

- •Глава 10 аналоговые устройства

- •10.1. Классификация аналоговых электронных устройств

- •10.2. Основные технические показатели и характеристики аналоговых устройств

- •10.3. Методы обеспечения режима работы транзистора в каскадах усиления

- •10.3.1. Схема с фиксированным током базы

- •10.3.2. Схема с фиксированным напряжением база–эмиттер

- •10.3.3. Схемы с температурной стабилизацией

- •10.4. Стабильность рабочей точки

- •10.5. Способы задания режима покоя в усилительных

- •10.6. Обратные связи в усилителях

- •10.6.1. Последовательная обратная связь по напряжению

- •10.6.2. Последовательная обратная связь по току

- •10.7. Режимы работы усилительных каскадов

- •10.8. Работа активных элементов с нагрузкой

- •10.9. Усилительный каскад с общим эмиттером

- •10.10. Усилительный каскад по схеме с общей базой

- •10.11. Усилительный каскад с общим коллектором

- •10.12. Усилительные каскады на полевых транзисторах

- •10.12.1. Усилительный каскад с ои

- •10.12.2. Усилительный каскад с общим стоком

- •10.13. Усилители постоянного тока

- •Глава 11 Дифференциальные и операционные усилители

- •11.1. Дифференциальные усилители

- •11.2. Операционные усилители

- •11.3. Параметры операционных усилителей

- •11.4. Амплитудно и фазочастотные характеристики оу

- •11.5. Устройство операционных усилителей

- •11.6. Оу общего применения

- •11.7. Инвертирующий усилитель

- •11.8. Неинвертирующий усилитель

- •11.9. Суммирующие схемы

- •11.9.1. Инвертирующий сумматор

- •11.9.2. Неинвертирующий сумматор

- •11.9.3. Интегрирующий усилитель

- •11.9.4. Дифференцирующий усилитель

- •11.9.5. Логарифмические схемы

- •11.9.6. Антилогарифмирующий усилитель

- •Глава 12 компараторы напряжения

- •Глава 13 Цифро-аналоговые преобразователи

- •13.1. Параметры цап

- •13.2. Устройство цап

- •Глава 14 Аналого-цифровые преобразователи

- •14.1. Параметры ацп

- •14.2. Классификация ацп

- •14.3. Ацп последовательного приближения

- •ЛитературА

9.10. Транзисторно–транзисторная логика (ттл)

Элементы транзисторно-транзисторной логики являются дальнейшим усовершенствованием ДТЛ, которая осуществляется заменой диодной сборки многоэмиттерным транзистором. Многоэмиттерный транзистор представляет собой совокупность нескольких транзисторных структур, имеющих общий коллектор и общую базу и непосредственно взаимодействующих друг с другом только за счет движения основных носителей. Эмиттерные переходы МЭТ выполняют функции входных диодов в схемах ДТЛ, а коллекторный переход – роль смещающего диода. Характерной особенностью элементов транзисторно-транзисторной логики является высокая помехоустойчивость, большое быстродействие, хорошая нагрузочная способность, малая потребляемая мощность, высокая надежность, малая стоимость.

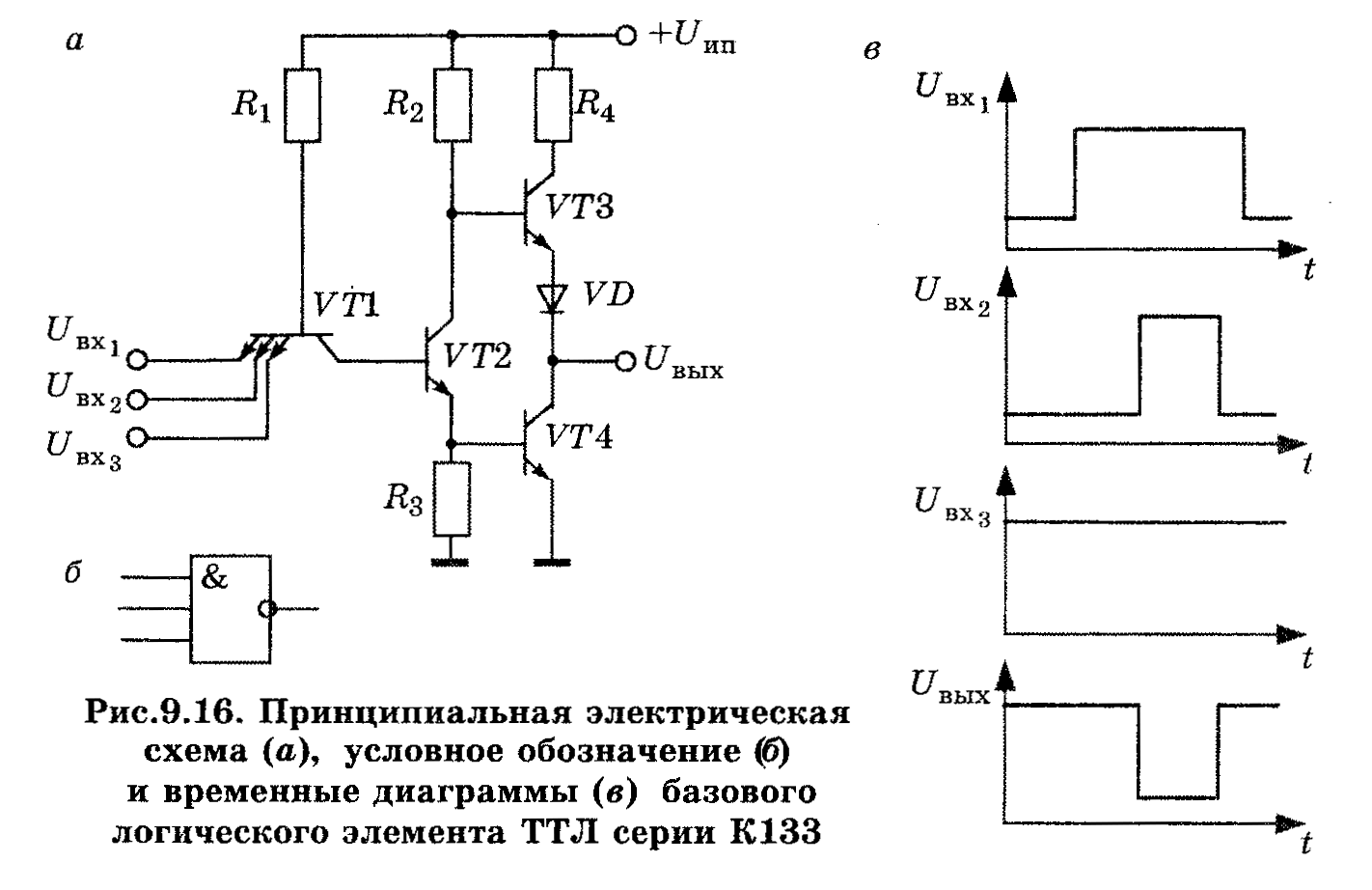

Принципиальная электрическая схема, условное обозначение, временные диаграммы базового логического элемента серий ТТЛ приведены на рис. 9.16. Базовый логический элемент ТТЛ выполняет операцию И–НЕ (является элементом Шеффера). Схема базового элемента ТТЛ состоит из двух частей. Входная часть реализует логическую функцию И с помощью VТ1 и резистора R1. Выходная цепь реализует функцию НЕ и содержит сложный инвертор на транзисторах VТ2…VТ4. Сложный инвертор включает в свой состав простой инвертор (VТ2, R2) и эмиттерный повторитель (VТ3) с динамической нагрузкой (VТ4), которая управляется эмиттерным током транзистора VТ2. Простой ин-

вертор в этой схеме (VТ2) является фазоинверсным каскадом. Если транзистор VТ2 открыт, то через него протекает большой эмиттерный ток, который является базовым током транзистора VТ4. Транзистор VТ4 открывается и переходит в режим насыщения. А транзистор VТ3 закрывается низким коллекторным потенциалом транзистора VТ2. Выходное напряжение близко к нулю. Если транзистор VТ2 закрыт, то транзистор VТ3 открыт, ибо потенциал базы транзистора VТ3 близок к Uип, а транзистор VТ4 закрыт. Выходное напряжение имеет высокий уровень и соответствует логической единице. При запирании транзистора VТ4 ток рассасывания избыточных носителей из базы транзистора VТ4 протекает через резистор R3 на землю. Резистор R4 ограничивает ток выходного каскада во время перехода схемы из открытого состояния в закрытое, когда транзистор VТ3 уже открылся, а транзистор VT4 еще находится в режиме насыщения. Диод VD обеспечивает надежное запирание транзистора VТ3, при напряжении на выходе схеме равном нулю. Сопротивление резистора R4 выбирается исходя из заданного значения предельно допустимого тока транзисторов VТ3, VТ4 и диода VD и составляет величину порядка 50…500 Ом. Для сопротивлений других резисторов существуют оптимальные значения: R1/R2=2…4; R2/R3=1…2; R2/R4=10.

Рассмотрим

принцип работы схемы. Если хотя бы на

один из входов подано напряжение

логического нуля, то соответствующий

эмиттерный переход многоэмиттерного

транзистора VТ1

открывается. Ток базы

![]() транзистора VT1

потечет во входную цепь, при этом ток

коллектора VТ1

уменьшается, коллекторный переход

открывается и транзистор VТ1

насыщается по коллекторной цепи.

Напряжение на базе транзистора VТ2

равно сумме входного напряжения и

остаточного напряжения на насыщенном

транзисторе VТ1:

транзистора VT1

потечет во входную цепь, при этом ток

коллектора VТ1

уменьшается, коллекторный переход

открывается и транзистор VТ1

насыщается по коллекторной цепи.

Напряжение на базе транзистора VТ2

равно сумме входного напряжения и

остаточного напряжения на насыщенном

транзисторе VТ1:

![]() .

Поэтому транзистор VТ2

запирается, а транзистор VТ3

и диод VD открываются высоким потенциалом

коллектора транзистора VТ2.

Транзистор VТ4 –

закрыт. Напряжение на выходе имеет

высокий уровень и соответствует

логической единице "1".

.

Поэтому транзистор VТ2

запирается, а транзистор VТ3

и диод VD открываются высоким потенциалом

коллектора транзистора VТ2.

Транзистор VТ4 –

закрыт. Напряжение на выходе имеет

высокий уровень и соответствует

логической единице "1".

Если на всех логических входах действуют высокие уровни напряжения, то эмиттерные переходы транзистора VТ1 закрываются, VТ1 работает в инверсном активном режиме. Ток от Uип через R1, открытый коллекторный переход транзистора VТ1 поступает в базу транзистора VТ2. Транзисторы VТ2, VТ4 открываются, и на выходе схемы имеется уровень напряжения, соответствующий логическому нулю. Транзистор VТ3 и диод VD закрыты.

Базовые

элементы различных серий ТТЛ различаются

только инверторами, которые должны

улучшать переходные характеристики,

повышать помехоустойчивость и нагрузочную

способность, потреблять небольшую

мощность. Для уменьшения входных токов

транзистор VТ1

должен обладать малым коэффициентом

передачи тока базы в инверсном режиме

![]() .

.

Логические элементы со сложным инвертором потребляют большую мощность, занимают большую площадь кристалла, поэтому на их основе изготавливаются цифровые микросхемы малой и средней степени интеграции.

Быстродействие логических элементов различных серий ТТЛ можно повысить двумя путями:

– уменьшая сопротивление резисторов и паразитные емкости;

– обеспечивая работу транзисторов в активном, т.е. ненасыщенном режиме, при котором отсутствует накопление и рассасывание носителей в базах транзисторов. Оба эти способа повышения быстродействия нашли практическое применение.

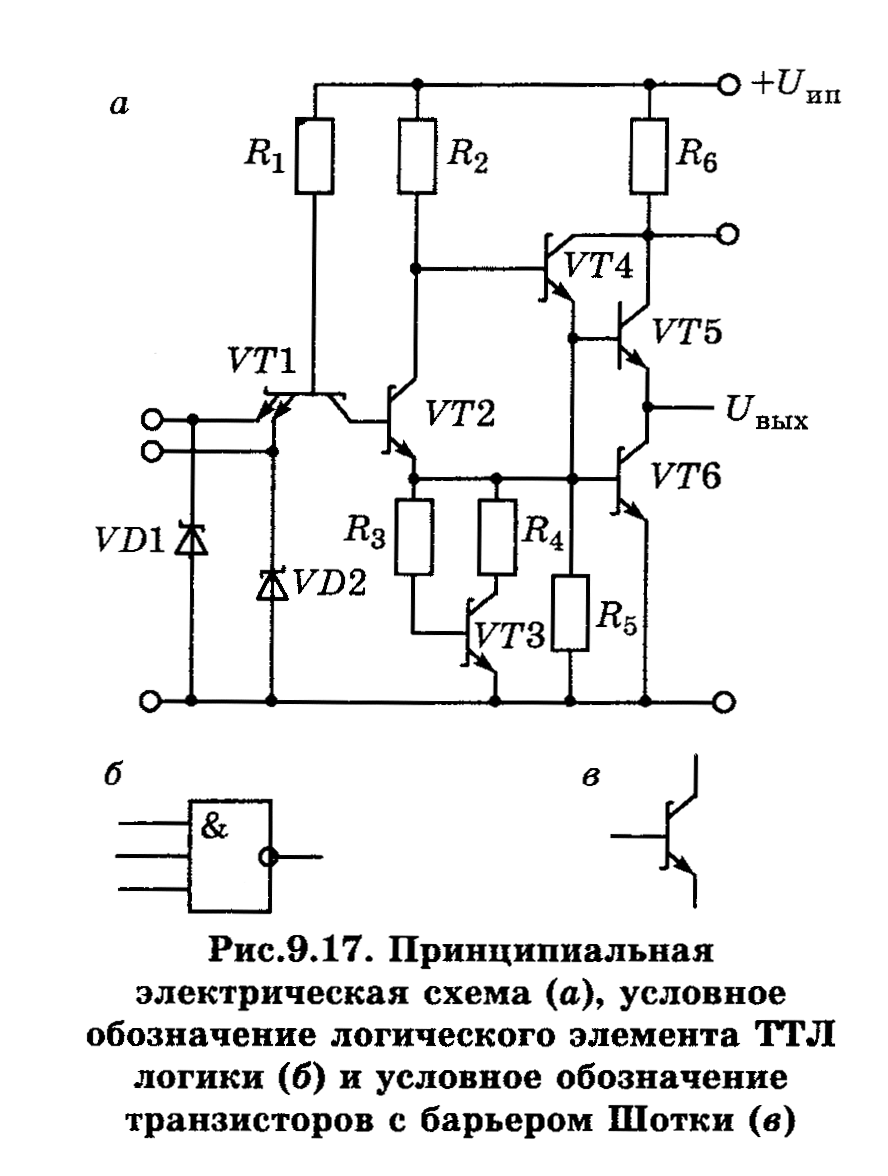

Первый способ использовался при создании ТТЛ серий К130 и К131. Второй способ повышения быстродействия цифровых микросхем ТТЛ связан с применением транзисторов с барьером Шотки. При этом высокое быстродействие сочетается с умеренным потреблением мощности. Диоды Шотки подключаются параллельно коллекторному переходу транзистора, а транзисторы с диодами Шотки называют транзисторами с барьером Шотки или транзисторами Шотки (рис. 9.17,а,б). Когда транзистор закрыт или работает в ненасыщенном, активном режиме, потенциал коллектора выше потенциала базы. Диод Шотки закрыт и не влияет на работу транзистора. При насыщении транзистора потенциал коллектора уменьшается, диод Шотки открывается при напряжении 0,3…0,5 В и фиксирует этот уровень напряжения на коллекторном переходе, не позволяя транзистору перейти в режим насыщения. Применение транзисторов Шотки позволяет уменьшить или почти полностью исключить время рассасывания избыточного заряда в базе и тем самым снизить время выключения схемы. На рис. 9.17,в показана принципиальная схема базового элемента ТТЛШ

с ерии.

Промышленностью выпускается следующие

серии ТТЛШ логики: К530, К531, КР1531 и

маломощные К555, КР1533 с потребляемой

мощностью порядка 2 мВт. По принципу

действия эта схема аналогична базовому

ТТЛ логическому элементу (рис. 9.16).

Отличие состоит лишь в том, что в выходном

каскаде использован составной транзистор

VТ4,

VТ5,

обеспечивающий повышенный выходной

ток, а каскад с ОЭ (генератор тока) на

транзисторе VТ3

с резисторами R3,

R4,

включенный в эмиттерную цепь транзистора

VТ2,

улучшает форму передаточной характеристики,

приближая ее к прямоугольной. Транзистор

VТ5

реализуется без диода Шотки, т.к. он

работает в активном режиме (эмиттерный

повторитель).

ерии.

Промышленностью выпускается следующие

серии ТТЛШ логики: К530, К531, КР1531 и

маломощные К555, КР1533 с потребляемой

мощностью порядка 2 мВт. По принципу

действия эта схема аналогична базовому

ТТЛ логическому элементу (рис. 9.16).

Отличие состоит лишь в том, что в выходном

каскаде использован составной транзистор

VТ4,

VТ5,

обеспечивающий повышенный выходной

ток, а каскад с ОЭ (генератор тока) на

транзисторе VТ3

с резисторами R3,

R4,

включенный в эмиттерную цепь транзистора

VТ2,

улучшает форму передаточной характеристики,

приближая ее к прямоугольной. Транзистор

VТ5

реализуется без диода Шотки, т.к. он

работает в активном режиме (эмиттерный

повторитель).

В перспективных интегральных микросхемах применяются новые интегральные транзисторы со структурой "Изопланар-П", у которых использована оксидная изоляция между транзисторами, а не привычный p–n переход. Граничная частота у транзисторов с такой структурой достигает 5 ГГц, что в 3 раза выше, чем у транзисторов с планарной структурой.

Выигрыш

в быстродействии схем с использованием

транзисторов Шотки приводит к некоторому

ухудшению статических параметров:

понижается пороговое напряжение,

повышается значение логического нуля

![]() ,

ухудшается помехоустойчивость. Для

повышения помехоустойчивости логических

элементов в эмиттерные цепи многоэмиттерного

транзистора VТ1

вводят диоды VD1–VD2,

включенные в обратном направлении для

сигналов логической единицы и нуля.

Если напряжения на входах логического

элемента меняют свой знак на противоположный,

то диоды VD1,

VD2

открываются. Сигнал помехи не поступает

на вход транзистора VТ1,

и не происходит ложное срабатывание

схемы.

,

ухудшается помехоустойчивость. Для

повышения помехоустойчивости логических

элементов в эмиттерные цепи многоэмиттерного

транзистора VТ1

вводят диоды VD1–VD2,

включенные в обратном направлении для

сигналов логической единицы и нуля.

Если напряжения на входах логического

элемента меняют свой знак на противоположный,

то диоды VD1,

VD2

открываются. Сигнал помехи не поступает

на вход транзистора VТ1,

и не происходит ложное срабатывание

схемы.