- •Техническая Электроника

- •Оглавление

- •Предисловие

- •Введение

- •Глава 1 пассивные компоненты электронных устройств

- •1.1. Резисторы

- •Числовые коэффициенты первых трех рядов

- •Допустимые отклонения сопротивлений

- •Основные параметры резисторов

- •1.1.1. Система условных обозначений и маркировка резисторов

- •Специальные резисторы

- •1.2. Конденсаторы

- •1.2.1. Система условных обозначений конденсаторов

- •1.2.2. Параметры постоянных конденсаторов

- •1.2.3. Конденсаторы переменной ёмкости

- •1.3. Катушки индуктивности

- •Параметры катушек индуктивности

- •Глава 2 полупроводниковые диоды

- •2.1. Физические основы полупроводниковых приборов

- •2.2. Примесные полупроводники

- •2.3. Электронно-дырочный переход

- •2.4. Физические процессы в p–n переходе

- •2.5. Контактная разность потенциалов

- •2.6. Прямое включение p–n перехода

- •2.7. Обратное включение p–n перехода

- •2.8. Вольт–амперная характеристика p–n перехода

- •2.9. Пробой p–n перехода

- •2.10. Емкостные свойства p–n перехода

- •2.11. Полупроводниковые диоды

- •Система обозначения полупроводниковых диодов

- •2.12. Выпрямительные диоды

- •Параметры выпрямительных диодов

- •2.13. Стабилитроны

- •Параметры стабилитрона

- •2.14. Варикапы

- •Параметры варикапов

- •2.15. Импульсные диоды

- •Параметры импульсных диодов

- •2.15.1. Диоды с накоплением заряда и диоды Шотки

- •2.16. Туннельные диоды

- •Параметры туннельных диодов

- •2.17. Обращенные диоды

- •Глава 3 биполярные транзисторы

- •3.1. Режимы работы биполярного транзистора

- •3.2. Принцип действия транзистора

- •3.3. Токи в транзисторе

- •3.4. Статические характеристики

- •3.4.1. Статические характеристики в схеме с об входные характеристики

- •Выходные характеристики

- •Характеристики прямой передачи

- •Характеристики обратной связи

- •3.5. Статические характеристики транзистора в схеме с оэ

- •3.6. Малосигнальные параметры Дифференциальные параметры транзистора

- •Система z–параметров.

- •Система y–параметров

- •Система h–параметров

- •Определение h–параметров по статическим характеристикам

- •3.7. Малосигнальная модель транзистора

- •3.8. Моделирование транзистора

- •3.9. Частотные свойства транзисторов

- •3.10. Параметры биполярных транзисторов

- •Глава 4 полевые транзисторы

- •4.1. Полевой транзистор с управляющим p-n переходом

- •Статические характеристики

- •4.2. Полевые транзисторы с изолированным затвором

- •4.2.2. Статические характеристики мдп-транзистора с

- •4.3. Полевые транзисторы со встроенным каналом

- •4.4. Cтатические характеристики транзистора со

- •4.5. Cпособы включения полевых транзисторов

- •4.6. Полевой транзистор как линейный четырехполюсник

- •4.7. Эквивалентная схема и частотные свойства

- •4.8. Основные параметры полевых транзисторов

- •Глава 5 полупроводниковые переключающие приборы

- •5.1. Диодный тиристор

- •5.2. Триодный тиристор

- •5.3. Симметричные тиристоры (симисторы)

- •5.4. Параметры тиристоров

- •Глава 6 электронно-лучевые приборы

- •6.1. Электростатическая система фокусировки луча

- •6.2. Электростатическая отклоняющая система

- •6.3. Трубки с магнитным управлением электронным лучом

- •6.4. Экраны электронно-лучевых трубок

- •6.5. Система обозначения электронно-лучевых трубок

- •6.6. Осциллографические трубки

- •6.7. Индикаторные трубки

- •6.8. Кинескопы

- •6.9. Цветные кинескопы

- •Глава 7 элементы и устройства оптоэлектроники

- •7.1. Источники оптического излучения

- •7.2. Характеристики светодиодов

- •7.3. Основные параметры светодиодов

- •7.4. Полупроводниковые приемники излучения

- •7.5. Фоторезисторы

- •7.6. Характеристики фоторезистора

- •7.7. Параметры фоторезистора

- •7.8. Фотодиоды

- •7.9. Характеристики и параметры фотодиода

- •7.10. Фотоэлементы

- •7.11. Фототранзисторы

- •7.12. Основные характеристики и параметры фототранзисторов

- •7.13. Фототиристоры

- •7.14. Оптопары

- •7.15. Входные и выходные параметры оптопар

- •7.16. Жидкокристаллические индикаторы

- •Параметры жки

- •Глава 8 элементы интегральных микросхем

- •8.1. Пассивные элементы интегральных микросхем

- •8.1.1. Резисторы

- •8.1.2. Конденсаторы

- •8.1.3. Пленочные конденсаторы

- •8.2. Биполярные транзисторы

- •8.3. Диоды полупроводниковых имс

- •8.4. Биполярные транзисторы с инжекционным питанием

- •8.5. Полупроводниковые приборы c зарядовой связью

- •Применение пзс

- •Параметры элементов пзс

- •Глава 9 основы цифровой техники

- •9.1. Электронные ключевые схемы

- •9.2. Ключи на биполярном транзисторе

- •9.3. Ключ с барьером Шотки

- •9.4. Ключи на мдп транзисторах

- •9.5. Ключ на комплементарных транзисторах

- •9.6. Алгебра логики и основные её законы

- •9.7. Логические элементы и их классификация

- •Классификация ис по функциональному назначению

- •Классификация ис по функциональному назначению

- •9.8. Базовые логические элементы цифровых

- •9.9. Диодно–транзисторная логика

- •9.10. Транзисторно–транзисторная логика (ттл)

- •9.11. Микросхемы ттл серий с открытым коллектором

- •9.12. Правила схемного включения элементов

- •9.13. Эмиттерно–связанная логика

- •9.14. Интегральная инжекционная логика (и2л)

- •9.15. Логические элементы на мдп-транзисторах

- •9.16. Параметры цифровых ис

- •9.17. Триггеры

- •Параметры триггеров

- •9.18. Мультивибраторы

- •9.18.1. Мультивибраторы на логических интегральных элементах

- •9.18.2. Автоколебательный мультивибратор с

- •9.18.3. Автоколебательные мультивибраторы с

- •9.18.4. Ждущие мультивибраторы

- •Глава 10 аналоговые устройства

- •10.1. Классификация аналоговых электронных устройств

- •10.2. Основные технические показатели и характеристики аналоговых устройств

- •10.3. Методы обеспечения режима работы транзистора в каскадах усиления

- •10.3.1. Схема с фиксированным током базы

- •10.3.2. Схема с фиксированным напряжением база–эмиттер

- •10.3.3. Схемы с температурной стабилизацией

- •10.4. Стабильность рабочей точки

- •10.5. Способы задания режима покоя в усилительных

- •10.6. Обратные связи в усилителях

- •10.6.1. Последовательная обратная связь по напряжению

- •10.6.2. Последовательная обратная связь по току

- •10.7. Режимы работы усилительных каскадов

- •10.8. Работа активных элементов с нагрузкой

- •10.9. Усилительный каскад с общим эмиттером

- •10.10. Усилительный каскад по схеме с общей базой

- •10.11. Усилительный каскад с общим коллектором

- •10.12. Усилительные каскады на полевых транзисторах

- •10.12.1. Усилительный каскад с ои

- •10.12.2. Усилительный каскад с общим стоком

- •10.13. Усилители постоянного тока

- •Глава 11 Дифференциальные и операционные усилители

- •11.1. Дифференциальные усилители

- •11.2. Операционные усилители

- •11.3. Параметры операционных усилителей

- •11.4. Амплитудно и фазочастотные характеристики оу

- •11.5. Устройство операционных усилителей

- •11.6. Оу общего применения

- •11.7. Инвертирующий усилитель

- •11.8. Неинвертирующий усилитель

- •11.9. Суммирующие схемы

- •11.9.1. Инвертирующий сумматор

- •11.9.2. Неинвертирующий сумматор

- •11.9.3. Интегрирующий усилитель

- •11.9.4. Дифференцирующий усилитель

- •11.9.5. Логарифмические схемы

- •11.9.6. Антилогарифмирующий усилитель

- •Глава 12 компараторы напряжения

- •Глава 13 Цифро-аналоговые преобразователи

- •13.1. Параметры цап

- •13.2. Устройство цап

- •Глава 14 Аналого-цифровые преобразователи

- •14.1. Параметры ацп

- •14.2. Классификация ацп

- •14.3. Ацп последовательного приближения

- •ЛитературА

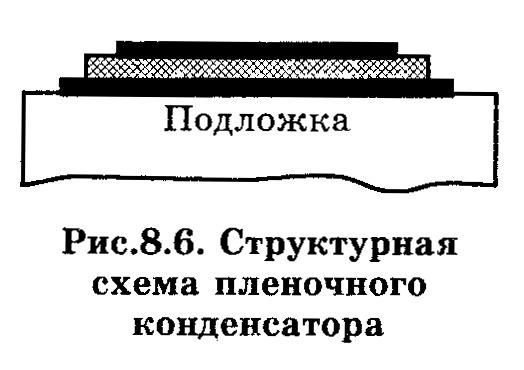

8.1.3. Пленочные конденсаторы

О ни

позволяют получить большую емкость и

представляют собой многослойную

структуру, показанную на рис. 8.6. На

подложку наносится слой металла, служащий

обкладкой конденсатора, на поверхности

которого наносится слой диэлектрика.

Диэлектрик покрывается металлическим

слоем, служащим второй обкладкой

конденсатора. В качестве диэлектрика

используется окись тантала или моноокись

кремния. Температурный коэффициент

емкости таких конденсаторов порядка

0,02…0,04 %/С,

а добротность на высоких частотах

определяется сопротивлением обкладок.

В связи с этим чаще используются

алюминиевые обкладки. Сопротивление

пленки тантала велико, порядка 100 Ом/,

поэтому танталовые конденсаторы являются

низкочастотными.

ни

позволяют получить большую емкость и

представляют собой многослойную

структуру, показанную на рис. 8.6. На

подложку наносится слой металла, служащий

обкладкой конденсатора, на поверхности

которого наносится слой диэлектрика.

Диэлектрик покрывается металлическим

слоем, служащим второй обкладкой

конденсатора. В качестве диэлектрика

используется окись тантала или моноокись

кремния. Температурный коэффициент

емкости таких конденсаторов порядка

0,02…0,04 %/С,

а добротность на высоких частотах

определяется сопротивлением обкладок.

В связи с этим чаще используются

алюминиевые обкладки. Сопротивление

пленки тантала велико, порядка 100 Ом/,

поэтому танталовые конденсаторы являются

низкочастотными.

В отличие от конденсаторов на основе p–n перехода в тонкопленочных конденсаторах параметры не зависят от величины и полярности прикладываемого напряжения и имеют большее значение емкости на единицу площади при меньшем паразитном воздействии. Однако имеется два основных недостатка, присущих тонкопленочным конденсаторам: требуются дополнительные технологические этапы, помимо обычных диффузионных циклов; выходят из строя из-за пробоя диэлектрика, когда напряжение превышает номинальное значение.

8.2. Биполярные транзисторы

Основным и наиболее универсальным элементом интегральных микросхем является биполярный транзистор. В большинстве случаев используется транзистор n–p–n типа, ибо подвижность электронов больше подвижности дырок, и они обладают лучшими частотными свойствами, чем транзисторы p–n–р типа.

Главное отличие структур биполярных транзисторов в микросхемах от дискретных транзисторов состоит в том, что интегральные транзисторы имеют дополнительные области, которые изолируют транзисторы от общей полупроводниковой подложки. Все выводы интегральных транзисторов располагаются на одной плоскости, что позволяет легко проводить межэлементные соединения всей микросхемы.

Изготовление транзисторов осуществляется одновременно с созданием других элементов схемы: резисторов, конденсаторов, диодов; при этом используются аналогичные полупроводниковые области: эмиттерная, базовая, коллекторная, т.е. все элементы полупроводниковых микросхем конструктивно и технологически совместимы.

С труктура

планарно-эпитаксиального транзистора

представлена на рис. 8.7. На кремниевой

подложке с электропроводностью р–типа

методом диффузии изготавливаются

области коллектора, базы и эмиттера.

Особенностью планарных транзисторов

является неравномерное распределение

примеси в коллекторной области. Наличие

большого числа примеси у коллекторного

перехода обуславливает низкое значение

пробивного напряжения коллекторного

перехода и большое значение обратного

сопротивления коллектора. Все это

вызывает сильное влияние подложки на

электрические параметры транзистора

и ограничивает возможности планарных

транзисторов в полупроводниковых

интегральных схемах.

труктура

планарно-эпитаксиального транзистора

представлена на рис. 8.7. На кремниевой

подложке с электропроводностью р–типа

методом диффузии изготавливаются

области коллектора, базы и эмиттера.

Особенностью планарных транзисторов

является неравномерное распределение

примеси в коллекторной области. Наличие

большого числа примеси у коллекторного

перехода обуславливает низкое значение

пробивного напряжения коллекторного

перехода и большое значение обратного

сопротивления коллектора. Все это

вызывает сильное влияние подложки на

электрические параметры транзистора

и ограничивает возможности планарных

транзисторов в полупроводниковых

интегральных схемах.

Улучшить ряд параметров транзисторов удается используя планарно-эпитаксиальную технологию. Важной конструктивной особенностью эпитаксиально-планарных транзисторов является скрытый n+–слой, предназначенный для уменьшения объемного сопротивления коллекторной области и уменьшения степени влияния подложки на характеристики и параметры транзисторов. Низкоомный скрытый слой шунтирует расположенный над ним более высокоомный коллекторный слой n–типа и в десятки раз уменьшает объемное сопротивление коллекторной области между коллекторным переходом и выводом коллектора.

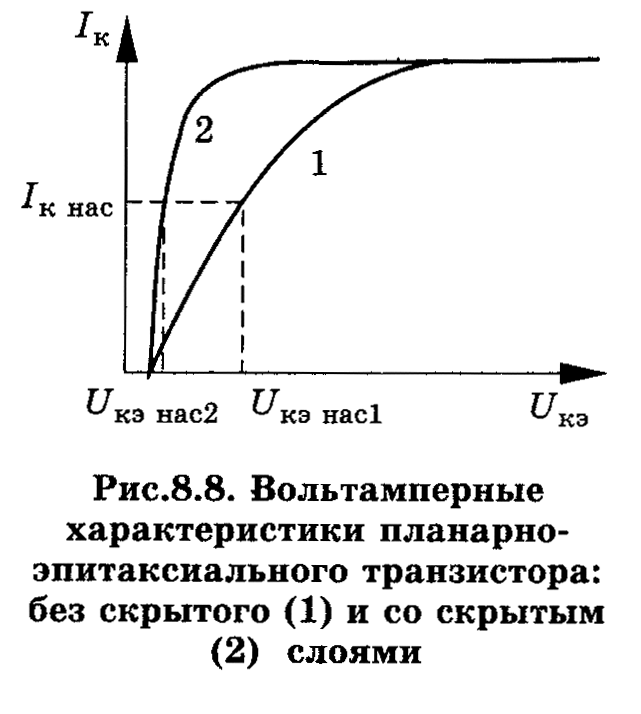

В ыходные

характеристики в схеме с общим эмиттером

в диапазоне малых значений Uкэ

для транзисторов без скрытого слоя 1 и

со скрытым слоем 2 приведены на рис. 8.8.

Скрытый n+–слой

влияет на форму выходной характеристики

только в режиме насыщения, где rк диф

невелико. Скрытый слой позволяет получить

малое значение остаточного напряжения

при работе транзистора в цифровых

микросхемах.

ыходные

характеристики в схеме с общим эмиттером

в диапазоне малых значений Uкэ

для транзисторов без скрытого слоя 1 и

со скрытым слоем 2 приведены на рис. 8.8.

Скрытый n+–слой

влияет на форму выходной характеристики

только в режиме насыщения, где rк диф

невелико. Скрытый слой позволяет получить

малое значение остаточного напряжения

при работе транзистора в цифровых

микросхемах.

Интегральные транзисторы в полупроводниковых микросхемах обладают следующими параметрами: коэффициент передачи тока базы порядка 200; граничная частота до 500 МГц; емкость коллектора до 0,5 пФ; пробивное напряжение для коллекторного перехода до 50 В, для эмиттерного до 8 В; удельное сопротивление n– и p–слоев составляет несколько сотен, а n+–слоя – не более 20 Ом/.

В виду

того, что интегральный транзистор

занимает малую площадь подложки по

сравнению с пассивными элементами, то

в интегральных микросхемах используется

большее число транзисторов, чем в

дискретных аналогах.

виду

того, что интегральный транзистор

занимает малую площадь подложки по

сравнению с пассивными элементами, то

в интегральных микросхемах используется

большее число транзисторов, чем в

дискретных аналогах.

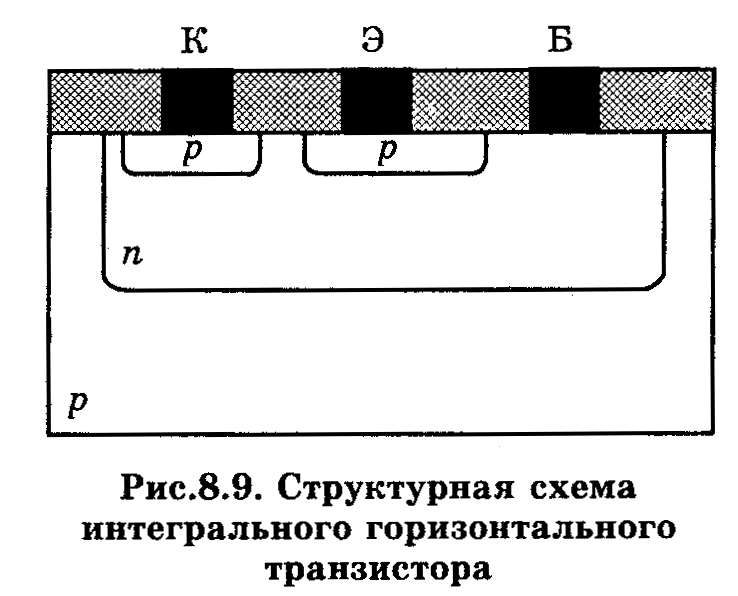

Некоторые аналоговые схемы требуют использования p–n–р транзисторов, которые изготавливаются одновременно с транзисторами n–p–n типа. Такой интегральный транзистор принято называть горизонтальным, боковым или латеральным (рис. 8.9).

Эмиттерный и коллекторный переходы изготавливаются одновременно за счет диффузии акцепторной примеси. За счет меньшей подвижности дырок коэффициент передачи тока базы и граничная частота усиления значительно ниже, чем у аналогичных n–p–n транзисторов.

В латеральном транзисторе перенос зарядов протекает в горизонтальном направлении, параллельно поверхности подложки. Инжектированные эмиттером дырки диффундируют в горизонтальном направлении к коллектору. Коэффициент усиления по току латерального транзистора невелик из-за малого коэффициента инжекции эмиттера и широкой базы. Относительно низкая концентрация примесей и небольшая эффективная площадь эмиттера не позволяют получить большой коэффициент инжекции эмиттера. Одинаковые области эмиттера и коллектора обуславливают симметрию латерального транзистора, а это значит, что прямой и инверсный коэффициенты усиления по току почти одинаковы. Пробивные напряжения обоих переходов также практически одинаковы и составляют 30…50 В.

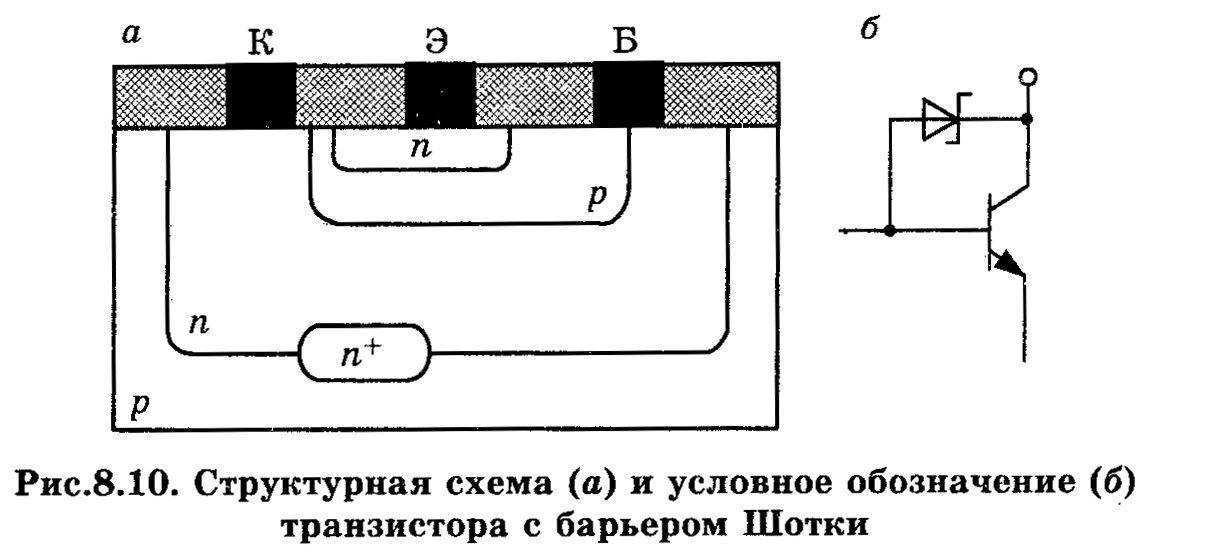

Важным параметром, характеризующим быстродействие транзистора, является время рассасывания избыточных зарядов. Для уменьшения его, интегральный транзистор легируется золотом, которое имеет большой коэффициент диффузии и проникает во все области транзистора (базу, эмиттер, коллектор). Это приводит к созданию дополнительных центров рекомбинации. В результате уменьшается время жизни неосновных носителей в базе и снижаются коэффициенты передачи h21э, h21б. Чтобы сохранить высокие значения h21э, h21б, уменьшив время рассасывания, переход база-коллектор шунтируют диодом Шотки. Такие транзисторы называют транзисторами с барьером Шотки. В отличие от планарного транзистора у транзисторов с барьером Шотки базовое контактное отверстие расширено в сторону коллекторной области n–типа (рис. 8.10,а). Диод Шотки образуется в месте контакта металла с высокоомной коллекторной областью n–типа. Диод Шотки оказывается включенным параллельно коллекторному переходу (рис. 8.10,б).

В режиме отсечки и в активном режиме потенциал коллектора выше потенциала базы, диод Шотки закрыт, и транзистор работает как обычный биполярный транзистор. При переходе из активного в режим насыщения потенциал коллектора становится меньше потенциала базы. Диод Шотки открывается, и основная часть тока базы поступает в коллектор через диод Шотки, минуя область базы транзистора. При этом не происходит накопления избыточного заряда в области базы, и при переключении транзистора из режима насыщения в активный или режим отсечки почти отсутствует процесс рассасывания избыточного заряда. Время рассасывания избыточного заряда определяется временем пролета электронов через базу и для транзисторов с достаточно тонкой базой менее 1 мкм составляет не более 1 нс.

Основная область применения транзисторов с диодом Шотки – это цифровые микросхемы с повышенным быстродействием, где транзисторы работают в режиме насыщения. На быстродействие работы транзистора в импульсном режиме, кроме времени рассасывания, сильно влияют время задержки, нарастания и спада, которые определяются барьерными емкостями переходов и емкостью нагрузки. Применение транзисторов с диодом Шотки позволяет повысить быстродействие цифровых микросхем в 2…5 раз.

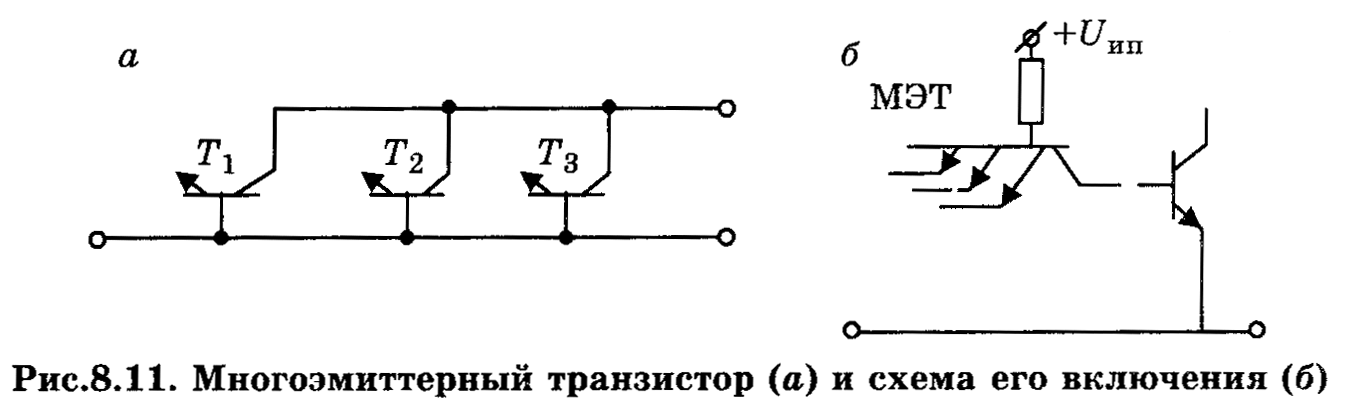

В цифровых интегральных микросхемах широко используются особые транзисторные структуры – многоэмиттерные транзисторы, неимеющие дискретного аналога. Многоэмиттерные n–p–n транзисторы (МЭТ) отличаются от одноэмиттерных тем, что в их базовой области р–типа создается несколько эмиттерных областей (обычно 4…8). Структуры МЭТ получаются в едином технологическом процессе изготовления ИС вместе с одноэмиттерными интегральными транзисторами. Многоэмиттерный транзистор можно представить в виде совокупности отдельных n–p–n транзисторов, число которых равно числу эмиттеров (рис. 8.11,а), и имеющих общие коллектор и базу.

Под каждым эмиттером расположена активная область базы, а между соседними эмиттерами – пассивная область. Соседние эмиттеры вместе с разделяющей их пассивной областью базы образуют литеральный паразитный транзистор n–p–n типа. Роль коллектора в паразитном транзисторе выполняет эмиттер, на который подано отрицательное напряжение. Для устранения паразитного явления расстояние между соседними эмиттерами МЭТ делают больше диффузионной длины неосновных носителей заряда в базе.

Включение МЭТ осуществляется по схеме, представленной на рис. 8.11,б. МЭТ используется для создания микросхем транзисторно-транзисторной логики. В интегральных микросхемах часто используется инверсное включение МЭТ, при этом транзистор называют многоколлекторным транзистором (МКТ). Многоколлекторный транзистор находит применение в интегральных схемах с инжекционным питанием.