- •1. Режимы работы усилительных элементов.

- •2. Режим класса а

- •3. Режим класса в

- •4. Режим класса с

- •5. Динамический режим работы транзистора.

- •6 . Построение сквозной динамической характеристики

- •7. Расчет коэффициента гармоник.

- •8.Основные показатели, характеризующие работу усилителя.

- •9 . Амплитудная характеристика усилителя.

- •10. Частотная характеристика усилителя.

- •11. Динамический диапазон усилителя.

- •12. Полоса пропускания усилителя.

- •13. Чувствительность усилителя.

- •14. Резистивный каскад. Принципиальная схема.

- •15. Эквивалентная схема резистивного каскада.

- •16. Частотная хар-ка резистивного каскада.

- •17. Роль разделительных конденсаторов в резистивном каскаде.

- •18. Трансформаторный каскад. Принципиальная схема.

- •19. Эквивалентная схема трансформаторного каскада.

- •20. Частотная хар-ка трансформаторного каскада.

- •21. Двухтактные каскады. Преимущества.

- •22. Двухтактный трансформаторный каскад.

- •23. Двухтактный бестрансформаторный каскад.

- •24. Коэффициент асимметрии.

- •25. Использование комплиментарных транзисторов в двухтактных схемах.

- •26. Фазоинверсный каскад.

- •27. Обеспечение равенства амплитуд выходных напряжений фазоинверсного каскада.

- •28. Обратная связь электронных схем.

- •29. Отрицательная обратная связь.

- •30. Влияние отрицательной обратной связи на коэфициент усиления.

- •31. Глубина оос.

- •32. Глубокая оос.

- •33. Схемы с оос.

- •34. Положительная обратная связь.

- •35. Самовозбуждение усилителей.

- •36. Амплитудные условия самовозбуждения.

- •39. Операционные усилители.

- •40. Построение структурной схемы усилителя.

- •41. Построение принципиальной схемы усилителя.

- •42. Выбор транзисторов для каскадов усиления.

- •43. Температурная стабилизация в транзисторных схемах.

- •44. Дискретизация аналоговых сигналов.

- •45. Теорема Котельникова.

- •46. Логические операции.

- •47. Асинхронные rs-триггеры на элементах и-не. Временные диаграммы.

- •48. Асинхронные rs-триггеры на элементах или-не. Временные диаграммы.

- •50. Временные диаграммы д-триггера.

- •51. Синхронные т-триггеры.

- •52. Временные диаграммы т-триггера.

- •54. Временные диаграммы m-s-схемы.

- •55. Регистр сдвига.

- •56. Счетчики импульсов.

- •57. Однофазные выпрямители. Принцип действия.

- •58. Однополупериодный выпрямитель с активной нагрузкой.

- •59.Однополупериодный выпрямитель с активно-индуктивной нагрузкой.

- •60. Однофазный выпрямитель с нулевым выводом.

- •61.Мостовая схема выпрямителя.

- •62 Сглаживающие г-образные фильтры.

- •63 Сглаживающие г-образные фильтры.

- •65. Стабилизаторы.

- •66. Параметрические стабилизаторы.

- •67. Компенсационные стабилизаторы.

- •68. Автогенераторы.

54. Временные диаграммы m-s-схемы.

Основой микропроцессорной техники является триггер, который имеет 2 устойчивых состояния равновесия и переходит из одного состояния в другое с помощью внешних импульсов. Триггер позволяет определить состояние в предыдущем цикле и позволяет определить состояние в текущем времени. Поэтому основной узел оперативной памяти состоит из триггеров.

Триггер со счетным запуском.

M-S-схема. Синхронный триггер. Master – основной.

Slave – вспомогательный

55. Регистр сдвига.

Триггерным регистром сдвига называют совокупность триггеров с определенными связями между ними, при которых они действуют как единое устройство. В регистрах сдвига организация этих связей такова, что при подаче тактового импульса, общего для всех триггеров, выходное состояние каждого триггера сдвигается в соседний. В зависимости от организации связей этот сдвиг может происходить влево или вправо. Основным назначением этого регистра является преобразование двоичного последовательного кода в параллельный и наоборот. Они используются как элементы задержки цифровых сигналов или выполняют роль регистров памяти. Также они используются для реализации операций деления или умножения чисел.

Используют параллельный или последовательный ввод информации, при которых ввод двоичного числа осуществляется или одновременно во все разряды регистра, или последовательно во времени по отдельным разрядам. В счетчиках импульсов находят применение сдвигающие регистры с последовательным вводом и выводом и со сдвигом вправо.

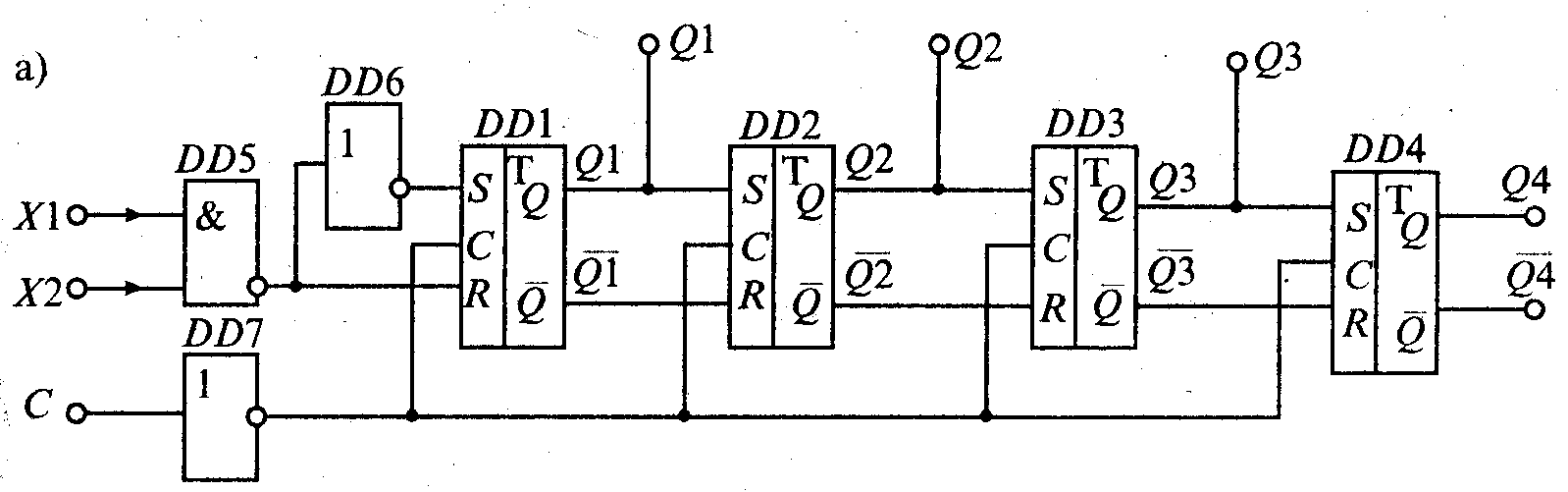

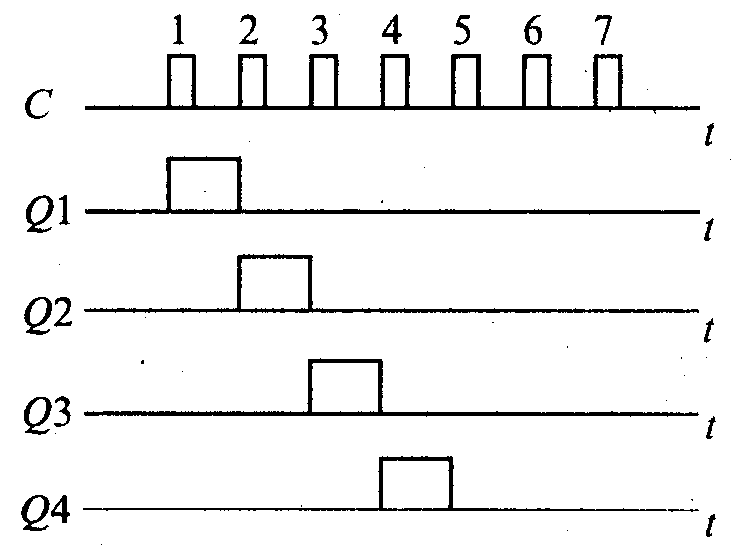

На рисунке приведены временные диаграммы выходных сигналов триггеров и схема четырехразрядного регистра сдвига, выполненного на RS-триггерах. В этой схеме каждый выход Q триггера соединен со входом S последующего разряда, а каждый выход -Q - с входом R. Тактовые входы всех триггеров соединены вместе, и поступление сигнала синхронизации осуществляется одним общим импульсом через логический элемент И-НЕ (DD7). Состояние первого триггера определяется входными сигналами на входах ХI и Х2 логического элемента И-НЕ (DD5). На вход ХI подается текущая информация, а на вход Х2 сигнал разрешения ее передачи. Логические элемент НЕ (DD6) используется для инвертирования входного сигнала, подаваемого на вход S.

Если при поступлении первого тактового импульса на входах ХI и Х2 установлены сигналы ХI=Х2=1, которые затем снимаются к приходу второго тактового импульса, то в результате в первый триггер будет записан сигнал Q1= 1. С приходом второго тактового импульса в первый триггер будет записан сигнал Q1=0, а на выходе второго триггера появиться сигнал Q2=2 , который перед этим был на выходе первого триггера. При поступлении последующих тактовых импульсов единичный сигнал перемещается последовательно в третий и четвертый триггеры, после чего все триггеры устанавливаются в нулевое состояние.

Сдвиговые регистры можно реализовать также на D-триггерах или JK-триггерах. Для всех регистров сдвига характерны следующие положения: 1) необходима предварительная установка исходного состояние и ввод единицы в первый триггер и 2) для регистра из n триггеров после поступления n входных тактовых импульсов первоначально введенная единица выводится, вследствие чего прямые выходы всех регистров оказывается в нулевом состоянии.

Интегральные микросхемы регистров сдвига бывают реверсивными, т. е. выполняющими сдвиг в любом направлении: вправо или влево. Направление сдвига определяется значением управляющего сигнала.