- •1. Режимы работы усилительных элементов.

- •2. Режим класса а

- •3. Режим класса в

- •4. Режим класса с

- •5. Динамический режим работы транзистора.

- •6 . Построение сквозной динамической характеристики

- •7. Расчет коэффициента гармоник.

- •8.Основные показатели, характеризующие работу усилителя.

- •9 . Амплитудная характеристика усилителя.

- •10. Частотная характеристика усилителя.

- •11. Динамический диапазон усилителя.

- •12. Полоса пропускания усилителя.

- •13. Чувствительность усилителя.

- •14. Резистивный каскад. Принципиальная схема.

- •15. Эквивалентная схема резистивного каскада.

- •16. Частотная хар-ка резистивного каскада.

- •17. Роль разделительных конденсаторов в резистивном каскаде.

- •18. Трансформаторный каскад. Принципиальная схема.

- •19. Эквивалентная схема трансформаторного каскада.

- •20. Частотная хар-ка трансформаторного каскада.

- •21. Двухтактные каскады. Преимущества.

- •22. Двухтактный трансформаторный каскад.

- •23. Двухтактный бестрансформаторный каскад.

- •24. Коэффициент асимметрии.

- •25. Использование комплиментарных транзисторов в двухтактных схемах.

- •26. Фазоинверсный каскад.

- •27. Обеспечение равенства амплитуд выходных напряжений фазоинверсного каскада.

- •28. Обратная связь электронных схем.

- •29. Отрицательная обратная связь.

- •30. Влияние отрицательной обратной связи на коэфициент усиления.

- •31. Глубина оос.

- •32. Глубокая оос.

- •33. Схемы с оос.

- •34. Положительная обратная связь.

- •35. Самовозбуждение усилителей.

- •36. Амплитудные условия самовозбуждения.

- •39. Операционные усилители.

- •40. Построение структурной схемы усилителя.

- •41. Построение принципиальной схемы усилителя.

- •42. Выбор транзисторов для каскадов усиления.

- •43. Температурная стабилизация в транзисторных схемах.

- •44. Дискретизация аналоговых сигналов.

- •45. Теорема Котельникова.

- •46. Логические операции.

- •47. Асинхронные rs-триггеры на элементах и-не. Временные диаграммы.

- •48. Асинхронные rs-триггеры на элементах или-не. Временные диаграммы.

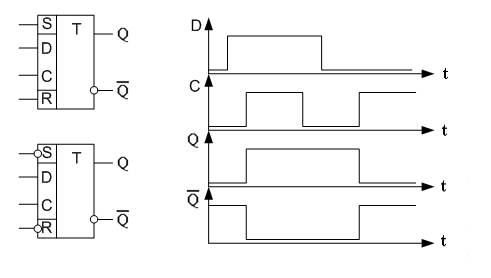

- •50. Временные диаграммы д-триггера.

- •51. Синхронные т-триггеры.

- •52. Временные диаграммы т-триггера.

- •54. Временные диаграммы m-s-схемы.

- •55. Регистр сдвига.

- •56. Счетчики импульсов.

- •57. Однофазные выпрямители. Принцип действия.

- •58. Однополупериодный выпрямитель с активной нагрузкой.

- •59.Однополупериодный выпрямитель с активно-индуктивной нагрузкой.

- •60. Однофазный выпрямитель с нулевым выводом.

- •61.Мостовая схема выпрямителя.

- •62 Сглаживающие г-образные фильтры.

- •63 Сглаживающие г-образные фильтры.

- •65. Стабилизаторы.

- •66. Параметрические стабилизаторы.

- •67. Компенсационные стабилизаторы.

- •68. Автогенераторы.

46. Логические операции.

В устройствах цифровой электроники используются элементы, входные и выходные сигналы которых могут принимать лишь два значения: логической единицы «1» и логического нуля «0». Такие элементы называемые логическими, осуществляют простейшие операции с такими двоичными числами.

Для описания алгоритмов работы и структуры логических схем используют простую алгебру логики (булеву алгебру). В её основе лежат три основные логические операции: логическое отрицание, или операция НЕ (инверсия), логическое сложение, или операция ИЛИ (дизъюнкция) и логическое умножение, или операция И (конъюнкция).

Некоторая логическая функция может быть задана в алгебраической форме или в виде таблицы истинности.

Наименование функции |

Условное графическое обозначение |

Выражение функции |

Таблицы истинности |

||||

x1 |

0 |

0 |

1 |

1 |

|||

x2 |

0 |

1 |

0 |

1 |

|||

ИЛИ |

|

y= x1+x2 |

y |

0 |

1 |

1 |

1 |

И |

|

y= x1 ·x2 |

y |

0 |

0 |

0 |

1 |

НЕ |

|

_ y= x1 |

y |

1 |

1 |

1 |

0 |

ИЛИ-НЕ |

|

______ y= x1+x2 |

y |

1 |

0 |

0 |

0 |

И-НЕ

|

|

_____ y= x1 ·x2

|

y |

1 |

1 |

1 |

0 |

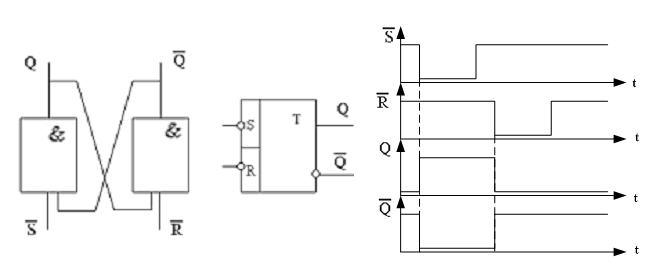

47. Асинхронные rs-триггеры на элементах и-не. Временные диаграммы.

Основой микропроцессорной техники является триггер, который имеет 2 устойчивых состояния равновесия и переходит из одного состояния в другое с помощью внешних импульсов. Триггер позволяет определить состояние в предыдущем цикле и позволяет определить состояние в текущем времени. Поэтому основной узел оперативной памяти состоит из триггеров.

Работа асинхронного триггера зависит от сигналов в информационных входах.

Асинхронные RS-триггеры на элементах И-НЕ:

Таблица перехода:

R |

S |

Qn+1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

запрещ |

1 |

1 |

Qn |

Qn+1- текущее состояние; Qn- предыдущий режим

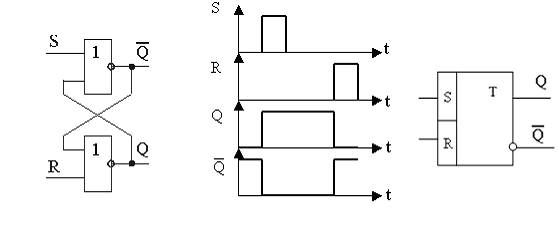

48. Асинхронные rs-триггеры на элементах или-не. Временные диаграммы.

Основой микропроцессорной техники является триггер, который имеет 2 устойчивых состояния равновесия и переходит из одного состояния в другое с помощью внешних импульсов. Триггер позволяет определить состояние в предыдущем цикле и позволяет определить состояние в текущем времени. Поэтому основной узел оперативной памяти состоит из триггеров.

Работа асинхронного триггера зависит от сигналов в информационных входах.

Асинхронные RS-триггеры на элементах ИЛИ-НЕ:

Таблица перехода:

R |

S |

Qn+1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

Qn |

1 |

1 |

запрещ |

Qn+1- текущее состояние; Qn- предыдущий режим

49. Д-триггеры.

Основой микропроцессорной техники является триггер, который имеет 2 устойчивых состояния равновесия и переходит из одного состояния в другое с помощью внешних импульсов. Триггер позволяет определить состояние в предыдущем цикле и позволяет определить состояние в текущем времени. Поэтому основной узел оперативной памяти состоит из триггеров.

Д-триггер (delay-задержка) имеет прямые или инверсные установочные входы R и S, один управляющий вход D и вход синхронизации C. Входы R и S называются установочными и служат для предварительной установки Д-триггера в состояние Q=1 или Q=0.

Сигнал на управляющем входе D=1 или D=0 устанавливает триггер в устойчивое состояние с одноимённым значением на прямом информационном выходе Q=1 или Q=0 только при одновременном действии импульса положительной полярности на входе синхронизации. Обычно переключение триггера происходит в течении времени действия переднего фронта импульса синхронизации.