- •2.3. Лабораторный практикум

- •Распределение тем лабораторных занятий по времени

- •2.3.В.1. Ознакомление с системой моделирования matlab

- •2.3.В.2. Общие рекомендации по исследованию характеристик и параметров цепей и устройств в среде ewb

- •2.3.1. Лабораторная работа № 1 Моделирование логических функций

- •1.1. Краткие теоретические сведения

- •1.2. Задание на лабораторную работу

- •2.3.2. Лабораторная работа № 2 Моделирование цифровых триггеров

- •2.1. Краткие теоретические сведения

- •2.2. Задание на лабораторную работу

- •2.3.3. Лабораторная работа № 3 Моделирование регистров

- •3.1. Краткие теоретические сведения

- •3.2. Задание на лабораторную работу

- •2.3.4. Лабораторная работа № 4 Моделирование счетчиков

- •4.1. Краткие теоретические сведения

- •4.2. Задание на лабораторную работу

- •2.3.5. Лабораторная работа № 5 Моделирование комбинационных устройств

- •5.1. Краткие теоретические сведения

- •5.2. Задание на лабораторную работу

- •2.3.6. Лабораторная работа № 6 Моделирование работы арифметико-логического устройства при выполнении операций суммирования и умножения

- •6.1. Краткие теоретические сведения

- •6.2. Задание на лабораторную работу

- •2.3.7. Лабораторная работа № 7 Моделирование работы микропроцессора при выполнении операций умножения двоичных чисел

- •7.1. Краткие теоретические сведения

- •7.2. Задание на лабораторную работу

- •2.3.8. Лабораторная работа № 8 Проектирование и моделирование цифровых устройств

- •8.1. Задание на лабораторную работу

- •12. Расскажите о параметрах и работе цифровых мультиплексоров.

- •3. Учебно-методическое обеспечение дисциплины

- •3.1. Перечень основной и дополнительной литературы

- •3.1.1. Основная литература:

- •3.1.2. Дополнительная литература:

- •3.2. Методические рекомендации преподавателю

- •3.3. Методические указания студентам по изучению дисциплины

- •3.4. Методические указания и задания для выполнения курсовой работы

- •3.4.1. Постановка задачи и цель курсовой работы

- •3.4.2. Задание 1. Расчет, анализ и синтез комбинационных схем

- •3.4.2.4. Пример выполнения задания.

- •3.4.3. Задание 2. Расчет, анализ и синтез комбинационных схем

- •3.4.2.3. Методические указания по выполнению задания 2.

- •3.4.4. Правила выполнения и оформления курсовой работы

- •Пример правильного оформления расчета

- •3.5. Учебно-методическая карта дисциплины

- •3.6. Материально-техническое обеспечение дисциплины

- •3.7. Программное обеспечение использования современных информационно-коммуникативных технологий

- •3.8. Технологическая карта дисциплины Поволжский государственный университет сервиса

2.3.2. Лабораторная работа № 2 Моделирование цифровых триггеров

Цель работы: моделирование работы цифровых триггеров; приобретение практических навыков построения и исследования различных типов триггеров.

2.1. Краткие теоретические сведения

Триггером называется устройство, способное формировать два устойчивых значения выходного сигнала (лог. 0 и лог. 1) и скачкообразно изменять эти значения под действием внешнего управляющего сигнала.

Триггеры классифицируются на несколько типов в зависимости от принципа их работы и целевого назначения.

По способу управления триггеры подразделяют на два класса: синхронизируемые и несинхронизируемые (асинхронные). Синхронизируемый триггер снабжен вспомогательным входом синхронизации, который разрешает переключение триггера при наличии на этом входе соответствующего сигнала.

По способу организации логических связей триггеры классифицируют на следующие типы: RS – с раздельной установкой состояний стояний 1 и 0; Т – со счетным входом; D – с приемом информации по одному входу; JK (универсальный) – совмещает в себе свойства D, RS и Т-триггеров (позволяет раздельную установку состояний 1 и 0, но способен при одновременном воздействии входных сигналов функционировать как Т-триггер).

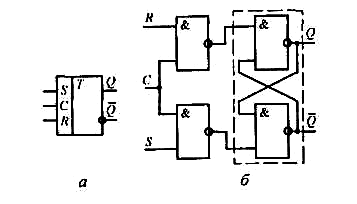

Асинхронный RS-триггер

(рис. П2.1, а)

имеет два информационных

входа, один из которых обозначают буквой

S

(от англ. set

– устанавливать),

а другой – R

(от англ. reset

– сбрасывать).

Прямой выход триггера, как отмечалось,

обозначают буквой Q,

а инверсный –

![]() .

.

Асинхронный RS-триггер можно получить на двух ЛЭ ИЛИ–НЕ, если снабдить их перекрестными положительными обратными связями, как показано на рис. П2.1, б. Временные диаграммы, поясняющие принцип работы этого триггера, приведены на рис. П2.1, в (длительностью переходных процессов при коммутациях пренебрегаем).

Как видно из рис. П2.1, б, при

подключении к входу S

лог. 1, т. е. S = 1 (момент

t1 на рис. П2.1,

в), на инверсном выходе

![]() получаем лог. 0. Поскольку этот сигнал

по цепи обратной связи подается на один

из входов верхнего элемента ИЛИ–НЕ, а

на другом его входе действует также

сигнал 0 с входа R,

имеем (Q = 1. Это

состояние триггера может сохраняться

сколь угодно долго и не зависит от

последующих изменений сигнала на входе

S, если на входе R

поддерживается состояние 0 (состояние

S = 1 и R

= 1 является для данного триггера

запрещенным, так как при этой комбинации

входных сигналов выходное состояние

триггера будет непредсказуемо). Таким

образом, RS-триггер

запоминает информацию о состоянии S

= 1 и поддерживает ее до тех пор, пока на

входе R не появится

сигнал сброса 1 (момент t2

рис. П2.1, в).

получаем лог. 0. Поскольку этот сигнал

по цепи обратной связи подается на один

из входов верхнего элемента ИЛИ–НЕ, а

на другом его входе действует также

сигнал 0 с входа R,

имеем (Q = 1. Это

состояние триггера может сохраняться

сколь угодно долго и не зависит от

последующих изменений сигнала на входе

S, если на входе R

поддерживается состояние 0 (состояние

S = 1 и R

= 1 является для данного триггера

запрещенным, так как при этой комбинации

входных сигналов выходное состояние

триггера будет непредсказуемо). Таким

образом, RS-триггер

запоминает информацию о состоянии S

= 1 и поддерживает ее до тех пор, пока на

входе R не появится

сигнал сброса 1 (момент t2

рис. П2.1, в).

|

Рис. П2.1. Асинхронный RS-триггер |

При R = 1 на выходе Q получим сигнал Q = 0, а соответствующий канал обратной связи обеспечит = 1 и т. д.

Синхронный RS-триггер, обозначаемый также буквами RST, имеет дополнительный С-вход (от англ. clock – часы), на который подают импульсы синхронизации (рис. П2.2, а). Синхронный триггер получают при подключении к входу асинхронного RS-триггера двух дополнительных элементов И–НЕ (рис. П2.2, б).

|

Рис. П2.2. Синхронный RS-триггер |

Как видно, при отсутствии сигнала на С-входе, т. е. С = 0, входы R и S оказываются отключенными от собственно триггера, и изменение сигналов на этих входах не может изменить состояние триггера. С момента появления разрешающего сигнала С = 1 входные элементы И–НЕ выполняют функцию инверторов. При этом состояние триггера будет однозначно определяться значениями сигналов на S- и R-входах по аналогии с асинхронным RS-триггером.

Следует подчеркнуть, что описанный триггер может изменять свое состояние в любой момент на интервале действия сигнала С = 1. Такой триггер называют триггером со статическим входом синхронизации.

Наибольшее практическое распространение получили триггеры с динамическим (импульсным) входом синхронизации. Суть построения такого триггера заключается в обеспечении его переключения лишь на интервале изменения сигнала входа С, т. е. либо по фронту, либо по срезу импульса синхронизации. Такое решение позволяет значительно повысить надежность и помехозащищенность триггерных устройств, так как сводит к минимуму интервал, на котором возможна перезапись информации.

Т-триггер (от англ. tumbler – опрокидыватель) находит широкое применение в счетчиках импульсов цифровых систем. В этом триггере, условное обозначение которого приведено на рис. П2.3, а, имеется один Т-вход, при каждом воздействии на который (импульсом) происходит очередное переключение триггера из одного состояния в другое. Поэтому такой прибор именуют триггером со счетным входом. Число переключений равно числу поступивших на вход импульсов.

|

Рис. П2.3. Т-триггер |

В основу большинства Т-триггеров положена схема двухступенчатого триггера, образованного последовательным соединением двух синхронных RST-триггеров, охваченных перекрестными обратными связями (рис. П2.3, б). Кроме того, С-входы этих RST-триггеров соединены между собой элементом НЕ и объединены в общий для всего T-триггера вход T. Таким образом, любое управляющее воздействие на вход С1 вызывает отключение второго RST-триггера по входной цепи. Однако за счет соединения триггера Т1 с T2 цепями обратной связи каждое принудительное переключение T1 вызывает опрокидывание T2. Принцип работы T-триггера иллюстрируют временные диаграммы процессов на T-входе и Q-выходе (рис. П2.3, в).

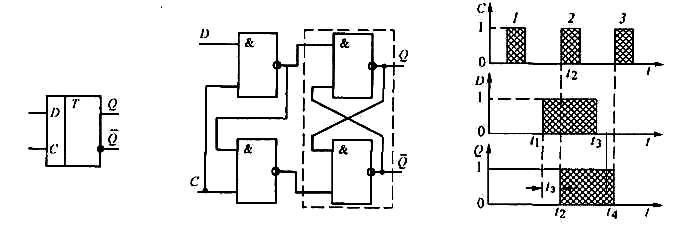

D-триггер (от англ. delay – задержка), условное обозначение которого приведено на рис. П2.4, а, формирует выходной сигнал на Q-выходе с задержкой относительно управляющего воздействия на D-входе. Для этого его снабжают С-входом, возбуждение которого (статическое или импульсное) позволяет переключать триггер в состояние, соответствующее сигналу на D-входе.

D-триггеры получают на основе RS-триггеров, используя на входе однотипные логические устройства И–НЕ (рис. П2.4, б). Временные диаграммы процессов представлены на рис. П2.4, в.

|

Рис. П2.4. D-триггер |

Универсальный JK-триггер, условное обозначение которого приведено на рис. П2.5, а, имеет три входа: два информационных (J и К) и один синхронизирующий (С). Он легко реализуется на двух RST-триггерах с обратными связями, как показано на рис. П2.5, б.

JK-триггер относят к универсальному типу, поскольку при различных вариантах переключения его входных зажимов можно получить схему триггеров всех других типов.