- •2.3. Лабораторный практикум

- •Распределение тем лабораторных занятий по времени

- •2.3.В.1. Ознакомление с системой моделирования matlab

- •2.3.В.2. Общие рекомендации по исследованию характеристик и параметров цепей и устройств в среде ewb

- •2.3.1. Лабораторная работа № 1 Моделирование логических функций

- •1.1. Краткие теоретические сведения

- •1.2. Задание на лабораторную работу

- •2.3.2. Лабораторная работа № 2 Моделирование цифровых триггеров

- •2.1. Краткие теоретические сведения

- •2.2. Задание на лабораторную работу

- •2.3.3. Лабораторная работа № 3 Моделирование регистров

- •3.1. Краткие теоретические сведения

- •3.2. Задание на лабораторную работу

- •2.3.4. Лабораторная работа № 4 Моделирование счетчиков

- •4.1. Краткие теоретические сведения

- •4.2. Задание на лабораторную работу

- •2.3.5. Лабораторная работа № 5 Моделирование комбинационных устройств

- •5.1. Краткие теоретические сведения

- •5.2. Задание на лабораторную работу

- •2.3.6. Лабораторная работа № 6 Моделирование работы арифметико-логического устройства при выполнении операций суммирования и умножения

- •6.1. Краткие теоретические сведения

- •6.2. Задание на лабораторную работу

- •2.3.7. Лабораторная работа № 7 Моделирование работы микропроцессора при выполнении операций умножения двоичных чисел

- •7.1. Краткие теоретические сведения

- •7.2. Задание на лабораторную работу

- •2.3.8. Лабораторная работа № 8 Проектирование и моделирование цифровых устройств

- •8.1. Задание на лабораторную работу

- •12. Расскажите о параметрах и работе цифровых мультиплексоров.

- •3. Учебно-методическое обеспечение дисциплины

- •3.1. Перечень основной и дополнительной литературы

- •3.1.1. Основная литература:

- •3.1.2. Дополнительная литература:

- •3.2. Методические рекомендации преподавателю

- •3.3. Методические указания студентам по изучению дисциплины

- •3.4. Методические указания и задания для выполнения курсовой работы

- •3.4.1. Постановка задачи и цель курсовой работы

- •3.4.2. Задание 1. Расчет, анализ и синтез комбинационных схем

- •3.4.2.4. Пример выполнения задания.

- •3.4.3. Задание 2. Расчет, анализ и синтез комбинационных схем

- •3.4.2.3. Методические указания по выполнению задания 2.

- •3.4.4. Правила выполнения и оформления курсовой работы

- •Пример правильного оформления расчета

- •3.5. Учебно-методическая карта дисциплины

- •3.6. Материально-техническое обеспечение дисциплины

- •3.7. Программное обеспечение использования современных информационно-коммуникативных технологий

- •3.8. Технологическая карта дисциплины Поволжский государственный университет сервиса

2.3.5. Лабораторная работа № 5 Моделирование комбинационных устройств

Цель работы: моделирование работы комбинационных устройств – цифровых шифраторов и дешифраторов, мультиплексоров и демультиплексоров.

5.1. Краткие теоретические сведения

Комбинационное устройство – это устройство с n входами и m выходами. Если данное устройство выполнено на базе идеальных, т. е. безынерционных элементов, то состояние его выходов однозначно определяется состоянием его входов в тот же момент времени.

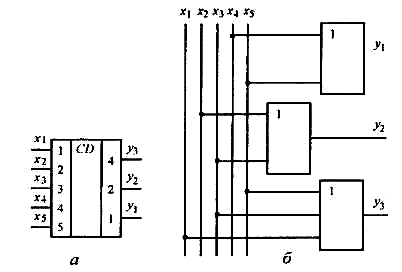

Шифратор (кодер) – логическое устройство с п входами и т выходами, преобразующее входные одиночные сигналы, соответствующие лог. 1, в m - разрядный двоичный код на выходе. Для шифратора, показанного условно на рис. П5.1, а (п =5, т = 3), задают следующую таблицу истинности (табл. П5.1).

|

Рис. П5.1. УГО шифратора (а) и его функциональная схема на элементах ИЛИ (б) |

Функциональная схема, реализующая на элементах ИЛИ приведенную в табл. П5.1 программу работы шифратора, представлена на рис. П5.1, б.

Таблица П 5.1

Сигналы на входе |

Выходной код |

|||||||

двоичный |

десятичный |

|||||||

x1 |

х2 |

х3 |

х4 |

х5 |

y1 |

y2 |

y3 |

Y(10) |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

2 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

3 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

4 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

5 |

Таблица П5.2

Входной код |

Сигналы на выходе |

|||||||

десятичный |

двоичный |

|||||||

X(10) |

х3 |

х2 |

x1 |

y0 |

y1 |

y2 |

y3 |

у4 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

2 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

3 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

4 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

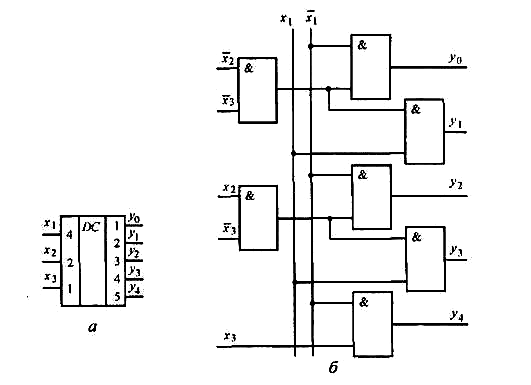

Функциональная схема дешифратора, реализующая на элементах И заданную программу (см. табл. П5.1), приведена на рис. П5.2, б.

|

Рис. П5.2. УГО дешифратора (а) и его функциональная схема на элементах И (б) |

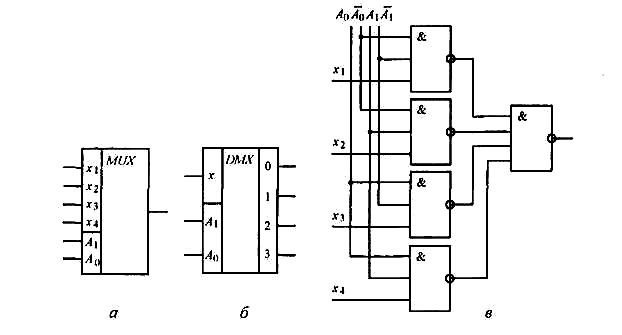

Мультиплексор – логическое устройство, предназначенное для управляемой передачи данных от нескольких входных цепей в общий выходной канал. Он снабжается двумя группами входов: адресными и информационными. Сигнал, поступающий на адресный вход мультиплексора, определяет, какой из информационных входов в данный момент подключен к его выходу. Поэтому число адресных (А) и информационных (X) входов мультиплексора связано соотношением X = 2А.

На рис. П5.3 приведены УГО мультиплексора и логическая схема, реализующая алгоритм его работы 41.

Демультиплексор – логическое устройство, предназначенное для управляемой передачи данных от одной входной цепи в несколько выходных. Принцип его действия противоположен принципу работы мультиплексора. Поэтому он кроме адресных содержит единственный информационный вход и 2А выходов. По адресному сигналу вход демультиплексора подключается к соответствующему выходу. Как следует из сказанного, по выполняемым функциям демультиплексор аналогичен дешифратору. Отличие состоит лишь в том, что по заданному адресу на выбранном выходе дешифратора появляется строго определенный сигнал, а в демультиплексоре – тот же сигнал, что и на его входе. УГО демультиплексора приведено на рис. П5.3, б.

|

Рис. П5.3. УГО мультиплексора (а) и демультиплексора (б) и логическая схема мультиплексора (в), реализующая алгоритм его работы 4 1 |

Компаратор (цифровой) – логическое устройство, обеспечивающее сравнение двух многоразрядных двоичных чисел А и В, разряды каждого из которых подаются порознь на его входы (рис. П5.3). На практике одно из чисел (например, А) является неизменным, а другое (В) изменяет свое значение от такта к такту. В момент равенства их значений на выходе компаратора формируется сигнал лог. 1.