- •2.3. Лабораторный практикум

- •Распределение тем лабораторных занятий по времени

- •2.3.В.1. Ознакомление с системой моделирования matlab

- •2.3.В.2. Общие рекомендации по исследованию характеристик и параметров цепей и устройств в среде ewb

- •2.3.1. Лабораторная работа № 1 Моделирование логических функций

- •1.1. Краткие теоретические сведения

- •1.2. Задание на лабораторную работу

- •2.3.2. Лабораторная работа № 2 Моделирование цифровых триггеров

- •2.1. Краткие теоретические сведения

- •2.2. Задание на лабораторную работу

- •2.3.3. Лабораторная работа № 3 Моделирование регистров

- •3.1. Краткие теоретические сведения

- •3.2. Задание на лабораторную работу

- •2.3.4. Лабораторная работа № 4 Моделирование счетчиков

- •4.1. Краткие теоретические сведения

- •4.2. Задание на лабораторную работу

- •2.3.5. Лабораторная работа № 5 Моделирование комбинационных устройств

- •5.1. Краткие теоретические сведения

- •5.2. Задание на лабораторную работу

- •2.3.6. Лабораторная работа № 6 Моделирование работы арифметико-логического устройства при выполнении операций суммирования и умножения

- •6.1. Краткие теоретические сведения

- •6.2. Задание на лабораторную работу

- •2.3.7. Лабораторная работа № 7 Моделирование работы микропроцессора при выполнении операций умножения двоичных чисел

- •7.1. Краткие теоретические сведения

- •7.2. Задание на лабораторную работу

- •2.3.8. Лабораторная работа № 8 Проектирование и моделирование цифровых устройств

- •8.1. Задание на лабораторную работу

- •12. Расскажите о параметрах и работе цифровых мультиплексоров.

- •3. Учебно-методическое обеспечение дисциплины

- •3.1. Перечень основной и дополнительной литературы

- •3.1.1. Основная литература:

- •3.1.2. Дополнительная литература:

- •3.2. Методические рекомендации преподавателю

- •3.3. Методические указания студентам по изучению дисциплины

- •3.4. Методические указания и задания для выполнения курсовой работы

- •3.4.1. Постановка задачи и цель курсовой работы

- •3.4.2. Задание 1. Расчет, анализ и синтез комбинационных схем

- •3.4.2.4. Пример выполнения задания.

- •3.4.3. Задание 2. Расчет, анализ и синтез комбинационных схем

- •3.4.2.3. Методические указания по выполнению задания 2.

- •3.4.4. Правила выполнения и оформления курсовой работы

- •Пример правильного оформления расчета

- •3.5. Учебно-методическая карта дисциплины

- •3.6. Материально-техническое обеспечение дисциплины

- •3.7. Программное обеспечение использования современных информационно-коммуникативных технологий

- •3.8. Технологическая карта дисциплины Поволжский государственный университет сервиса

2.3.6. Лабораторная работа № 6 Моделирование работы арифметико-логического устройства при выполнении операций суммирования и умножения

Цель работы: моделирование работы арифметико-логического устройства при выполнении простейших арифметических операций – суммирования и умножения.

6.1. Краткие теоретические сведения

Арифметико-логическое устройство (АЛУ) – это многофункциональное устройство, которое выполняет над входными числами различные арифметические и логические операции. УГО АЛУ приведено на рис. П.6.1.

|

Рис. П6.1. УГО арифметико-логического устройства |

Назначение АЛУ – обработка информации (операции +, –, <<, >>, и т. д.) и логические операции.

Структура АЛУ для сложения и вычитания чисел с фиксированной запятой. При выполнении сложения положительные слагаемые представляются в прямом коде, отрицательные – в дополнительном. Производится сложение двоичных кодов, включая разряды знаков. Если при этом возникает перенос из знакового разряда суммы при отсутствии переноса в этот разряд или перенос в знаковый разряд при отсутствии переноса из разряда знака, то имеется переполнение разрядной сетки соответственно при отрицательной и положительной суммах. Если нет переносов из знакового разряда и в знаковый разряд суммы или есть оба этих переноса, то переполнения нет и при 0 в знаковом разряде сумма положительна, а при 1 отрицательна и представлена в ДК.

Структура АЛУ для умножения чисел с фиксированной запятой (сумматор частичных произведений). В ЭВМ операция умножения чисел с фиксированной запятой с помощью соответствующих алгоритмов сводится к операциям сложения и сдвига. Произведение двух (n–1)-разрядных чисел может иметь 2(n–1) значащих разрядов. Т. о. при операции умножения целых чисел необходимо предусмотреть возможность формирования в АЛУ произведения, имеющего двойную по сравнению с сомножителем длину. В ЭВМ, в которых числа с фиксированной запятой являются дробями, младшие n–1 разрядов произведения часто отбрасываются (возможно, с операцией округления).

Для выполнения умножения АЛУ должно содержать регистры множимого, множителя и схемы формирования суммы частичных произведений – сумматор частичных произведений, в котором путем соответствующей организации передач производится последовательное суммирование частичных произведений.

Операция умножения состоит из n–1 [(n–1) – число цифровых разрядов множителя] циклов. В каждом цикле анализируется очередная цифра множителя, и если это 1, то к сумме частичных произведений прибавляется множимое, в противном случае прибавления не происходит. Цикл завершается сдвигом множимого относительно суммы частичных произведений либо сдвигом суммы частичных произведений относительно неподвижного множимого.

6.2. Задание на лабораторную работу

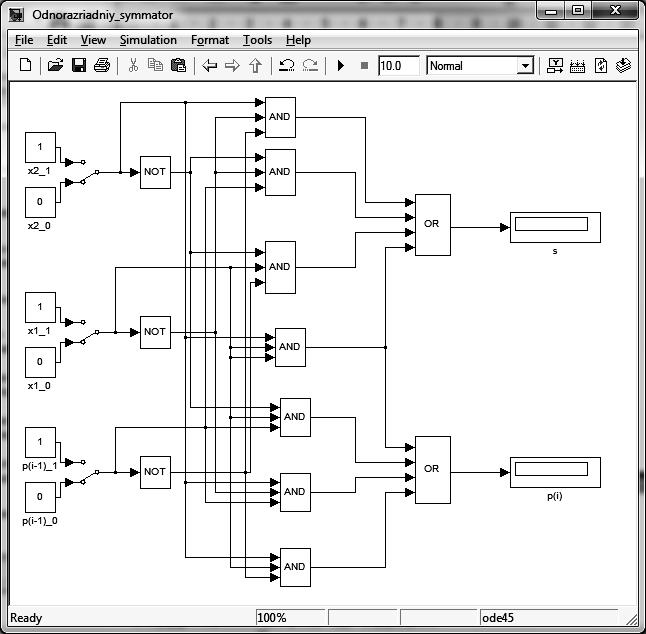

1. Смоделировать работу одноразрядного сумматора, схема которого представлена на рис. П6.2.

|

Рис. П6.2.Схема моделирования одноразрядного сумматора |

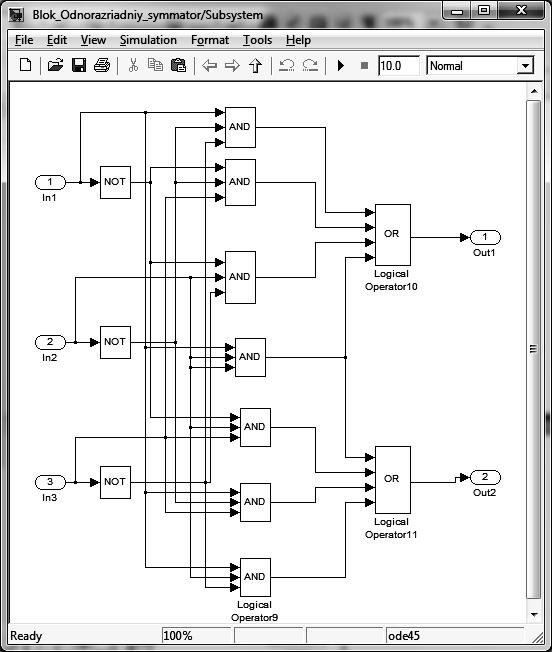

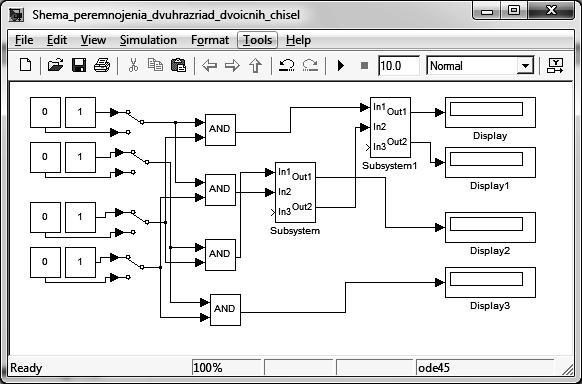

2. Создать блок одноразрядного сумматора в соответствии с рис. П6.3, и на его основе смоделировать схему перемножения двухразрядных двоичных чисел, представленную на рис. П6.4.

|

Рис. П6.3. Блок одноразрядного сумматора |

Контрольные вопросы

1. Можно ли с помощью АЛУ умножить операнд на 2?

2. Какие из операций являются важнейшими для АЛУ?

3. Для чего в АЛУ используются дополнительные регистры?

4. Какие основные выводы АЛУ вам известны и для чего они используются?

5. Что означает понятие «аккумулятор» в АЛУ?

6. В каком случае АЛУ использует один входной порт? Два входных порта?

7. Перечислите операции, выполняемые АЛУ всех типов.

8. В чем отличие элементарных операций от микропрограммных?

9. АЛУ относятся к последовательностным или комбинационным устройствам? Почему?

|

Рис. П6.4. Схема перемножения двухразрядных двоичных чисел |