- •2.3. Лабораторный практикум

- •Распределение тем лабораторных занятий по времени

- •2.3.В.1. Ознакомление с системой моделирования matlab

- •2.3.В.2. Общие рекомендации по исследованию характеристик и параметров цепей и устройств в среде ewb

- •2.3.1. Лабораторная работа № 1 Моделирование логических функций

- •1.1. Краткие теоретические сведения

- •1.2. Задание на лабораторную работу

- •2.3.2. Лабораторная работа № 2 Моделирование цифровых триггеров

- •2.1. Краткие теоретические сведения

- •2.2. Задание на лабораторную работу

- •2.3.3. Лабораторная работа № 3 Моделирование регистров

- •3.1. Краткие теоретические сведения

- •3.2. Задание на лабораторную работу

- •2.3.4. Лабораторная работа № 4 Моделирование счетчиков

- •4.1. Краткие теоретические сведения

- •4.2. Задание на лабораторную работу

- •2.3.5. Лабораторная работа № 5 Моделирование комбинационных устройств

- •5.1. Краткие теоретические сведения

- •5.2. Задание на лабораторную работу

- •2.3.6. Лабораторная работа № 6 Моделирование работы арифметико-логического устройства при выполнении операций суммирования и умножения

- •6.1. Краткие теоретические сведения

- •6.2. Задание на лабораторную работу

- •2.3.7. Лабораторная работа № 7 Моделирование работы микропроцессора при выполнении операций умножения двоичных чисел

- •7.1. Краткие теоретические сведения

- •7.2. Задание на лабораторную работу

- •2.3.8. Лабораторная работа № 8 Проектирование и моделирование цифровых устройств

- •8.1. Задание на лабораторную работу

- •12. Расскажите о параметрах и работе цифровых мультиплексоров.

- •3. Учебно-методическое обеспечение дисциплины

- •3.1. Перечень основной и дополнительной литературы

- •3.1.1. Основная литература:

- •3.1.2. Дополнительная литература:

- •3.2. Методические рекомендации преподавателю

- •3.3. Методические указания студентам по изучению дисциплины

- •3.4. Методические указания и задания для выполнения курсовой работы

- •3.4.1. Постановка задачи и цель курсовой работы

- •3.4.2. Задание 1. Расчет, анализ и синтез комбинационных схем

- •3.4.2.4. Пример выполнения задания.

- •3.4.3. Задание 2. Расчет, анализ и синтез комбинационных схем

- •3.4.2.3. Методические указания по выполнению задания 2.

- •3.4.4. Правила выполнения и оформления курсовой работы

- •Пример правильного оформления расчета

- •3.5. Учебно-методическая карта дисциплины

- •3.6. Материально-техническое обеспечение дисциплины

- •3.7. Программное обеспечение использования современных информационно-коммуникативных технологий

- •3.8. Технологическая карта дисциплины Поволжский государственный университет сервиса

2.3.8. Лабораторная работа № 8 Проектирование и моделирование цифровых устройств

Цель работы: изучение и исследование последовательных двоичных счетчиков на основе D-триггеров, проектирование и моделирование устройства формирования импульсов; проектирование и моделирование цифровых устройств с применением счетчиков с произвольным коэффициента пересчета на базе JK-триггеров; проектирование и моделирование цифровых устройств на микросхемах средней интеграции.

8.1. Задание на лабораторную работу

1. Проектирование цифрового устройства (ЦУ) с трехразрядным двоичным счетчиком на база D-триггеров.

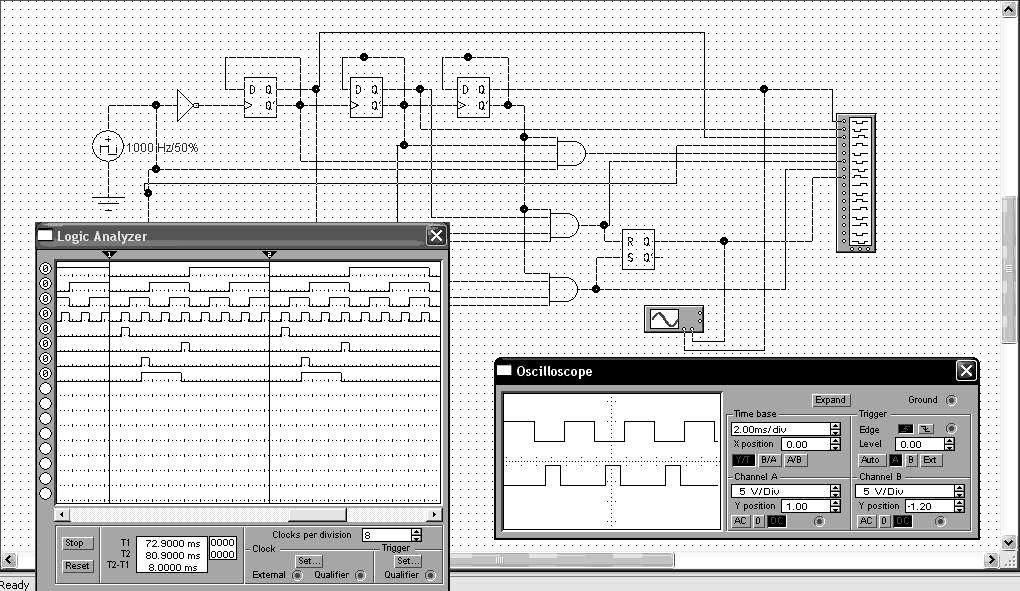

Схема ЦУ синхронизации на основе последовательного двоичного счетчик на D-триггерах имеет вид, представленный на рис. П8.1. Устройство содержит трехразрядный двоичный счетчик, дешифраторы импульсов, RS-триггер. В качестве устройств отображения параметров импульсов (временных диаграмм) использован логический анализатор на 8 входов и двулучевой осциллограф. Осциллограф необходим для проверки сигналов на наличие «паразитных» импульсов, так как логический анализатор не может их обнаружить.

Используя органы управления логического анализатора и осциллографа можно измерить параметры сигналов: амплитуду, длительность, период и задержки их относительно друг друга.

|

Рис. П8.1. ЦУ синхронизации на основе последовательного двоичного счетчик на D-триггерах |

Для каждого студента преподавателем выдается временная диаграмма для четырех импульсов Т1, Т2, Т3, Т4. Период для всех четырех импульсов одинаков и равен 8 периодам тактовой частоты генератора (16 временным интервалам). Задания представлены в табл. 8.1 по вариантам.

Каждый из вариантов содержит временные диаграммы четырех выходных импульсов устройства. Временные диаграммы закодированы двоичным 16-разрядным кодом. Наличие единицы в разряде кода соответствует уровню лог. 1 в соответствующем временном интервале, наличие нуля соответствует уровню лог. 0 в соответствующем временном интервале. На рис. П8.2 представлены временные диаграммы для кода 1101100100110000.

|

Рис. П8.2. Временные диаграммы импульсов генератора и выходного импульса с кодом 1101100100110000 |

Для моделирования необходимо использовать схему последовательного трехразрядного двоичного счетчика на базе D-триггеров, а также генератор тактовых импульсов. В качестве устройств отображения использовать логический анализатор и двулучевой осциллограф.

Схему формирования импульсов, состоящую из дешифраторов на ЛЭ и RS-триггеров, а также других ЦУ разрабатывается каждым студентом самостоятельно по заданным временным диаграммам.

Таблица П8.1

№ варианта |

Параметры выходных импульсов |

№ варианта |

Параметры выходных импульсов |

1 |

Т1 – 1000000000000000 Т2 – 0110000000000000 Т3 – 0101000000000000 Т4 – 0111100000000000 |

19 |

Т1 – 0000000011111111 Т2 – 0000000110000000 Т3 – 0000011000000000 Т4 – 0000100001000000 |

2 |

Т1 – 0110000000000000 Т2 – 0001000000000000 Т3 – 1110011111111111 Т4 – 0000000011100000 |

20 |

Т1 – 0011100000000000 Т2 – 0001110000000000 Т3 – 0000111000000000 Т4 – 0000011100000000 |

3 |

Т1 – 0001111000000000 Т2 – 0010000100000000 Т3 – 0000110000000000 Т4 – 0111001110000000 |

21 |

Т1 – 1000000000000001 Т2 – 1100000000000011 Т3 – 1110000000000111 Т4 – 1111000000001111 |

4 |

Т1 – 0000000001100000 Т2 – 0001100000000000 Т3 – 0000011000000000 Т4 – 0000000111000000 |

22 |

Т1 – 0101000000000000 Т2 – 0010100000000000 Т3 – 0001100110000000 Т4 – 0000011111100000 |

5 |

Т1 – 0011000000000000 Т2 – 0000111000000000 Т3 – 0010000010000000 Т4 – 0001000100000000 |

23 |

Т1 – 0000000000011000 Т2 – 0000000000100100 Т3 – 0000000001000010 Т4 – 0000000010000001 |

6 |

Т1 – 0000000000000010 Т2 – 0000000000000100 Т3 – 0000000000001000 Т4 – 0000000000010000 |

24 |

Т1 – 1011111111111111 Т2 – 0111000000000000 Т3 – 1111100011111111 Т4 – 0000001000000000 |

7 |

Т1 – 0000000000000011 Т2 – 0000000000001100 Т3 – 0000000000110000 Т4 – 0000000011000000 |

25 |

Т1 – 0000011100000000 Т2 – 0000001000000000 Т3 – 0000100010000000 Т4 – 0001000001000000 |

8 |

Т1 – 0000000100000000 Т2 – 0000001110000000 Т3 – 0000010001000000 Т4 – 0000110001100000 |

26 |

Т1 – 1000000000000001 Т2 – 0000000000000010 Т3 – 0000000000000100 Т4 – 0000000000001000 |

9 |

Т1 – 0010000000000000 Т2 – 0001000000000000 Т3 – 0000100000000000 Т4 – 0000011000000000 |

27 |

Т1 – 0000000000000111 Т2 – 1100000000000000 Т3 – 0011000000000000 Т4 – 0000110000000000 |

10 |

Т1 – 1110000000000000 Т2 – 0001110000000000 Т3 – 0000001110000000 Т4 – 0000000001110000 |

28 |

Т1 – 1010000000000000 Т2 – 0101000000000000 Т3 – 0010100000000000 Т4 – 0001010000000000 |

11 |

Т1 – 0000000000001000 Т2 – 0000000000000100 Т3 – 0000000000010000 Т4 – 0000001110000000 |

29 |

Т1 – 1110000000000000 Т2 – 0001110000000000 Т3 – 0000001110000000 Т4 – 0000000001110000 |

12 |

Т1 – 0000011100000000 Т2 – 0110000000000000 Т3 – 0011100000000000 Т4 – 0000000011100000 |

30 |

Т1 – 0000000000001110 Т2 – 1100000000000001 Т3 – 0011100000000000 Т4 – 0000011100000000 |

13 |

Т1 – 0000000010000000 Т2 – 0000000101000000 Т3 – 0000001000100000 Т4 – 0000011111110000 |

31 |

Т1 – 0000000010000000 Т2 – 0000000101000000 Т3 – 0000001000100000 Т4 – 0000010000010000 |

14 |

Т1 – 1100000000000000 Т2 – 0011100000000000 Т3 – 0000010000000000 Т4 – 0000001000000000 |

32 |

Т1 – 0000000011000000 Т2 – 0000001101100000 Т3 – 0000011000110000 Т4 – 0000110000011000 |

15 |

Т1 – 0000000110000000 Т2 – 0000000001100000 Т3 – 0000000000011000 Т4 – 0000000000000110 |

33 |

Т1 – 0000001000000000 Т2 – 0000010100000000 Т3 – 0000111110000000 Т4 – 0001000001000000 |

16 |

Т1 – 0000000000000001 Т2 – 0000000000000011 Т3 – 0000000000000111 Т4 – 0000000000001111 |

34 |

Т1 – 0110000000000000 Т2 – 1001000000000000 Т3 – 0000111000000000 Т4 – 0000000111000000 |

17 |

Т1 – 0000100000000000 Т2 – 0000011000000000 Т3 – 0011000000000000 Т4 – 0001110000000000 |

35 |

Т1 – 0000000000111000 Т2 – 0000000000000111 Т3 – 1100000000000000 Т4 – 0011000000000000 |

18 |

Т1 – 1000000000000000 Т2 – 1100000000000000 Т3 – 1110000000000000 Т4 – 1111000000000000 |

36 |

Т1 – 0000100010000000 Т2 – 0000010100000000 Т3 – 0000001000000000 Т4 – 0000011100000000 |

2. Проектирование цифрового устройства (ЦУ) с произвольным коэффициентом пересчета счетчика на базе JK-триггеров.

Задания к лабораторной работе представлены в табл. П8.2. Для каждого варианта указаны параметры выходных импульсов Т1, Т2, Т3, Т4 ЦУ – период Тп, длительность Т и задержка Тs относительно первого импульса Т1 и активный уровень (полярность импульса). Параметры импульсов указаны в периодах частоты генератора.

Таблица П8.2

№ вар. |

Тs |

Т |

Тп |

Акт. уровень |

№ вар. |

Тs |

Т |

Тп |

Акт. уровень |

1 |

0 1 2 3 |

2 3 4 5 |

17 |

1 1 1 0 |

16 |

0 2 3 5 |

1 2 3 4 |

34 |

1 1 1 0 |

2 |

0 2 4 5 |

6 7 8 9 |

18 |

1 0 0 1 |

17 |

0 6 5 6 |

5 6 7 8 |

35 |

0 0 1 1 |

3 |

0 3 5 1 |

4 3 2 1 |

19 |

0 1 0 1 |

18 |

0 6 6 7 |

9 8 7 6 |

36 |

1 1 1 0 |

4 |

0 2 3 5 |

3 2 4 5 |

20 |

1 1 0 0 |

19 |

0 8 9 9 |

5 4 3 2 |

37 |

0 1 0 1 |

5 |

0 1 4 5 |

5 6 4 7 |

22 |

0 0 1 1 |

20 |

0 9 8 7

|

1 3 5 7 |

38 |

1 1 1 0 |

6 |

0 1 3 4 |

4 5 6 7 |

23 |

1 1 1 0 |

21 |

0 9 5 4 |

9 7 5 3 |

39 |

1 1 0 0 |

7 |

0 4 3 2 |

8 9 5 4 |

24 |

1 0 0 1 |

22 |

0 2 3 4 |

1 2 4 6 |

40 |

0 1 1 0 |

8 |

0 1 3 2 |

7 2 1 4 |

25 |

0 1 0 1 |

23 |

0 5 6 7 |

8 7 5 4 |

41 |

1 1 0 0 |

9 |

0 6 5 4 |

5 8 9 5 |

26 |

1 1 0 0 |

24 |

0 9 6 5 |

2 3 4 6 |

42 |

0 0 1 1 |

10 |

0 6 4 3 |

9 8 4 3 |

27 |

0 0 1 1 |

25 |

0 9 8 7 |

8 7 6 5 |

43 |

1 0 1 0 |

11 |

0 3 5 4 |

3 2 1 4 |

28 |

1 1 1 0 |

26 |

0 4 5 3 |

9 6 4 3 |

44 |

1 1 0 0 |

12 |

0 3 6 7 |

5 7 6 3 |

29 |

0 1 1 0 |

27 |

0 3 4 5 |

3 4 5 7 |

45 |

1 1 0 0 |

13 |

0 1 6 2 |

8 9 6 7 |

30 |

1 1 0 0 |

28 |

0 7 7 6 |

3 2 5 4 |

46 |

1 1 0 1 |

14 |

0 2 1 5 |

2 3 4 4 |

31 |

0 0 1 1 |

29 |

0 2 3 4 |

7 8 6 5 |

47 |

1 0 1 0 |

15 |

0 6 5 7 |

4 5 7 8 |

33 |

1 0 1 0 |

30 |

0 6 7 8 |

9 3 2 1 |

48 |

1 1 0 0 |

Необходимо разработать схему ЦУ синхронизации, состоящего из последовательного счетчика на JK-триггерах, логических схем, дешифраторов и других цифровых устройств, формирующих выходные импульсы. Провести моделирование и представить результаты в виде временных диаграмм выходных импульсов, полученные логическим анализатором и осциллографом. Пример моделирования представлен на рис. П8.4, а на рис. П8.3 представлена панель логического анализатора Logic Analyzer с характерными сигналами моделируемого устройства.

|

Рис. П8.3. Панель логического анализатора Logic Analyzer при исследовании ЦУ синхронизации на базе JK-триггеров |

|

Рис. П8.4. Моделируемое ЦУ синхронизации на базе JK-триггеров |

3. Проектирование ЦУ синхронизации на логических МС средней интеграции.

Необходимо разработать схему ЦУ, формирующего импульсы, параметры которых (период, длительность, задержка, активный уровень) представлены в табл. П8.2.

В соответствии с заданным вариантом произвести синтез ЦУ синхронизации. На рис. П8.6. представлен пример схемы аналогичного устройства и результаты его моделирования. Устройства содержит 8-ми разрядный двоичный счетчик на двух микросхемах 7493 (аналог К155ИЕ5), в качестве дешифратора использованы две микросхемы 74154 (дешифратор 4×16), а также применены логические микросхемы 2–ИЛИ–НЕ и RS-триггер. Коэффициент пересчета счетчика равен (12×16 + 2) = 194. На рисунке приведена одна из возможных реализаций ЦУ. На рис. П8.5 представлена панель логического анализатора Logic Analyzer с характерными сигналами моделируемого устройства.

|

Рис. П8.5. Панель логического анализатора Logic Analyzer при исследовании ЦУ синхронизации на базе логических МС средней интеграции |

Допускаются любые другие реализации, которые могут быть отмоделированы в EWB.

Контрольные вопросы

1. Расскажите о работе схемы сравнения.

2. Расскажите о работе цифровых компараторов.

3. Расскажите о работе шинных формирователей.

4. Расскажите о работе кольцевых сдвиговых регистров.

5. Расскажите о работе шифраторов и дешифраторов кодов.

6. Расскажите о функционировании JK-триггера в режиме D-триггера.

7. Расскажите о недостатках счетчиков с последовательным переносом.

8. Расскажите о функционировании и составе двоичных сумматоров.

9. Расскажите о работе счетчиков с произвольным коэффициентом пересчета.

10. Расскажите о функционирование D-триггера в счетном режиме.

11. Расскажите о работе схемы счетчика с параллельным переносом на JK-триггерах.