- •2.3. Лабораторный практикум

- •Распределение тем лабораторных занятий по времени

- •2.3.В.1. Ознакомление с системой моделирования matlab

- •2.3.В.2. Общие рекомендации по исследованию характеристик и параметров цепей и устройств в среде ewb

- •2.3.1. Лабораторная работа № 1 Моделирование логических функций

- •1.1. Краткие теоретические сведения

- •1.2. Задание на лабораторную работу

- •2.3.2. Лабораторная работа № 2 Моделирование цифровых триггеров

- •2.1. Краткие теоретические сведения

- •2.2. Задание на лабораторную работу

- •2.3.3. Лабораторная работа № 3 Моделирование регистров

- •3.1. Краткие теоретические сведения

- •3.2. Задание на лабораторную работу

- •2.3.4. Лабораторная работа № 4 Моделирование счетчиков

- •4.1. Краткие теоретические сведения

- •4.2. Задание на лабораторную работу

- •2.3.5. Лабораторная работа № 5 Моделирование комбинационных устройств

- •5.1. Краткие теоретические сведения

- •5.2. Задание на лабораторную работу

- •2.3.6. Лабораторная работа № 6 Моделирование работы арифметико-логического устройства при выполнении операций суммирования и умножения

- •6.1. Краткие теоретические сведения

- •6.2. Задание на лабораторную работу

- •2.3.7. Лабораторная работа № 7 Моделирование работы микропроцессора при выполнении операций умножения двоичных чисел

- •7.1. Краткие теоретические сведения

- •7.2. Задание на лабораторную работу

- •2.3.8. Лабораторная работа № 8 Проектирование и моделирование цифровых устройств

- •8.1. Задание на лабораторную работу

- •12. Расскажите о параметрах и работе цифровых мультиплексоров.

- •3. Учебно-методическое обеспечение дисциплины

- •3.1. Перечень основной и дополнительной литературы

- •3.1.1. Основная литература:

- •3.1.2. Дополнительная литература:

- •3.2. Методические рекомендации преподавателю

- •3.3. Методические указания студентам по изучению дисциплины

- •3.4. Методические указания и задания для выполнения курсовой работы

- •3.4.1. Постановка задачи и цель курсовой работы

- •3.4.2. Задание 1. Расчет, анализ и синтез комбинационных схем

- •3.4.2.4. Пример выполнения задания.

- •3.4.3. Задание 2. Расчет, анализ и синтез комбинационных схем

- •3.4.2.3. Методические указания по выполнению задания 2.

- •3.4.4. Правила выполнения и оформления курсовой работы

- •Пример правильного оформления расчета

- •3.5. Учебно-методическая карта дисциплины

- •3.6. Материально-техническое обеспечение дисциплины

- •3.7. Программное обеспечение использования современных информационно-коммуникативных технологий

- •3.8. Технологическая карта дисциплины Поволжский государственный университет сервиса

2.3.7. Лабораторная работа № 7 Моделирование работы микропроцессора при выполнении операций умножения двоичных чисел

Цель работы: моделирование работы микропроцессора при выполнении операции умножения двоичных чисел.

7.1. Краткие теоретические сведения

Микропроцессор (МП), иначе, центральный процессор – Central Processing Unit (CPU) – функционально законченное программно-управляемое устройство обработки информации, выполненное в виде одной или нескольких больших (БИС) или сверхбольших (СБИС) интегральных схем.

Из арифметических операций микропроцессор (МП) выполняет только сложение и вычитание над байтами в двоичном и двоично-десятичном формате.

Умножение. Умножение двух 8-битных чисел без знака может быть выполнено несколькими способами. Например, путём повторного сложения либо применения операции регистрового сдвига. Повторное сложение обеспечивает простейшую, но самую медленную форму умножения. Например, произведение 20Н*30АН может быть получено путём прибавления 20Н к аккумулятору (предварительно обнулённому) 3А раз.

Используя операцию сдвига, можно получить более быстрое умножение. Отметим ещё особенность умножения двоичных чисел. При умножении множителя на соответствующий разряд множителя будет получен либо множитель, либо нуль.

Итак, алгоритм умножения будет включать в себя следующие операции:

1. Проверка бита множителя, начиная с младшего разряда; если 1, то прибавить множимое к старшему байту промежуточного результата (при проверке самого младшего бита множителя значение промежуточного результата равно нулю); если бит множителя равен нулю, то переход к пункту 2;

2. Сдвиг всего 2-байтового промежуточного результата вправо на 1 бит.

Повторение п. 1 и 2, необходимо производить до тех пор, пока не будут проверены все восемь бит множителя.

7.2. Задание на лабораторную работу

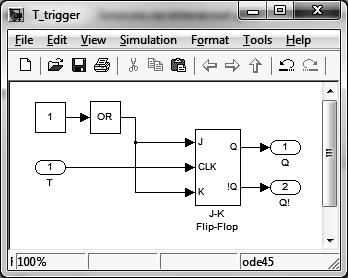

1. Собрать схему двухразрядного двоичного счетчика (рис. П7.1) на основе Т-триггеров (рис. П7.2) и сохранить ее в виде подсистемы счетчика. Можно использовать схемы моделирования предыдущих лабораторных работ.

|

Рис. П7.1. Схема моделирования двухразрядного двоичного счетчика |

|

Рис. П7.2. Т-триггер |

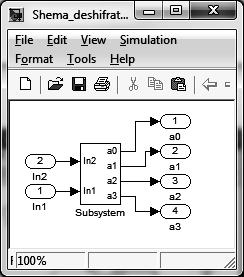

2. Собрать схему дешифратора (рис П7.3) и сохранить ее в виде подсистемы (рис. П 7.4).

|

Рис. П.7.3. Схема дешифратора |

|

Рис. П7.4. Подсистема дешифратора |

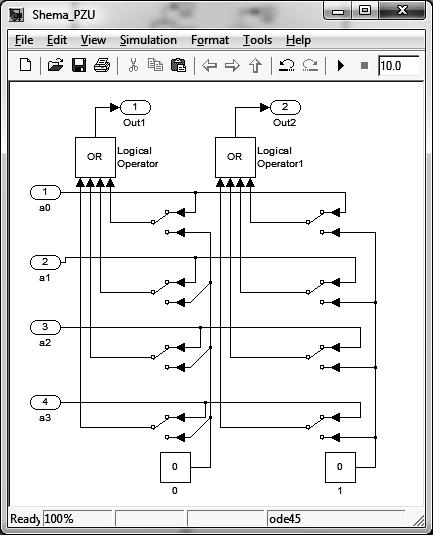

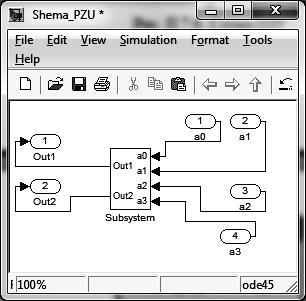

3. Собрать схему моделирования репрограммируемого постоянного запоминающего устройства РПЗУ 4×2 (в нем может храниться 4 двухразрядных двоичных числа) на рис. П7.5 и сохранить его в виде подсистемы (рис. П7.6). В схеме ПЗУ хранение логической единицы моделируется верхним положением ключа, хранение логического нуля – нижним положением ключа.

|

Рис. П7.5. Схема ПЗУ |

|

Рис. П7.6. Подсистема ПЗУ |

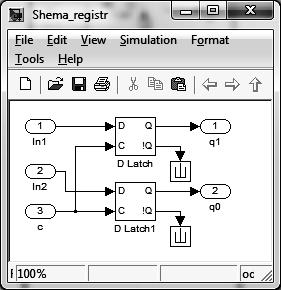

4. Собрать схему моделирования двухразрядного регистра (рис. П7.7) и сохранить ее в виде подсистемы (рис. П7.8).

|

Рис. П 7.7. Схема регистра |

|

Рис. П7.8. Подсистема регистра |

5. Собрать схему умножения двухразрядных двоичных чисел (рис. П7.9) и сохранить ее в виде подсистемы (рис. П7.10).

6. Записать в элементы ПЗУ двоичные числа, получить результаты их перемножения и занести их в табл. П7.1.

Таблица П7.1

y1 |

y0 |

x1 |

x0 |

M3 |

М2 |

M1 |

М0 |

0 0 1 1 |

0 1 0 1 |

1 1 1 1 |

1 1 1 1 |

|

|

|

|

|

Рис. П7.9. Схема блока умножения двухразрядных двоичных чисел |

|

Рис. П7.10. Подсистема блока умножения |

|

Рис. П7.11 Схема МП для перемножения двухразрядных двоичных чисел |

7. Получить осциллограммы сигналов С, Q1, Q0, A3, A2, A1, A0, y1, y0, x1, x0, M3, M2, M1, M0 и занести их в отчет.

Контрольные вопросы

1. Назовите, какие функциональные узлы необходимы для построения системы микропроцессора, перемножающего двухразрядные двоичные числа.

2. На каких элементах построено РПЗУ, применяемое в настоящей лабораторной работе?