- •Однокристальная микроЭвм

- •Содержание

- •1. Введение.

- •1.1 Характеристики.

- •1.2 Общее описание.

- •1.3 Программная модель.

- •1.4 Характеристики представителей семейства mc68hc11.

- •2. Описание сигналов и режимы работы.

- •2.1 Описание выводов.

- •2.1.1 Выводы питания (vdd) и земли (vss).

- •2.1.2 Сброс (reset/).

- •2.1.3 Входы внешней синхронизации (xtal и extal).

- •2.1.4 Вывод тактовой частоты синхронизации e (e).

- •2.1.5 Запрос прерывания (irq/).

- •2.1.6 Немаскируемое прерывание (xirq/).

- •2.1.7 Выводы moda/lir/ и modb/vstby.

- •2.1.8 Опорные напряжения ацп (vrLи vrh).

- •2.1.9 Строб b и чтение/запись (strb / r/w/).

- •2.1.10 Строб a и строб адреса (stra/as)

- •2.1.11 Сигналы портов.

- •2.2 Режимы работы.

- •2.2.1 Однокристальный режим.

- •2.2.2 Расширенный режим.

- •2.3 Специальный режим загрузки.

- •Примечание

- •Примечание

- •2.2.4 Дополнительные опции загрузчика программ.

- •2.2.5 Специальный режим теста.

- •3. Внутренняя память.

- •3.1 Карта памяти.

- •3.2 Озу и регистр отображения памяти (init).

- •3.5 Эсппзу.

- •3.5.1 Регистр управления эсппзу (pprog).

- •3.5.2 Регистр защиты эсппзу (bprot).

- •3.5.3 Программирование/стирание внутреннего эсппзу.

- •3.5.4 Регистр конфигурации системы (config).

- •Примечание: в этот момент недопустим сброс контроллера!!!

- •4. Параллельный ввод/вывод.

- •4.1 Порты ввода/вывода общего назначения (c и d).

- •4.2 Порты с фиксированным направлением ввода/вывода (a, b и e).

- •4.3 Простой стробируемый ввод/вывод.

- •4.3.1 Стробируемый ввод-порт c.

- •4.3.2 Стробируемый вывод-порт b.

- •4.4 Ввод/вывод с полным квитированием установления связи.

- •4.4.1 Протокол режима ввода с полным квитированием установления связи.

- •4.4.2 Протокол режима вывода с полным квитированием установления связи.

- •4.5 Регистр управления вводом/выводом (pioc).

- •5. Последовательный интерфейс связи (sci).

- •5.3 Особенности при работе в системах с несколькими приемниками.

- •5.4 Принимаемые данные (RxD).

- •5.5 Распознавание старт-бита.

- •5.6 Передаваемые данные (TxD).

- •5.7 Фунциональное описание.

- •5.8 Регистры sci.

- •5.8.1 Регистр данных последовательной связи (scdr).

- •5.8.2 Регистр управления 1 (sccr1).

- •5.8.3 Регистр управления 2 (sccr2).

- •5.8.4 Регистр статуса последовательной связи (scsr).

- •5.8.5 Регистр скорости приема/передачи (baud).

- •Примечание

- •Примечание

- •6. Последовательный периферийный интерфейс.

- •6.1 Общий обзор и характеристики.

- •6.2 Описание сигналов spi.

- •6.2.1 Вход ведущего-выход ведомого (miso).

- •6.2.2 Выход ведущего-вход ведомого (mosi).

- •6.2.3 Сигналы синхронизации (sck).

- •6.2.4 Выбор ведомого устройства (ss/).

- •6.3 Функциональное описание.

- •6.4 Регистры spi.

- •6.4.1 Регистр управления периферийным интерфейсом (spcr).

- •6.4.2 Регистр статуса поеледовательного периферийного интерфейса (spsr).

- •6.4.3 Регистр ввода/вывода spi.

- •7. Аналого-цифровой преобразователь.

- •7.1 Процесс преобразования.

- •7.2 Назначение каналов.

- •7.4 Работа в многоканальном режиме.

- •7.5 Работа в режимах stop и wait.

- •7.6 Регистр управления и статуса ацп (adctl).

- •Примечание:

- •Примечание:

- •7.7 Регистры результатов преобразований 1,2,3 и 4 (adr1, adr2, adr3 и adr4).

- •7.8 Подача питания на ацп и выбор источника синхронизации.

- •8. Программируемый таймер, прерывания реального времени и счетчик импульсов.

- •8.1 Программируемый таймер.

- •8.1.1 Счетчик.

- •8.1.2 Входная фиксация.

- •8.1.3 Выходное сравнение.

- •8.1.4 Управление вводом/выводом выходного сравнения 1.

- •8.1.5 Регистр принудительного сравнения таймера (cforc).

- •8.1.6 Регистр 1 маскирования выходного сравнения (oc1m).

- •8.1.7 Регистр данных выходного сравнения 1 (oc1d).

- •8.1.8 Регистр 1 управления таймером (tctl1).

- •8.1.9 Регистр 2 управления таймером (tctl2).

- •8.1.10 Регистр 1 маскирования прерываний таймера (tmsk1).

- •Примечание:

- •8.1.11 Регистр 1 флагов прерывания таймера (tflg1).

- •Примечание:

- •8.1.12 Регистр 2 маскирования прерываний таймера (tmsk2).

- •8.1.13 Регистр 2 флагов прерываний таймера (tflg2).

- •8.2 Прерывания реального времени.

- •8.3 Счетчик импульсов.

- •8.4 Регистр управления счетчиком импульсов (pactl).

- •9. Сброс, прерывания и режимы с пониженным потреблением энергии.

- •9.1 Варианты сброса.

- •9.1.1 Внешний вывод reset/.

- •9.1.2 Сброс при включении питания.

- •9.1.3 Сброс, вызываемый системой слежения.

- •9.1.4 Сброс тактового монитора.

- •9.1.5 Регистр выбора конфигурации (option).

- •9.2 Прерывания.

- •9.2.1 Программное прерывание (swi).

- •Примечание

- •9.2.2 Прерывание по неверному коду команды.

- •9.2.3 Биты маскирования прерываний регистра условий.

- •9.2.4 Структура приоритетов.

- •9.2.5 Регистр наивысшего приоритета I-прерывания (hprio).

- •9.3 Режимы пониженного энергопотребления.

- •9.3.1 Команда wait.

- •9.3.2 Команда stop.

- •10. Центральный процессор, режимы адресации и система команд.

- •10.1 Регистры цп.

- •10.1.1 Аккумуляторы a и b.

- •10.2 Режимы адресации.

- •10.2.1 Непосредственная адресация.

- •10.2.2 Прямая адресация.

- •10.2.3 Расширенная адресация.

- •10.2.4 Индексная адресация.

- •10.2.5 Неявная адресация.

- •10.2.6 Относительная адресация.

- •10.2.7 Байт префикса.

- •10.3 Система команд.

- •11. Электрические характеристики.

- •11.1 Максимальные диапазоны.

- •11.2 Температурные характеристики.

- •11.3 Энергопотребление.

- •11.4 Электрические характеристики.

- •11.5 Синхронизация.

- •11.7 Характеристики системы ацп.

- •11.8 Временные диаграммы шины расширенния.

- •11.9 Временные характеристики spi.

- •11.10 Характеристики эсппзу.

- •12. Корпус.

- •12.1 Расположение выводов.

- •12.2 Размеры корпуса.

6.2.4 Выбор ведомого устройства (ss/).

Этот вход используется для выбора ведомого устройства. Сигнал на этой линии должен принять низкий уровень до начала обмена данными и должен оставаться низким в течение всего времени обмена.

У ведущего устройства сигнал на этой линии должен постоянно быть высокого уровня. Если же уровень сигнала становится низким, то устанавливается флаг ошибки MODF регистра статуса SPI (SPSR). Вывод SS/ можно настроить как линию вывода общего назначения посредством записи “1” в бит 5 порта D, запрещая таким образом работу системы контроля. Три других вывода при работе SPI всегда используются самим SPI.

Если бит CPHA=0, то в качестве импульсов сдвига используется сигнал, представляющий собой функцию “ИЛИ” сигналов SS/ и SCK. В этом режиме уровень сигнала на линии SS/ должен быть высоким между двумя последовательными символами при передачи одного сообщения SPI. При CPHA=1 уровень сигнала на SS/ может оставаться низким на протяжении передачи нескольких символов. В случае когда присутствует только одно ведомое устройство, вывод SS/ можно подключить к VSS, пока используются режимы с CPHA=1.

6.3 Функциональное описание.

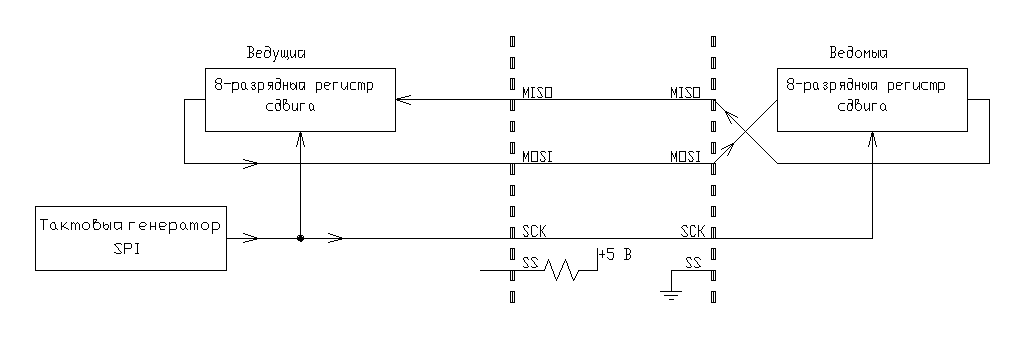

На рисунке 6-2 представлена блок-схема системы последовательного периферийного интерфейса. Когда ведущее устройство передает данные ведомому по линии MOSI, ведомое устройство отвечает посылкой данных ведомому по линии MISO. Весь этот процесс и составляет дуплексный обмен данными между двумя устройствами с синхронизацией одним и тем же сигналом. Таким образом, передаваемый байт замещается принимаемым байтом и поэтому не требуются отдельные флаги, сигнализирующие об очистке передатчика и заполнении приемника. Для инцикации завершения обмена данными используется один бит SPIF.

Рисунок 6-2. Блок-схема SPI.

Последовательный периферийный интерфейс является дважды буферированным на чтение, но не запись. Если выполняется запись данных во время передачи данных, то текущая передача не прерывается, а сама запись игнорируется. Такое событие вызывает установку флага ошибки записи WCOL регистра SPSR. После сдвига данных устанавливается флаг SPIF того же регистра SPSR.

В режиме ведущего устройства вывод SCK является выходом. В свободном состоянии он имеет низкий или высокий уровень, в зависимости от состояния бита CPOL регистра SPCR. После записи в сдвиговый регистр формируются восемь тактовых импульсов синхронизации для сдвига восьми бит данных, после чего линия SCK снова принимает в свободное состояние.

В режиме ведомого устройства логические схемы формируют низкий уровень на выводе SS/ и формируют тактовые импульсы на выводе SCK. Таким образом, ведомое устройство синхронизируется по ведущему. Данные последовательно посылаются ведущим устройством по линии MOSI и считываются в регистр сдвига. После полной загрузки сдвигового регистра данные параллельно перемещаются в буфер чтения. В течение цикла записи данные записываются в сдвиговый регистр, после чего ведомое устройство ждет сигнала синхронизации от ведущего для сдвига данных по линии MISO.

На рисунке 6-3 показано взаимное соединение выводов MOSI, MISO, SCK и SS ведущего и ведомого устройств.

Рисунок 6-3. Соединение ведущий-ведомый при использовании SPI.

Поскольку линии порта D (и соответственно линии SPI) могут работать в режиме с открытым стоком и таким образом позволять соединение “монтажное ИЛИ”, система SPI может быть построена различными способами. Система, в которой происходит единственный двунаправленный обмен данными может просто использовать соединение выводов MISO и MOSI. Но так как микроконтроллер MC68HC11E9 может выборочно запрещать свой выход MISO, то возможны другие виды протокола обмена.