- •Однокристальная микроЭвм

- •Содержание

- •1. Введение.

- •1.1 Характеристики.

- •1.2 Общее описание.

- •1.3 Программная модель.

- •1.4 Характеристики представителей семейства mc68hc11.

- •2. Описание сигналов и режимы работы.

- •2.1 Описание выводов.

- •2.1.1 Выводы питания (vdd) и земли (vss).

- •2.1.2 Сброс (reset/).

- •2.1.3 Входы внешней синхронизации (xtal и extal).

- •2.1.4 Вывод тактовой частоты синхронизации e (e).

- •2.1.5 Запрос прерывания (irq/).

- •2.1.6 Немаскируемое прерывание (xirq/).

- •2.1.7 Выводы moda/lir/ и modb/vstby.

- •2.1.8 Опорные напряжения ацп (vrLи vrh).

- •2.1.9 Строб b и чтение/запись (strb / r/w/).

- •2.1.10 Строб a и строб адреса (stra/as)

- •2.1.11 Сигналы портов.

- •2.2 Режимы работы.

- •2.2.1 Однокристальный режим.

- •2.2.2 Расширенный режим.

- •2.3 Специальный режим загрузки.

- •Примечание

- •Примечание

- •2.2.4 Дополнительные опции загрузчика программ.

- •2.2.5 Специальный режим теста.

- •3. Внутренняя память.

- •3.1 Карта памяти.

- •3.2 Озу и регистр отображения памяти (init).

- •3.5 Эсппзу.

- •3.5.1 Регистр управления эсппзу (pprog).

- •3.5.2 Регистр защиты эсппзу (bprot).

- •3.5.3 Программирование/стирание внутреннего эсппзу.

- •3.5.4 Регистр конфигурации системы (config).

- •Примечание: в этот момент недопустим сброс контроллера!!!

- •4. Параллельный ввод/вывод.

- •4.1 Порты ввода/вывода общего назначения (c и d).

- •4.2 Порты с фиксированным направлением ввода/вывода (a, b и e).

- •4.3 Простой стробируемый ввод/вывод.

- •4.3.1 Стробируемый ввод-порт c.

- •4.3.2 Стробируемый вывод-порт b.

- •4.4 Ввод/вывод с полным квитированием установления связи.

- •4.4.1 Протокол режима ввода с полным квитированием установления связи.

- •4.4.2 Протокол режима вывода с полным квитированием установления связи.

- •4.5 Регистр управления вводом/выводом (pioc).

- •5. Последовательный интерфейс связи (sci).

- •5.3 Особенности при работе в системах с несколькими приемниками.

- •5.4 Принимаемые данные (RxD).

- •5.5 Распознавание старт-бита.

- •5.6 Передаваемые данные (TxD).

- •5.7 Фунциональное описание.

- •5.8 Регистры sci.

- •5.8.1 Регистр данных последовательной связи (scdr).

- •5.8.2 Регистр управления 1 (sccr1).

- •5.8.3 Регистр управления 2 (sccr2).

- •5.8.4 Регистр статуса последовательной связи (scsr).

- •5.8.5 Регистр скорости приема/передачи (baud).

- •Примечание

- •Примечание

- •6. Последовательный периферийный интерфейс.

- •6.1 Общий обзор и характеристики.

- •6.2 Описание сигналов spi.

- •6.2.1 Вход ведущего-выход ведомого (miso).

- •6.2.2 Выход ведущего-вход ведомого (mosi).

- •6.2.3 Сигналы синхронизации (sck).

- •6.2.4 Выбор ведомого устройства (ss/).

- •6.3 Функциональное описание.

- •6.4 Регистры spi.

- •6.4.1 Регистр управления периферийным интерфейсом (spcr).

- •6.4.2 Регистр статуса поеледовательного периферийного интерфейса (spsr).

- •6.4.3 Регистр ввода/вывода spi.

- •7. Аналого-цифровой преобразователь.

- •7.1 Процесс преобразования.

- •7.2 Назначение каналов.

- •7.4 Работа в многоканальном режиме.

- •7.5 Работа в режимах stop и wait.

- •7.6 Регистр управления и статуса ацп (adctl).

- •Примечание:

- •Примечание:

- •7.7 Регистры результатов преобразований 1,2,3 и 4 (adr1, adr2, adr3 и adr4).

- •7.8 Подача питания на ацп и выбор источника синхронизации.

- •8. Программируемый таймер, прерывания реального времени и счетчик импульсов.

- •8.1 Программируемый таймер.

- •8.1.1 Счетчик.

- •8.1.2 Входная фиксация.

- •8.1.3 Выходное сравнение.

- •8.1.4 Управление вводом/выводом выходного сравнения 1.

- •8.1.5 Регистр принудительного сравнения таймера (cforc).

- •8.1.6 Регистр 1 маскирования выходного сравнения (oc1m).

- •8.1.7 Регистр данных выходного сравнения 1 (oc1d).

- •8.1.8 Регистр 1 управления таймером (tctl1).

- •8.1.9 Регистр 2 управления таймером (tctl2).

- •8.1.10 Регистр 1 маскирования прерываний таймера (tmsk1).

- •Примечание:

- •8.1.11 Регистр 1 флагов прерывания таймера (tflg1).

- •Примечание:

- •8.1.12 Регистр 2 маскирования прерываний таймера (tmsk2).

- •8.1.13 Регистр 2 флагов прерываний таймера (tflg2).

- •8.2 Прерывания реального времени.

- •8.3 Счетчик импульсов.

- •8.4 Регистр управления счетчиком импульсов (pactl).

- •9. Сброс, прерывания и режимы с пониженным потреблением энергии.

- •9.1 Варианты сброса.

- •9.1.1 Внешний вывод reset/.

- •9.1.2 Сброс при включении питания.

- •9.1.3 Сброс, вызываемый системой слежения.

- •9.1.4 Сброс тактового монитора.

- •9.1.5 Регистр выбора конфигурации (option).

- •9.2 Прерывания.

- •9.2.1 Программное прерывание (swi).

- •Примечание

- •9.2.2 Прерывание по неверному коду команды.

- •9.2.3 Биты маскирования прерываний регистра условий.

- •9.2.4 Структура приоритетов.

- •9.2.5 Регистр наивысшего приоритета I-прерывания (hprio).

- •9.3 Режимы пониженного энергопотребления.

- •9.3.1 Команда wait.

- •9.3.2 Команда stop.

- •10. Центральный процессор, режимы адресации и система команд.

- •10.1 Регистры цп.

- •10.1.1 Аккумуляторы a и b.

- •10.2 Режимы адресации.

- •10.2.1 Непосредственная адресация.

- •10.2.2 Прямая адресация.

- •10.2.3 Расширенная адресация.

- •10.2.4 Индексная адресация.

- •10.2.5 Неявная адресация.

- •10.2.6 Относительная адресация.

- •10.2.7 Байт префикса.

- •10.3 Система команд.

- •11. Электрические характеристики.

- •11.1 Максимальные диапазоны.

- •11.2 Температурные характеристики.

- •11.3 Энергопотребление.

- •11.4 Электрические характеристики.

- •11.5 Синхронизация.

- •11.7 Характеристики системы ацп.

- •11.8 Временные диаграммы шины расширенния.

- •11.9 Временные характеристики spi.

- •11.10 Характеристики эсппзу.

- •12. Корпус.

- •12.1 Расположение выводов.

- •12.2 Размеры корпуса.

9.2.1 Программное прерывание (swi).

Программное прерывание выполняется аналогично другим командам. Прерывание SWI имеет приоритет над другими прерываниями, если они замаскированы. (биты I и X регистра условий установлены). Процесс обработки SWI похож на процесс обработки других маскируемых прерываний: устанавливается бит I, регистры процессора сохраняются в стеке и т.д.

Примечание

Команда SWI не будет выполнена, если ожидается обработка другого прерывания. Однако как только началось выполнение команды SWI, никакое другое прерывание не может быть обработано до тех пор, пока не будет выбран вектор SWI.

9.2.2 Прерывание по неверному коду команды.

Так как не все возможные коды команд или последовательности команд определены, то микроконтроллер включает в себя схемы определения неверного кода команды. Когда обнаруживается неверный код команды, то запрашивается прерывание. Вектор этого прерывания никогда не следует оставлять неинициализированным. Можно посоветовать инициализировать указатель стека при обработке данного прерывания, так что повторяющаяся последовательность неверных команд не вызовет переполнения стека.

9.2.3 Биты маскирования прерываний регистра условий.

После сброса устанавливаются биты I и X для того, чтобы запретить все маскируемые прерывания и прерывание XIRQ/. Программно можно очистить бит X командой TAP, разрешая таким образом прерывания XIRQ/. После этого уже нельзя установить бит X, то есть это прерывание на самом деле является немаскируемым. Изменение бита I, связанного с системой прерываний, также не оказывает никакого влияния на бит X. В системе прерываний XIRQ/ имеет более высокий приоритет над всеми источниками, которые маскируются битом I. Все связанные с битом I прерывания действуют в соответствии со своей системой приоритетов. При возникновении прерывания, связанного с битом I, этот бит автоматически устанавливается после сохранения в стеке регистра условий, но бит X не изменяется. При возникновении прерывания, связанного с битом X, аппаратно устанавливаются оба бита-X и I после сохранения в стеке регистра условий. Команда RTI (возврат из прерывания) восстанавливает состояние битов X и I на момент запроса прерывания.

9.2.4 Структура приоритетов.

Для того, чтобы разрешить ситуацию одновременного запроса нескольких прерываний, у различных прерываний аппаратно установлен разный приоритет. Однако один из источников прерывания маскируемый битом I можно программно сделать прерыванием с наивысшим приоритетом. Первые шесть источников прерываний не маскируются битом I регистра условий и имеют следующий фиксированный приоритет: сброс, сброс тактового монитора, сброс системы слежения, прерывание по неверному коду командыиXIRQ/. (SWI - является командой и имеет наивысший приоритет после сброса в том смысле, что после выборки кода SWI никакое другое прерывание не обрабатывается до тех пор, пока не будет выбран вектор SWI). Каждый из этих источников прерываний подключен на вход системы разрешения приоритетов. Наивысший приоритет источнику, маскируемому битом I назначается программно - регистром HPRIO, при этом вход наивысшего прерывания соединяется с выбранным источником прерывания. Для того, чтобы избежать конфликтов, регистр HPRIO можно перезаписывать только если прерывания маскируемые битом I запрещены (бит I регистра условий установлен в логическую единицу). Прерывание, которому назначается наивысший приоритет, можно запретить соответствующим битом управления или битом I регистра условий. При назнаначении прерыванию наивысшего приоритета его вектор не изменяется.

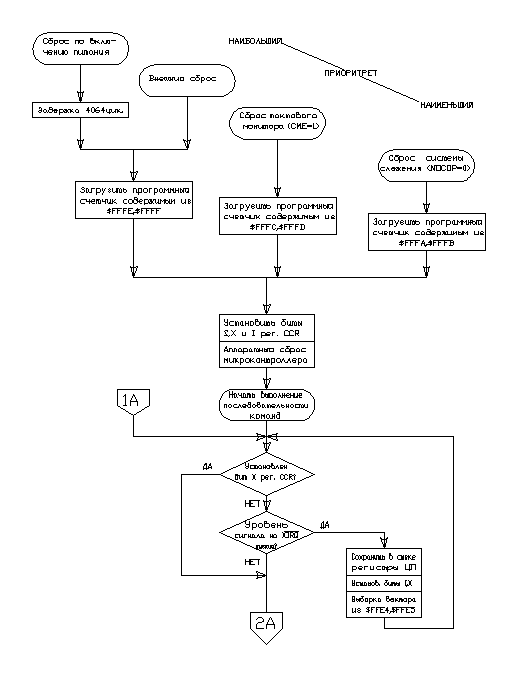

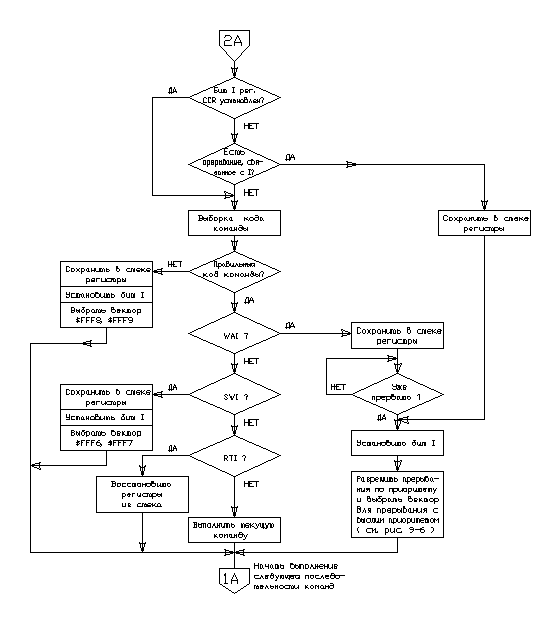

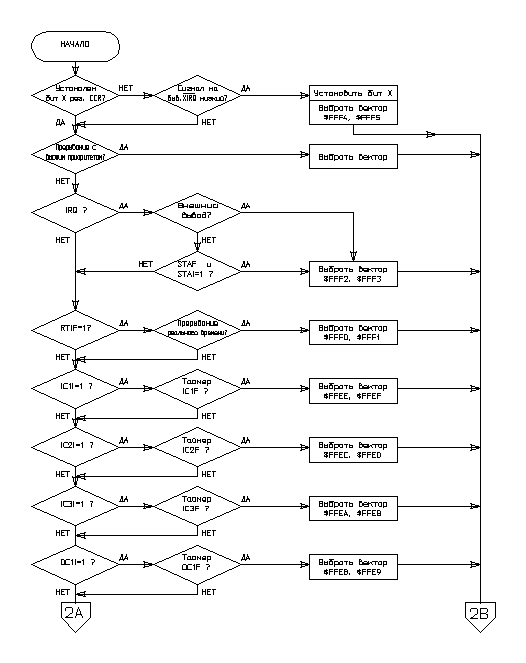

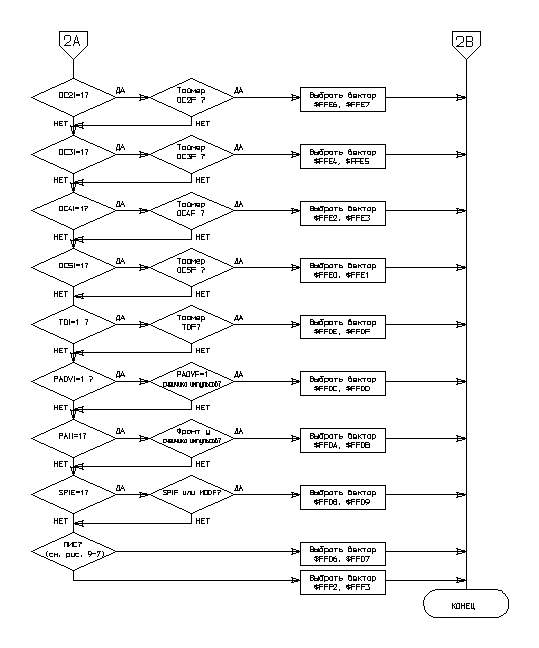

Рисунки 9-5, 9-6, и 9-7 иллюстрируют процесс обработки прерывания и его связь с процессом обычной работы. Рисунок 9-5 показывает, как процессор выполняет сброс и как обнаружение прерывания соотносится с выборкой кода обычной команды. Рисунок 9-7 более детально показывает блока прерывания SCI представленный на рисунке 9-6. Рисунок 9-7 показывает разрешение конфликта прерываний внутри подсистемы SCI.

Рисунок 9-5. Обработка прерываний (лист 1).

Рисунок 9-5. Обработка прерываний (лист 2).

Замечание: здесь представлено расширение рисунка 9-5.

Рисунок 9-6. Разрешение приоритетов прерываний (лист 1).

Замечание: здесь представлено расширение рисунка 9-5.

Рисунок 9-6. Разрешение приоритетов прерываний (лист 2).

Замечание: здесь представлено расширение рисунка 9-6.

Рисунок 9-7. Разрешение приоритетов прерываний от SCI.