- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

Типи операндів та способи адресації

МК 51 використовує операнди чотирьох типів: біти, 4-бітові цифри, байти і 16-байтові слова. З карти адрес РПД (рисунок 8.4) видно, МК має 128 програмно-керованих індикаторів користувача, а також є можливість адресації окремих бітів блока регістрів спеціальних функцій. Для адресації бітів використовується пряма 8-бітова адреса (bit), як це показано для команд 4 і 11 (рисунок 8.9). Опосередкована адресація бітів неможлива. Чотирибітові операнди виконуються тільки в операціях обміну SWAP i XCHD (формат типу 1).Восьмибітовим операндом може бути комірка пам’яті програм або даних (резидентної або зовнішньої), константа (безпосередній операнд), регістри спеціальних функцій, а також порти вводу-виводу. Порти і регістри спеціальних функцій адресуються тільки прямим способом. Байти пам’яті можуть адресуватись також і опосередковано через адресні регістри R0 і R1, відповідного банку, а також регістри DPTR і лічильник команд PC.

Таблиця 8.13- Перелік базових типів команд МК 51 в алфавітному порядку.

|

Мнемокод |

Призначення |

|

ACALL |

Абсолютний виклик підпрограми в межах сторінки в 2К |

|

ADD |

Додавання |

|

ADDC |

Додавання з переносом |

|

AJMP |

Абсолютний перехід в межах сторінки в 2К |

|

ANL |

Логічне ”І“ |

|

CJNE |

Порівняння байта в РПД з константою і перехід, якщо рівно |

|

CLR |

Обнуління акумулятора, біта або переносу |

|

CPR |

Інверсія акумулятора, біта або переносу |

|

DA |

Десяткова корекція акумулятора |

|

DEC |

Декремент |

|

DIV |

Ділення |

|

DJNZ |

Декремент байта і перехід, якщо нуль |

|

INC |

Інкремент |

|

JB |

Перехід, якщо біт рівний одиниці |

|

JBC |

Перхід, якщо біт установлено з наступним його обнулінням |

|

JC |

Перехід, якщо перенос рівний одиниці |

|

JMP |

Опосередкований відносний перехід |

|

JNB |

Перехід, якщо біт рівний нулю |

|

JNZ |

Перехід, якщо акумулятор не рівний нулю |

|

JZ |

Перехід, якщо акумулятор рівний нулю |

|

JCALL |

Довгий виклик підпрограми |

|

LJMP |

Довгий перехід в повному об’ємі пам’яті програм |

|

MOV |

Пересилання та завантаження даних в межах РПД |

|

MOVC |

Пересилання з пам’яті програм |

|

MOVX |

Персилання з ЗПД |

|

MUL |

Множення |

|

NOP |

Неробочій хід |

|

ORL |

Логічне ”АБО“ |

|

POP |

Добування зі стеку |

|

PUSH |

Завантаження в стек |

|

RET |

Повернення з підпрограми |

|

RETI |

Повернення з підпрограми обробки переривань |

|

RL |

Зсув вліво циклічно |

|

RLC |

Зсув вліво через перенос |

|

RR |

Зсув вправо циклічно |

|

RRC |

Зсув вправо через перенос |

|

SETB |

Установка біта |

|

SJMP |

Короткий відносний перехід в межах сторінки в 256 байтів |

|

SUBB |

Віднімання з запозиченням |

|

SWAP |

Обмін тетрадами в байт |

|

XCH |

Взаємообмін акумулятора з регістрами та комірками пам’яті |

|

XCHD |

Обмін молодшими тетрадами акумулятора і комірки пам’яті |

|

XRL |

Виключаюче ”АБО“ |

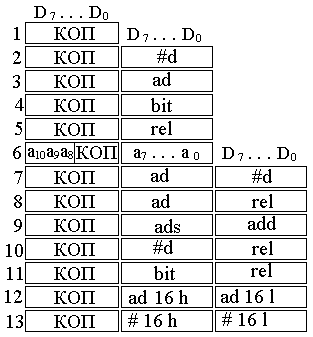

Рисунок 8.9- Формати команд МК 51:

КОП - код операції;

ad - пряма 8-розрядна адреса байта в РПД з такими уточненнями:

add - для джерела;

ads - для приймача;

ad11(a10 . . . a0) - біти прямої 11-розрядної адреси передачі керування в пам’яті програм;

ad16 - пряма 16-розрядна адреса передачі керування в пам’яті програм, де:

ad 16 h - старший, а

ad 16 l - молодший біт адреси;

bit - пряма 8-розрядна адреса біта;

#d - 8-розрядний операнд;

#d 16 16-розрядний операнд, де:

#d 16 h - старший, а

#d 16 l - молодший біт адреси;

rel - 8-розрядна відносна адреса передачі керування в РПД (-127 . . . +127).

Двобайтові операнди - це константи і прямі адреси, для представлення яких використовується другий і третій байт команди (типи 12 і 13).

В системі команд МК 51 передбачені 11 способів адресації операндів (рисунок 8.9).

основні: регістрова (тип 1); безпосередня (типи 2 і 3);

пряма (типи 3...6, 12); неявна (тип 1);

опосередкована (тип 1).

комбіновані: безпосередня з прямою (типи 7 і 10); пряма з

прямою (типи 8, 9, 11); пряма з опосередкованою

(тип 2 і 3); тощо.

Така широка номенклатура способів адресації операндів загальна кількість команд збільшується до 255, що практично вичерпує максимально можливу номенклатуру команд при однобайтовому коді операції.

При використанні асемблера МК51 (ASM51) з метою одержання об’єктних кодів програм допускається при програмуванні вживати символьні імена регістрів символьних функцій, портів і їх окремих бітів. Для адресації окремих бітів РСФ і портів (де це можливо) можна використовувати символьні імена бітів в такому форматі:

<ім’я РСФ або порта>.<номер біта>

Наприклад, символьне ім’я порта Р1, можна записати, як Р1.2, а п’ятого біта акумулятора - АСС.5. Символьні імена регістрів і їх бітів є резервованими словами для ASM 51, тому їх не треба визначати директивами асемблера.

Команди передачі даних

Дана група є найбільшою в системі команд МК 51 і містить 4 підгрупи: пересилок, завантаження, обміну даними і стекові команди. Крім того їх можна поділити на команди, які оперують з байтами та команди бітових операцій. Тут будуть розглядатись команди, які оперують з байтами (таблиця 8.14).

Таблиця 8.14- Команди передачі даних

|

Назва команди |

Мнемоніка |

КОП |

Т |

В |

Ц |

Операція |

|

Команди пересилок |

||||||

|

Пересилка

в акумулятор з регістра (n=0 |

MOV A,Rn |

11101ііі |

1 |

1 |

1 |

(A)(Rn) |

|

Пересилка в акумулятор прямоадресованого байта |

MOV A,ad |

11100101 |

3 |

2 |

1 |

(A)(ad) |

|

Пересилка в акумулятор байта з РПД (і=0,1) |

MOV A, @Ri |

1110011і |

1 |

1 |

1 |

(A)((Ri)) |

|

Пересилка в регістр з акумулятора |

MOVRn,A |

11111ііі |

1 |

1 |

1 |

(Rn)(A) |

|

Пересилка в регістр прямоадресованого байта |

MOV Rn,ad |

10101ііі |

3 |

2 |

2 |

(Rn)(ad) |

|

Пересилка за прямою адресою ак. |

MOV ad,A |

11110101 |

3 |

2 |

1 |

(ad)(A) |

|

Пересилка за прямою адресою регістра |

MOV ad,Rn |

10001ііі |

3 |

2 |

2 |

(ad)(Rn) |

|

Пересилка прямоадресованого байта по прямій адресі |

MOV add, ads |

10000101 |

9 |

3 |

2 |

(add)(abs) |

|

Пересилка байта з РПД по прямій адресі |

MOV ad, @Ri |

1000011і |

3 |

2 |

2 |

(ad)((Ri)) |

|

Пересилка в РПД з акумулятора |

MOV @Ri, A |

1111011і |

1 |

1 |

1 |

((Ri))(A) |

|

Пересилка в РПД прямоадресованого байта |

MOV @Ri, ad |

0110011і |

3 |

2 |

2 |

((Ri))(ad)

|

|

Пересилка в акуму-лятор байта з ПП |

MOVC A, @A+DPTR |

10010011 |

1 |

1 |

2 |

(A)((A)+ +(DPTR)) |

|

Пересилка в акуму-лятор байта з ПП |

MOVC A, @A+PC |

10000011 |

1 |

1 |

2 |

(PC)(PC)+1 (A)((A)+(PC)) |

|

Пересилка в акуму-лятор байта з ЗПД |

MOVX A,@Ri |

1110001і |

1 |

1 |

2 |

(A)((Ri)) |

|

Пересилка в акуму-лятор байта з розширеної ЗПД |

MOVX A, @DPTR |

11100000 |

1 |

1 |

2 |

(A)((DPTR)) |

|

Пересилка в ЗПД з акумулятора |

MOVX @Ri,A

|

1111001і |

1 |

1 |

2 |

((Ri))(A) |

|

Пересилка в розши-рену ЗПД з акуму-лятора |

MOVX @DPTR,A |

11110000 |

1 |

1 |

2 |

(DPTR)(A) |

|

Команди завантаження |

||||||

|

Завантаження в регістр константи |

MOV Rn,#d |

01111ііі |

2 |

2 |

1 |

(Rn) #d |

|

Завантаження в акумулятор константи |

MOV A,#d |

01110100 |

2 |

2 |

1 |

(A)#d

|

|

Пересилка за прямою адресою константи |

MOV ad,#d |

01110101 |

7 |

3 |

2 |

(ad)#d |

|

Пересилка в РПД константи |

MOV @Ri, #d |

0111011і |

2 |

2 |

1 |

((Ri))#d |

|

Завантаження вказівника даних |

MOV DPTR, #d16 |

10010000 |

13 |

3 |

2 |

(DPTR)#d16 |

|

Стекові команди |

||||||

|

Завантаження в стек |

PUSH ad |

11000000 |

3 |

2 |

2 |

(SP)(SP)+1 ((SP))(ad) |

|

Вилучення зі стека |

POP ad |

11010000 |

3 |

2 |

2 |

(ad)(SP) (SP)(SP)-1 |

|

Команди обміну |

||||||

|

Обмін акумулятора з регістром |

XCH A,Rn |

11001ііі |

1 |

1 |

1 |

(A) |

|

Обмін акумулятора з Прямоадресованим Байтом |

XCH A,ad |

11000101 |

3 |

2 |

1 |

(A)

|

|

Обмін акумулятора з байтом із РПД |

XCH A,@Ri |

1100011і |

1 |

1 |

1 |

(A) |

|

Обмін молодшої тетради акумулятора з молодшою тетрадою байта РПД |

XCHD A,@Ri |

1101011і |

1 |

1 |

1 |

(A0-3

) |

Команди пересилки даних мають три модифікації:

MOV - пересилки в межах резидентної пам’яті даних, регістрів, спеціальних функцій та портів;

MOVC - пересилки з пам’яті програм (внутрішньої та зовнішньої) в акумулятор;

MOVX - двонаправлені пересилки із зовнішньої пам’яті даних і акумулятора.

Команда MOV забезпечує двонаправлені пересилки, джерелами та приймачами яких з одного боку є акумулятор, а з другого - регістри оперативного призначення Rn (від R0 до R7 відповідного банку регістрів), комірки внутрішнього ОЗП, адреси яких (операнд ad задається в діапазоні адрес від 00 H до FF H) прямо задається в команді, комірки резидентної пам’яті даних (адреси від 00 Н до 7F H) вказується опосередковано через регістри R0 i R1 відповідного банку. Низка пересилок може виконуватись без участі акумулятора. Зокрема пересилки з однієї комірки внутрішнього ОЗП в іншу, адреса приймача (add) і джерела (ads) задається відповідно в другому і третьому байтах команди MOV, з комірки ОЗП в регістр оперативного призначення і навпаки. Можлива і опосередкована адресація комірки РПД через регістри R0 i R1. Основні способи пересилки з використанням команди MOV показані на таких прикладах:

|

MOV A,R3 |

; Пересилка даних з регістра R3 в акумулятор |

|

MOV P1,A |

; Пересилка байта з акумулятора в порт Р1 |

|

MOV @R1,P2 |

; Пересилка з порту Р2 в комірку РПД, адреса якої в ;регістрі R1 |

|

MOV R5,P0 |

; Пересилка байта з порту Р0 в регістр R5 |

|

MOV@R0,SUBF |

; Пересилка прийнятого в послідовному каналі байта в ;РПД |

Команди MOVC забезпечують занесення до акумулятора байта з комірок пам’яті програм, адреса яких утворена сумою поточного вмісту акумулятора та вказівника даних (MOVC A,@A+DPTR) або сумою вмісту акумулятора і лічильника команд (MOVC A,@A+PC). Перша команда дозволяє пересилати байти з комірок, що знаходяться в повному адресному просторі зовнішньої пам’яті програм об’ємом 64 Кбайти, а друга - в суміщеному адресному просторі ПП (тобто ЗП складає 64 Кбайтів +256 байтів, що задаються байтом акумулятора). Дані команди зручно використовувати у тому випадку, коли готові результати розв’язку певної задачі написані в ПП (наприклад, таблиця sin x для цілих кутів, квадратів чисел тощо).

В МК51 при використанні команди MOVX @,Ri забезпечується доступ до 256 байтів ЗПД для виконання пересилок, а також є двосторонній обмін байтами між акумулятором і розширеною ЗПД, коли для доступу до комірок пам’яті використовується 16-бітна адреса, що зберігається в регістрі-покажчику даних DPTR. Команда MOVX @DPTR забезпечує доступ до 65536 байтам ЗПД.

Команди арифметичних операцій

Дану групу утворюють 24 команди (таблиця 8.15), які використовують команди віднімання, десяткової корекції, інкременту/декременту байтів а також команди множення та ділення. Основною особливістю основних команд арифметичних операцій є те, що одним із операндів і приймачем результату є акумулятор. Другим операндом є регістри оперативного призначення, комірки внутрішнього ОЗП, безпосередні дані, комірки РПД. Всі безпосередні дані, крім інкременту/декременту байтів діють на індикатори.

Дія команд додавання, віднімання, десяткової корекції, інкременту/декремету співпадає з дією аналогічних команд вже розглянутих в МП (наприклад, КМ 1810 ВМ 86).

Таблиця 8.15- Група команд арифметичних операцій

|

Назва команди |

Мнемоніка |

КОП |

Т |

В |

Ц |

Операція |

|

Додавання

акумулятора і регістра (n=0 |

ADD A,Rn |

00101iii |

1 |

1 |

1 |

(A)(A)+(Rn) |

|

Додавання акумулятора і прямоадресовано-го байта |

ADD A,ad |

00100101 |

3 |

2 |

1 |

(A)(A)+(ad) |

|

Додавання акумулятора і байта з РПД |

ADD A,@Ri |

0010011i |

1 |

1 |

1 |

(A)(A)+((Ri)) |

|

Додавання акумулятора і константи |

ADD A,#d |

00100100 |

2 |

2 |

1 |

(A)(A)+#d |

|

Додавання акумулятора і регістра з перено-сом |

ADDC A,Rn |

00111iii |

1 |

1 |

1 |

(A)(A)+(Rn)+(C) |

|

Додавання акумулятора і прямоадресовано-го байта з переносом |

ADDC A,ad |

00110101 |

3 |

2 |

1 |

(A)(A)+(ad)+(C) |

|

Додавання акуму-лятора і байта з РПД з переносом |

ADDC A,@Ri |

0011011i |

1 |

1 |

1 |

(A)(A)+((Ri))+(C) |

|

Додавання акуму-лятора і константи з переносом |

ADDC A,#d |

00110100 |

2 |

2 |

1 |

(A)(A)+#d+(C) |

|

Десяткова корекція акумулятора |

DA A |

11010100 |

1 |

1 |

1 |

Якщо (A0-3) >9V ((AC)=1), то (A0-3)(A0-3)+6 потім, якщо(A4-7) >9V ((C)=1), то (A4-7)(A4-7)+6 |

|

Віднімання з акумулятора регістра з за-позиченням |

SUBB A,Rn |

10011iii |

1 |

1 |

1 |

(A)(A)-(C)-(Rn) |

|

Віднімання з акумулятора прямоадресо-ваного байта з запозиченням |

SUBB A,ad |

10010101 |

3 |

2 |

1 |

(A)(A)-(C)-((ad)) |

|

Віднімання з акумулятора байта з РПД з запозиченням |

SUBB A,@Ri |

1001011i |

1 |

1 |

1 |

(A)(A)-(C)-((Ri)) |

|

Віднімання з акумулятора константи з запозиченням |

SUBB A,#d |

10010100 |

2 |

2 |

1 |

(A)(A)-(C)-#d |

|

Інкремент акумулятора |

INC A |

00000100 |

1 |

1 |

1 |

(A)(A)+1 |

|

Інкремент регістра |

INC Rn |

00001iii |

3 |

1 |

1 |

(Rn)(Rn)+1 |

|

Інкремент прямоад-ресованого байта |

INC ad |

00000101 |

1 |

2 |

1 |

(ad)(ad)+1 |

|

Інкремент байта в РПД |

INC @Ri |

0000011i |

1 |

1 |

1 |

((Ri))((Ri))+1 |

|

Інкремент вказівника даних |

INC DPTR |

10100011 |

1 |

1 |

2 |

(DPTR)(DPTR)+1 |

|

Декремент акуму-лятора |

DEC A |

00010100 |

1 |

1 |

1 |

(A)(A)-1 |

|

Декремент регістра |

DEC Rn |

00011iii |

1 |

1 |

1 |

(Rn)(Rn) |

|

Декремент прямоад-ресованого байта |

DEC ad |

00010101 |

3 |

2 |

1 |

(ad)(ad)-1 |

|

Декремент байта в РПД |

DEC @Ri |

0001011i |

1 |

1 |

1 |

((Ri))((Ri))-1 |

|

Множення акуму-лятора і регістра В |

MUL AB |

10100100 |

1 |

1 |

4 |

(B)(A)(A)*(B) |

|

Ділення акумулятора і регістра В |

DIV AB |

10000100 |

1 |

1 |

4 |

(A).(B)(A)/(B) |