- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

6 Пам’ять мікропроцесорних пристроїв

Пам’ять є функціональною частиною МПС або мікро ЕОМ і призначена для запису, зберігання та відтворення інформації. Комплекс технічних засобів, який реалізує функцію пам’яті, називають запам’ятовуючим пристроєм (ЗП).

Основними операціями в пам’яті є запис - занесення інформації в пам’ять і зчитування - вибірка інформації з пам’яті. Ці операції називають зверненням до пам’яті.

6.1 Основні характеристики і класифікація запам’ятовуючих

пристроїв

До основних характеристик схем пам’яті і інтегральних схем пам’яті відносяться:

1) Інформаційна ємність пам’яті, яка визначає максимально можливу кількість бітів інформації для зберігання.

2) Ширина вибірки (розрядність), яка визначає кількість інформації (розрядів) записаної в ОЗП або вибраної з неї за одне звернення.

3) Час звернення (швидкодія). Це інтегрований параметр, для якого, як узагальнений, можна прийняти час циклу звернення до ЗП.

4) Споживана потужність Вона може бути різною для режиму зчитування (запису) і зберігання.

Важливою характеристикою ЗП є його спроможність зберігати інформацію при відключенні живлення, тобто є вони енергозалежні чи енергонезалежні.

За способом організації доступу (звернення) до пам’яті розрізняють два класи ЗП: з незалежним доступом (адресні) і з послідовним доступом (безадресні).

За способом зберігання інформації розрізняють статичні і динамічні ЗП.

З точки зору фізичної реалізації виділяють такі ЗП: вмонтовані в кристал МП; реалізовані у вигляді окремих ВІС; виконані у вигляді закінченого модуля, який містить групи ВІС і схеми управління.

За функціональним призначенням більшість типів ЗП можна поділити на такі групи: надоперативні (НОЗП); оперативні ЗП (ОЗП); постійні ЗП (ПЗП); перепрограмовані ЗП (ППЗП); програмовані логічні матриці (ПЛМ); буферні ЗП (БЗП), які призначені для спряження різних типів ЗП між собою і зовнішніми пристроями; стекові ЗП; зовнішні ЗП, які зберігають великий об’єм інформації (магнітні жорсткі і гнучкі диски, стрічки і т.д.)

6.2 Надоперативні і оперативні запам’ятовуючі пристрої

Надоперативні ОЗП складаються з набору регістрів, вміст яких безпосередньо використовується при обробці інформації в МП. Такі ОЗП вбудовані у ВІС МП і призначені для зберігання команд, операндів і результатів проміжних перетворень. Розрядність регістрів відповідає розрядності МП, а їх загальна кількість обмежена розмірами кристала. Надоперативні ОЗП виконані за єдиною з логічним елементом технологією і є набором регістрів на статичних тригерах, які не вимагають регенерації інформації, що в них зберігається . В мікропроцесорах великої продуктив-

ності , які є основою сучасних ПЕОМ , застосовується кеш-пам’ять ,що є різновидом надоперативної пам’яті.Вона є буфером між ОЗП і його “клієнтами”- процесором(одним або декількома )та іншими абонентами системної шини. Кеш-пам’ять не являється самостійним сховищем : інформація в ній не адресується клієнтами підсистеми пам’яті , присутність кеша для них є “ прозорою”.Кеш зберігає копії блоків даних тих областей ОЗП до яких були останні звернення і можливе повторне звернення до них буде обслужене кеш-пам’яттю значно швидше ніж ОЗП. Кеш в сучасних комп’ютерах збудований за дворівневою схемою :

■ Первинний кеш або L1 Cache –кеш 1 рівня,внутрішній кеш процесора класа 486 і старших для програмних кодів та даних.

■ Вторинний кеш або L2 Cache- кеш 2 рівня . Інколи це зовнішній кеш , що установлюється на системну плату , а в Pentium Pro , Pentium II та Pentium III кеш розміщений в одному корпусі з процесором.

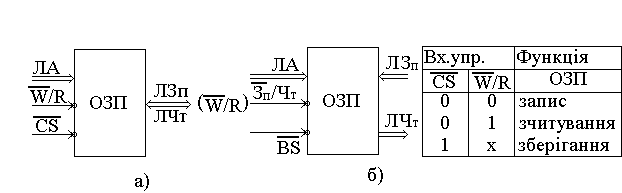

І снує

велика кількість елементів ОЗП, але

більшість з них має організацію за двома

типами (рисунок 6.1):

снує

велика кількість елементів ОЗП, але

більшість з них має організацію за двома

типами (рисунок 6.1):

Рисунок 6.1

ОЗП

має лінії адреси ЛА, для вибору комірки

пам’яті,

суміщені або окремі лінії запису і

зчитування даних, а також дві лінії

керування. В обох моделях керуюча лінія

![]() /ЧТ

/ЧТ

![]() задає режим запису при

задає режим запису при

![]() =0

і режим зчитування при ЧТ=1.

Керуюча лінія вибору кристала

=0

і режим зчитування при ЧТ=1.

Керуюча лінія вибору кристала

![]() дозволяє виконання операції звернення

до пам’яті при

дозволяє виконання операції звернення

до пам’яті при

![]() ,

або заперечує її виконання при

,

або заперечує її виконання при

![]() .

.

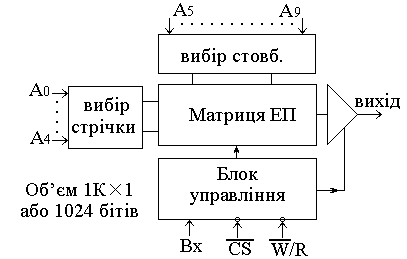

На рисунку 6.2 показана загальна організація ОЗП ємністю 1024 біт (1К), де матриця елементів пам’яті складається із 32 стрічок і 32 стовпчиків. Вибір будь-якої комірки здійснюється шляхом адресації стрічки (А0,....,А4) і стовпчика (А5,...,А9).

Рисунок 6.2

Активізація

даної ВІС здійснюється сигналом вибору

кристала

![]() .

Очевидно, що для організації ОЗП, яка

оперує машинним словом (8 біт) необхідно

паралельно задіяти 8 ВІС. При цьому

адресні входи під’єднуються

до ША, а лінії

.

Очевидно, що для організації ОЗП, яка

оперує машинним словом (8 біт) необхідно

паралельно задіяти 8 ВІС. При цьому

адресні входи під’єднуються

до ША, а лінії

![]() і

і

![]() до лінії керування МПС.

до лінії керування МПС.

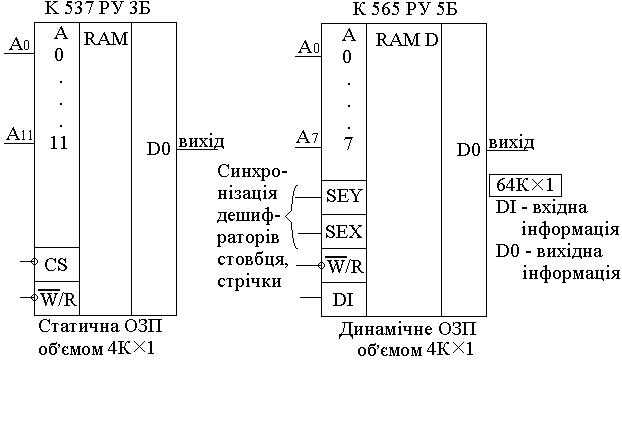

Промисловістю випускаються статичні і динамічні ОЗП.

Статичні ОЗП можуть зберігати інформацію як завгодно довго, доки надається живлення. Як елемент пам’яті використовується статичний тригер.

Динамічні ОЗП можуть зберігати інформацію короткий час (долі мс або мкс). Тому інформацію в них необхідно періодично обновляти, тобто регенерувати. Як елемент пам’яті використовується конденсатор з колами керування і регенерації. В динамічних ОЗП цикл зчитування (запису) більший, ніж у статичних, оскільки додається ще цикл регенерації пам’яті.

Приклади умовних позначень на принципових електричних схемах показаний на рисунку 6.3.

Рисунок 6.3