- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

4.1.3 Система команд мп

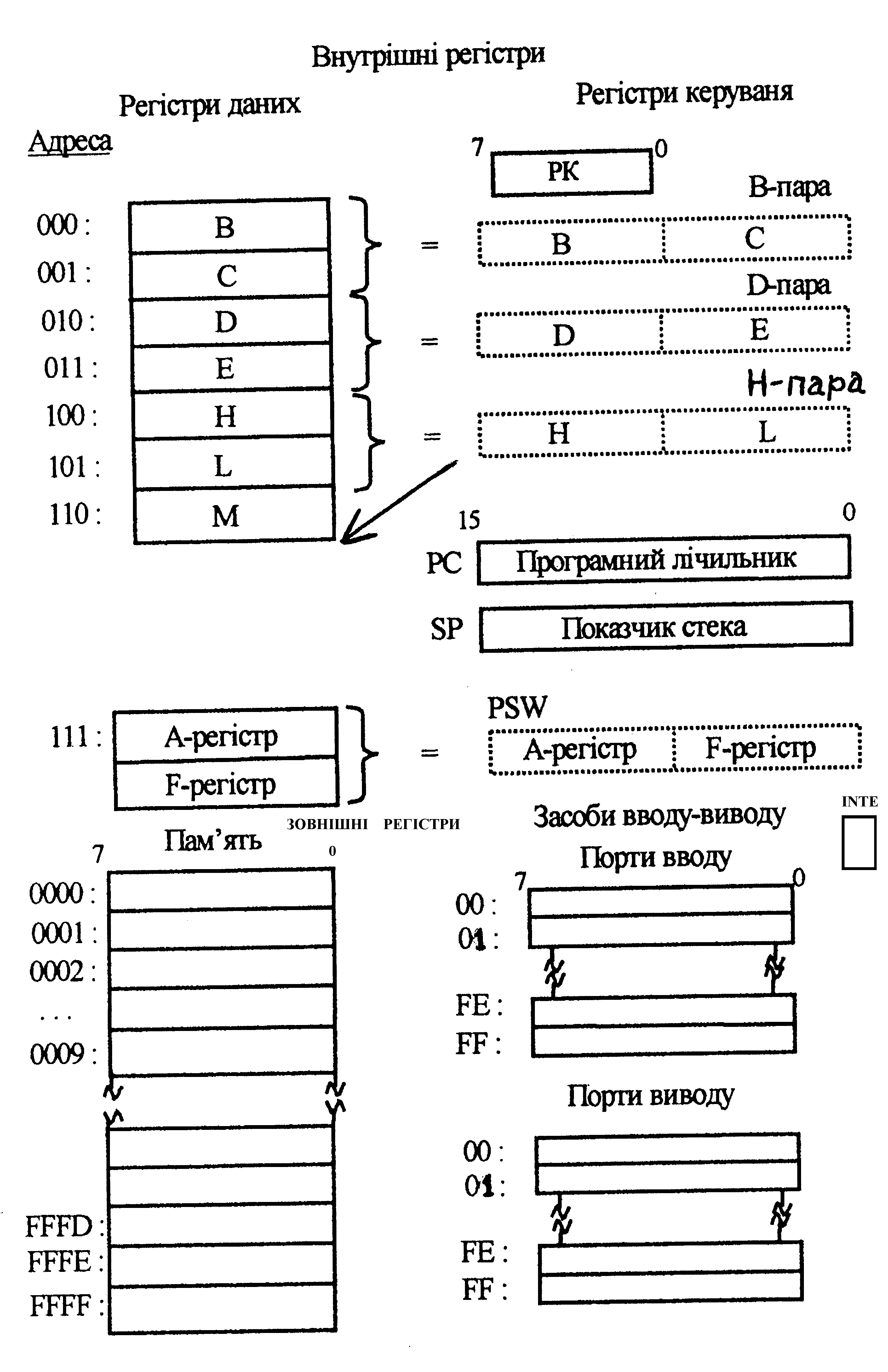

МПС на базі серії К580 представляють собою масив програмно доступних регістрів, над вмістом яких виконуються вказані в командах операції. Ефективність програми визначається повнотою системи команд МП і вмінням застосовувати цю систему команд при розвязку поставленої задачі. Програма складається з послідовності команд, які розміщені в памяті, що представляє собою послідовність комірок розміром один байт (рисунок 4.22). МП послідовно, байт за байтом зчитує вміст комірок памяті, адреса яких вказується лічильником команд РС, дешифрує їх і виконує.

Особливістю програмної моделі МП (рисунок 4.22) є можливість програмного обєднання 8-бітових РОП В, C, D, E, H, L в 16-бітові регістрові пари BC, DE і HL (скорочено їх відповідно позначають B, D і H-пари). Ці пари можуть зберігати 16-бітові операнди або виступати покажчиками памяті.

Основним покажчиком памяті є HL-пара і комірка памті, адреса якої визначається вмістом цієї пари і скорочено позначається буквою М.

Програмно доступними є також 16-бітовий лічильник команд РС, покажчик стеку SP, слово стану AF-PSW (акумулятор A і регістр ознак F) і тригер «Дозволу переривань» INTE, а також індикатори переносу C, знака S, нульового результату Z і парності P. МП може адресувати до 256 регістрів вводу, 256 регістрів виводу, а також 64 КБайти памяті.

Рисунок 4.22 – Програмна модель МП К580

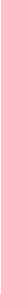

Команда МП може містити один, два або три байта (рисунок 4.23). Перший байт команди завжди містить код операції, а в інших двох байтах розміщуються операнди або адреси операндів. Адресація може бути прямою, безпосередньою, регістровою, опосередкованою і неявною.

Рисунок 4.23 - Формат команд МП ВМ80

Типи команд

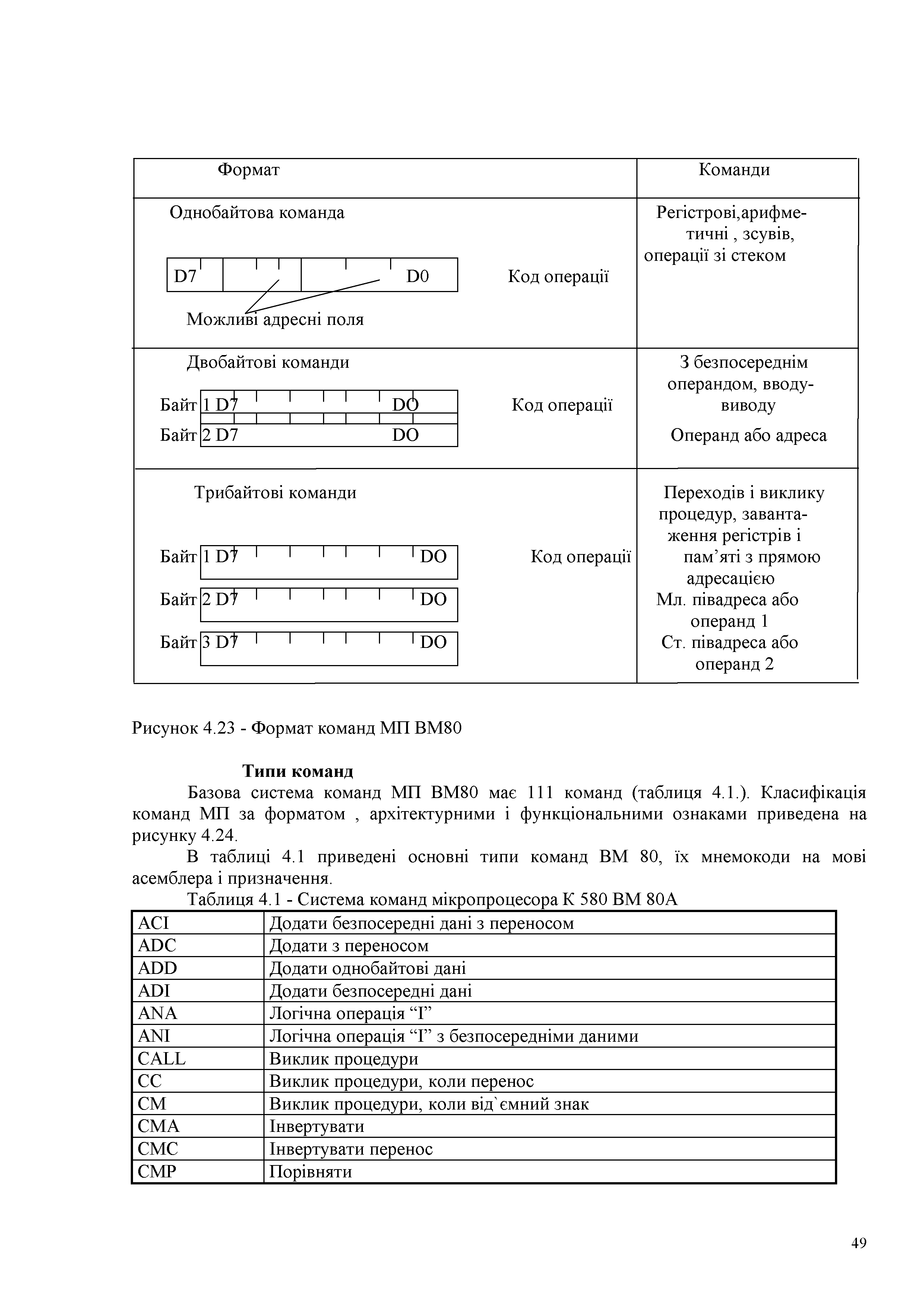

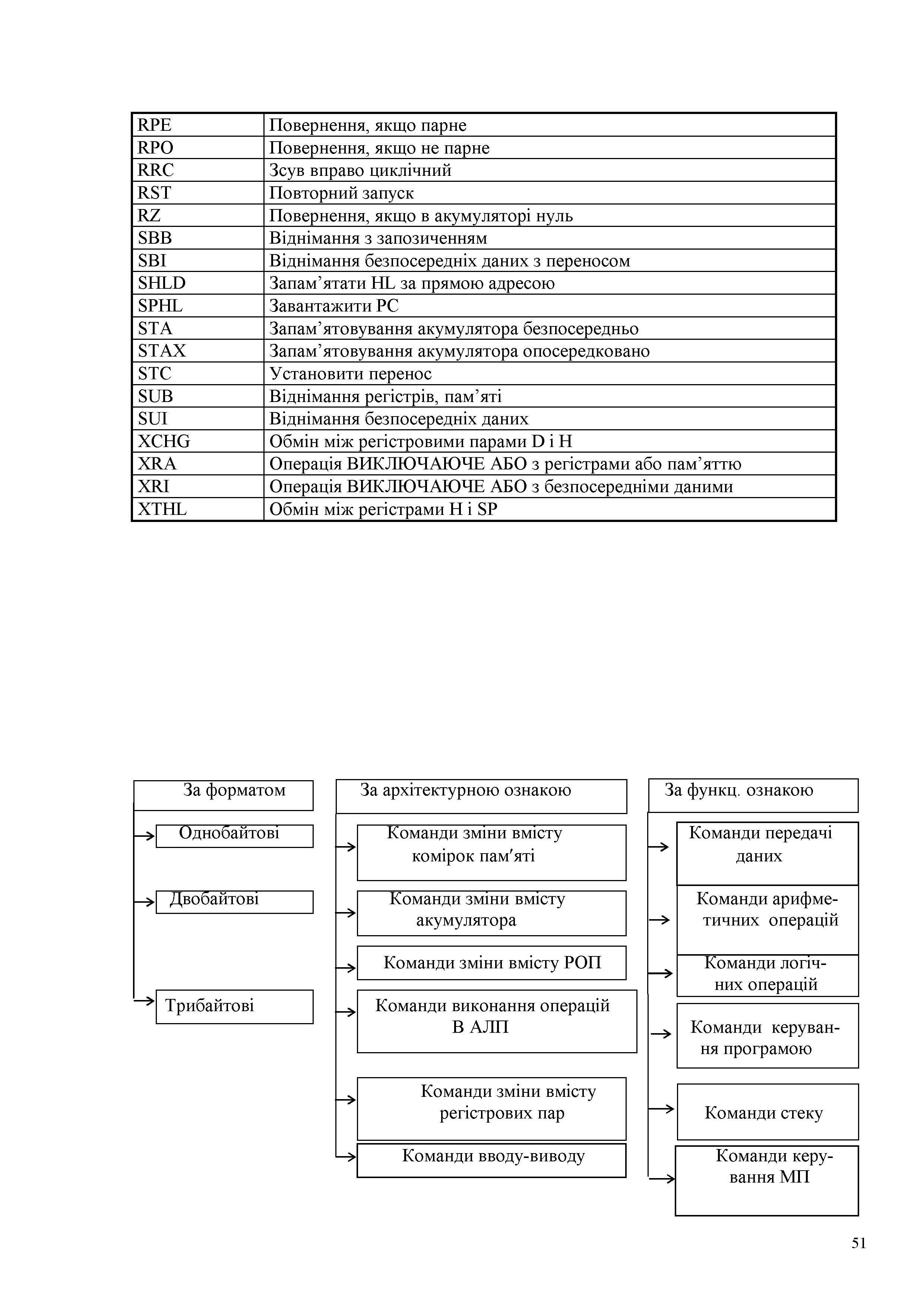

Базова система команд МП ВМ80 має 111 команд (таблиця 4.1.). Класифікація команд МП за форматом , архітектурними і функціональними ознаками приведена на рисунку 4.24.

В таблиці 4.1 приведені основні типи команд ВМ 80, їх мнемокоди на мові асемблера і призначення.

Таблиця 4.1 - Система команд мікропроцесора К 580 ВМ 80А

|

ACI |

Додати безпосередні дані з переносом |

|

ADC |

Додати з переносом |

|

ADD |

Додати однобайтові дані |

|

ADI |

Додати безпосередні дані |

|

ANA |

Логічна операція “І” |

|

ANI |

Логічна операція “І” з безпосередніми даними |

|

CALL |

Виклик процедури |

|

СС |

Виклик процедури, коли перенос |

|

СМ |

Виклик процедури, коли від`ємний знак |

|

СМА |

Інвертувати |

|

СМС |

Інвертувати перенос |

|

CMP |

Порівняти |

|

CNC |

Виклик процедури, коли немає переносу |

|

CNZ |

Виклик процедури, коли в акумуляторі не нуль |

|

CP |

Виклик процедури, коли додатній знак |

|

CPE |

Виклик процедури, коли парність |

|

CPI |

Порівняння з безпосередніми даними |

|

CPO |

Виклик процедури, коли немає парності |

|

CZ |

Виклик процедури, коли в акумуляторі нуль |

|

DAA |

Десяткова корекція акумулятора |

|

DCR |

Декрементувати регістр або пам`ять |

|

DCX |

Декрементувати регістрові пари або SP |

|

DI |

Заборона переривання |

|

EI |

Дозвіл переривання |

|

HLT |

Зупинка |

|

IN |

Зчитати значення з порту |

|

INR |

Інкрементувати регістр або пам’ять |

|

INX |

Інкрементувати регістрові пари або SP |

|

JC |

Перехід, якщо перенос |

|

JM |

Перехід, якщо від’ємний знак |

|

JMP |

Перехід безумовний |

|

JNC |

Перехід, якщо немає переносу |

|

JNZ |

Перехід, якщо в акумуляторі не нуль |

|

JP |

Перехід, якщо додатній знак |

|

JPE |

Перехід, якщо парний |

|

JPO |

Перехід, якщо не парний |

|

JZ |

Перехід, якщо в акумуляторі нуль |

|

LDA |

Завантажити безпосередньо |

|

LDAX |

Завантажити опосередковано |

|

LHLD |

Завантажити HL-пару |

|

LXI |

Завантажити регістрові пари і SP безпосередньо |

|

MOV |

Пересилки регістрові і в пам’ять |

|

MVI |

Завантажити регістри і пам’ять безпосередньо |

|

NOP |

Немає операції |

|

ORA |

Логічна операція АБО |

|

ORI |

Логічна операція АБО з безпосередніми даними |

|

OUT |

Вивести значення в порт |

|

PCHL |

Завантажити РС |

|

POP |

Розмістити значення в стеку |

|

PUSH |

Добути значення зі стеку |

|

RAL |

Зсув вліво з переносом |

|

RAR |

Зсув вправо з переносом |

|

RC |

Повернення, якщо перенос |

|

RET |

Повернення з процедури |

|

RLC |

Зсув вліво циклічний |

|

RM |

Повернення, якщо від’ємний знак |

|

RNC |

Повернення, якщо немає переносу |

|

RNZ |

Повернення, якщо в акумуляторі не нуль |

|

RP |

Повернення, якщо додатній знак |

|

RPE |

Повернення, якщо парне |

|

RPO |

Повернення, якщо не парне |

|

RRC |

Зсув вправо циклічний |

|

RST |

Повторний запуск |

|

RZ |

Повернення, якщо в акумуляторі нуль |

|

SBB |

Віднімання з запозиченням |

|

SBI |

Віднімання безпосередніх даних з переносом |

|

SHLD |

Запам’ятати HL за прямою адресою |

|

SPHL |

Завантажити РС |

|

STA |

Запам’ятовування акумулятора безпосередньо |

|

STAX |

Запам’ятовування акумулятора опосередковано |

|

STC |

Установити перенос |

|

SUB |

Віднімання регістрів, пам’яті |

|

SUI |

Віднімання безпосередніх даних |

|

XCHG |

Обмін між регістровими парами D i H |

|

XRA |

Операція ВИКЛЮЧАЮЧЕ АБО з регістрами або пам’яттю |

|

XRI |

Операція ВИКЛЮЧАЮЧЕ АБО з безпосередніми даними |

|

XTHL |

Обмін між регістрами H i SP |

Рисунок 4.24 - Класифікація команд МП ВМ80

В залежності від функціонального призначення систему команд МП поділяють на такі групи: команди передачі (пересилок) даних, команди арифметичних і логічних операцій, команди керування програмою, команди стеку і команди керування МП.

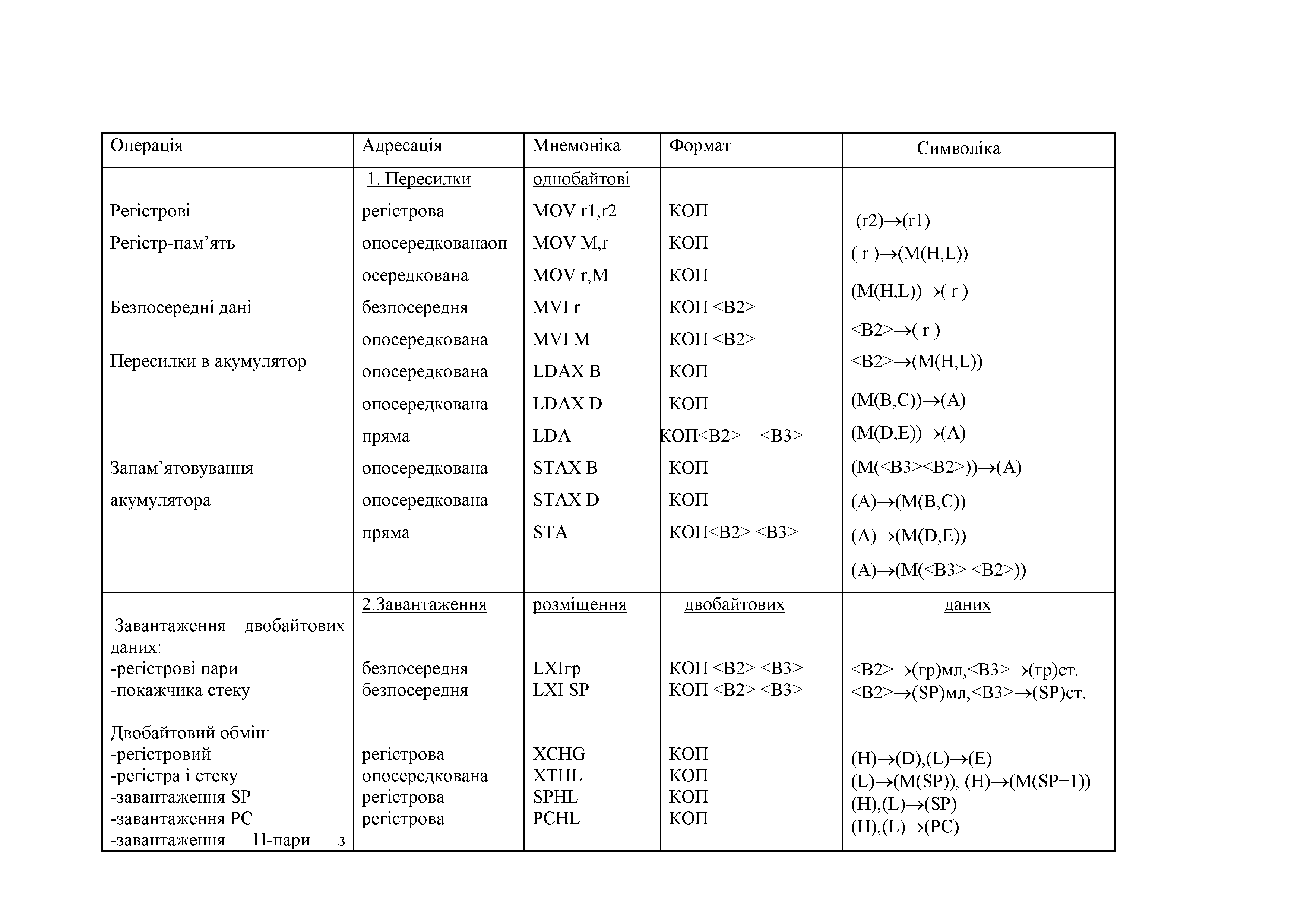

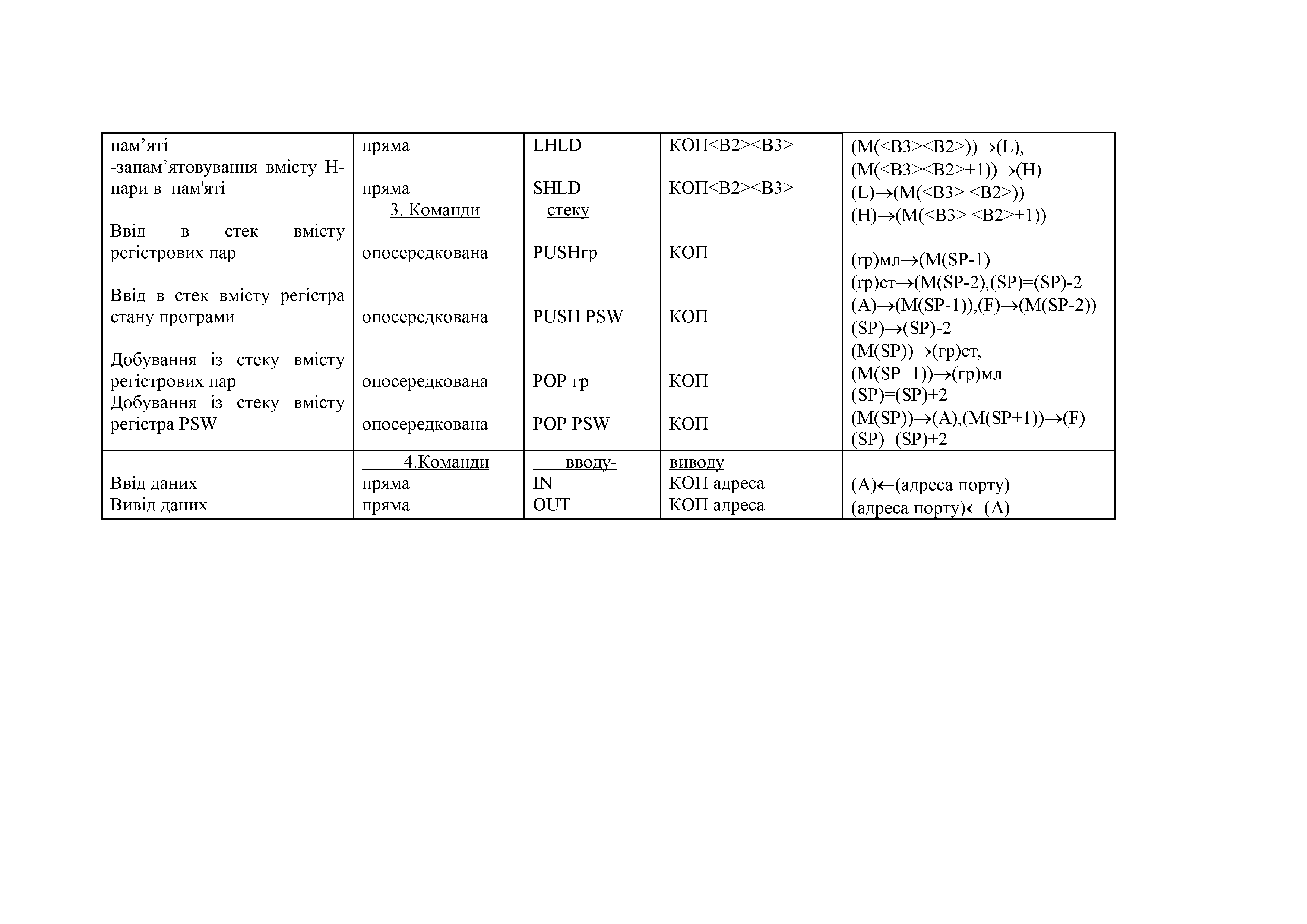

Команди передачі даних

Команди передачі даних виконують пересилання даних із регістра в регістр, розміщення даних в пам’яті, розміщення добутих з пам’яті даних, а також ввід і вивід даних через зовнішні пристрої (таблиця 4.2). Команди передачі даних поділяють на команди однобайтових пересилок, завантаження і розміщення двобайтових даних, команди стеку і вводу-виводу даних.

Кожна команда передачі містить адресу джерела і приймача даних. Способи адресації орієнтовані на те, де і як здійснюється пошук даних.

Команди арифметичних операцій

Мікропроцесор ВМ80 може використовувати операції додавання, віднімання, інкрементування, декрементування та порівняння (таблиця 4.3).

В таблиці 4.3 всі арифметичні команди розбиті на чотири підгрупи: команди додавання, віднімання, корекції акумулятора і порівняння. Більшість команд є однобайтовими, крім команд, що виконують дії з безпосередніми даними.

Таблиця 4.2 - Команди передачі даних

Примітка: ( )-вміст; (М))-вміст комірки пам’яті, адреса якої задана у внутрішніх дужках; РС-лічильник команд; SP-покажчик стеку; rр-регістрові пари D,B,H; r1, r2, r-восьмирозрядні регістри загального призначення і акумулятор; В2,В3,-другий та третій байт команд ( дані або безпосередня адреса).

Таблиця 4.3 - Команди арифметичних операцій

|

Операція |

Адресація |

Мнемоніка |

Формат |

Символіка |

Індикатори |

||||

|

С |

Z |

S |

P |

A |

|||||

|

1.Команди додавання |

|

|

|

|

|

|

|

|

|

|

-Додати А і регістр |

Регістрова |

ADD r

|

КОП |

(A)+(r) (A) |

+ |

+ |

* |

* |

* |

|

-Додати А і М |

Опосередкована |

ADD M |

КОП |

(A)+(M(H, L))(A) |

+ |

+ |

* |

* |

* |

|

-Додати А і регістр з переносом |

Регістрова |

ADC r |

КОП |

(A)+(r)+ (с) (А) |

+ |

+ |

* |

* |

* |

|

-Додати А і М з переносом |

Опосередкована |

ADC M |

КОП |

(A)+(M(H, L))+ (с)(A) |

+ |

+ |

* |

* |

* |

|

-Додати А і дані |

Безпосередня |

ADI |

КОП<B2> |

(A)+<B2>(A) |

+ |

+ |

* |

* |

* |

|

-Додати А і дані з переносом |

Безпосередня |

ACI |

КОП<B2> |

(A)+<B2>+(c)(A) |

+ |

+ |

* |

* |

* |

|

- Додавання регістрових пар |

Регістрова |

DAD rp* |

КОП |

(rp*)+(H,L)(H,L) |

+ |

- |

- |

- |

- |

|

-Інкремент регістра |

Регістрова |

INR r |

КОП |

(r)+1(r) |

- |

+ |

* |

* |

* |

|

-Інкремент пам’яті |

Опосередкована |

INR M |

КОП |

(M(H,L))+1(M(H,L)) |

- |

+ |

* |

* |

* |

|

-Інкремент регістрових пар |

Регістрова |

INX rp* |

КОП |

(rp*)+1 (rp*) |

- |

- |

- |

- |

- |

|

2. Команди віднімання |

|

|

|

|

|

|

|

|

|

|

Операція |

Адресація |

Мнемоніка |

Формат |

Символіка |

Індикатори |

||||||||

|

С |

Z |

S |

P |

A |

|||||||||

|

-Віднімання із А регістра |

Регістрова |

SUB r |

КОП |

(A)-(r) (A) |

+ |

+ |

* |

* |

* |

||||

|

-Віднімання з А пам’яті М |

Опосередкована |

SUB M |

КОП |

(A)-(M(H,L))(A) |

+ |

+ |

* |

* |

* |

||||

|

-Віднімання із А регістра з запозиченням |

Регістрова |

SBB r

|

КОП |

(A)-(r)-(c)(A) |

+ |

+ |

* |

* |

* |

||||

|

-Відняти від А пам’ять з запозиченням |

Опосередкована |

SBB M |

КОП |

(A)-M(H,L))-(c)(A) |

+ |

+ |

* |

* |

* |

||||

|

|

Безпосередня |

SUI |

КОП<B2> |

(A)-<B2> (A) |

+ |

+ |

* |

* |

* |

||||

|

-Відняти безпосередні дані з А з пе-реносом |

Безпосередня |

SBI |

КОП<B2> |

(A)-<B2>-(c)(A) |

+ |

+ |

* |

* |

* |

||||

|

-Декремент регістра |

Регістрова |

DCR r |

КОП |

(r)-1(r) |

- |

+ |

* |

* |

* |

||||

|

-Декремент пам’яті |

Опосередкована |

DCR M

|

КОП |

(M(H,L))-1(M(H,L)) |

- |

+ |

* |

* |

* |

||||

|

-Декремент регістрової пари |

Регістрова |

DCX rp*

|

КОП |

(rp*)-1(rp*) |

- |

- |

- |

- |

- |

||||

Продовження таблиці 4.3

Продовження

таблиці 4.3

|

Операція |

Адресація |

Мнемоніка |

Формат |

Символіка |

Індикатори |

||||||||

|

С |

Z |

S |

P |

A |

|||||||||

|

3. Команда корекції акумулятора |

|

DAA |

КОП |

Десяткова корекція А |

+ |

+ |

* |

* |

* |

||||

|

4. Команди порівняння |

|

|

|

|

|

|

|

|

|

||||

|

-Порівняння А і регістра |

Регістрова |

CMP r |

КОП |

(А)=(r) якщо рівне z=1;A<r,c=1 |

+ |

+ |

* |

* |

* |

||||

|

-Порівняти А і пам’ять |

Опосередкована |

CMP M |

КОП |

(A)=M(H,L)) дія на індикатори такаж |

+ |

+ |

* |

* |

* |

||||

|

-Порівняти А з даними |

Безпосередня |

CPI |

КОП<B2> |

(A)=<B2> дія на індикатори такаж |

+ |

+ |

* |

* |

* |

||||

Примітка : ( )-вміст;

(М( ))-вміст комірки пам’яті, адреса якої

задана у внутрішніх дужках; r-восьмирозрядні

регістри A,B,C,D,E,H,L; rp*-регістрові пари

H,D,B,SP; В2- другий байт команди;

+-установлюється індикатор; *-стан

індикатора важко передбачити програмісту;

- -команда не діє на індикатор (його стан

непередбачуваний) .

Команди маніпулювання бітами (Логічні операції)

Команди даної групи дозволяють маніпулювати окремими бітами байтових даних шляхом виконання найуживаніших логічних операцій та зсувів (таблиця 4.4).

Із таблиці видно, що команди маніпулювання бітами можна поділити на 5 підгруп: команди І, АБО, ВИКЛЮЧАЮЧЕ АБО, інвертування, установки переносу та зсувів. Більшість команд є однобайтовими (крім двобайтових команд з безпосередніми даними). Ядром більшості операцій є акумулятор.

Команди керування мікропроцесором

МП має низку команд, які керують його роботою. Перелік цих команд зведений в таблицю 4.5.

Команди дозволу (заборони) переривань ЕІ(DI), установлюють внутрішній тригер дозволу переривань в стан ‘’1’’(‘’0’’), тоді МП реагує (не реагує) на запити переривань, які надходять від зовнішніх пристроїв, що ініціюють обмін.

Команда неробочого ходу (немає операції) NOP відповідає відсутності виконання всяких операцій на протязі 1 або 2 мкс. Це однобайтова команда, єдиним ефектом якої є інкремент лічильника команд. Команда може використовуватись для забивки неправильних команд, які виявлені в ході відладлагодження програми або для формування часових інтервалів в циклах часової затримки.

Команда ЗУПИНКА використовується в кінці програми для зупинки МП. В цьому випадку тільки ОБНУЛЕННЯ або команда виклику переривань може дозволити новий запуск МП.

Команди керування програмою

Команди даної групи змінюють послідовність нормального ходу програми. Сюди входять команди переходів, виклику, повернення і повторного запуску.

Команди приведені в таблиці 4.6 двох типів: умовних і безумовних переходів. Безумовні переходи просто виконують операцію, визначену лічильником команд РС; умовні - перевіряють стан одного з індикаторів МП для визначення доцільності даного розгалуження. Умови, позначені в таблиці ідентифікатором Х, уточнюються в наступній формі:

|

Умови (ідентифікатор Х) |

Умови (ідентифікатор Х) |

|

NZ-не нуль (Z=0) |

PO-непарність (Р=0) |

|

Z-нуль (Z=1) |

PE-парність (Р=1) |

|

NC-немає переносу (C=0) |

P-плюс (S=0) |

|

C-перенос (C=1) |

M-мінус (S=1) |

Команди керування програмою є трибайтовими, крім команд повернення і рестарту (вони однобайтові). Другий та третій байт команди є адресою переходу. Всі команди не діють на індикатори регістра ознак.

Таблиця 4.4 - Команди маніпулювання бітами.

|

Операція |

Адресація |

Мнемоніка |

Формат |

Символіка |

Індикатори |

||||

|

|

|

|

|

|

C |

Z |

S |

P |

А |

|

1. Логічне множення |

|

|

|

|

|

|

|

|

|

|

-Логічне множення А і r |

регістрова |

ANA r |

КОП |

(A) |

0 |

+ |

* |

* |

- |

|

-Логічне множення А і пам’ять |

Опосередкована |

ANA M |

КОП |

(A) |

0 |

+ |

* |

* |

- |

|

-Логічне множення А і даних |

Безпосередня |

ANI |

КОП <B2> |

(A) |

0 |

+ |

* |

* |

- |

|

2.Логічне сумування |

|

|

|

|

|

|

|

|

|

|

-Логічне АБО А і r |

Регістрова |

ORA r |

КОП |

(A) |

0 |

+ |

* |

* |

- |

|

-Логічне АБО А і пам’яті |

Опосередкована |

ORA M |

КОП |

(A) |

0 |

+ |

* |

* |

- |

|

-Логічне АБО А і дані |

Безпосередня |

ORI |

КОП <B2> |

(A) |

0 |

+ |

* |

* |

- |

|

3. Заперечення рівно-значності: |

|

|

|

|

|

|

|

|

|

|

-Виключаюче АБО А і r |

Регістрова |

XRA r |

КОП |

(A) |

0 |

+ |

* |

* |

- |

|

-Виключаюче АБО А і пам’яті |

Опосередкована |

XRA M |

КОП |

(A) |

0 |

+ |

* |

* |

- |

|

-Виключаюче АБО А і даних |

Безпосередня |

XRI |

КОП <B2> |

(A) |

0 |

+ |

* |

* |

- |

Продовження

таблиці 4.4

Продовження

таблиці 4.4

|

Операція |

Адресація |

Мнемоніка |

Формат |

Символіка |

Індикатори |

||||

|

C |

Z |

S |

P |

А |

|||||

|

4.Команди інвертуван-ня і установки переносу |

|

|

|

|

|

|

|

|

|

|

Інвертування А |

Неявна |

CMA |

КОП |

(A)

|

- |

- |

- |

- |

- |

|

Інвертувати Пернос: |

Неявна |

CMC |

КОП |

(c)

|

+ |

- |

- |

- |

- |

|

Установити перенос |

неявна |

STC |

КОП |

1 |

+ |

- |

- |

- |

- |

|

5.Зсуви: |

|

|

|

|

|

|

|

|

|

|

Зсув вліво циклічно |

неявна |

RLS |

КОП |

|

+ |

- |

- |

- |

- |

|

Зсув вправо циклічно |

неявна |

RRC |

КОП |

|

+ |

- |

- |

- |

- |

|

Зсув вліво з переносом |

неявна |

RAL |

КОП |

|

+ |

- |

- |

- |

- |

|

Зсув вправо з переносом |

неявна |

RAR |

КОП |

|

+ |

- |

- |

- |

- |

Примітка:

( )-вміст; (М( ))-вміст комірки пам’яті;

r-регістри A, B, C, D, E, H, L; В2-другий байт

команди; +- індикатор установлюється;

*-індикатор установлюється, але його

важко передбачити програмісту; -

-індикатор не встановлюється;

![]() -операція

"I";

-операція

"I";

![]() -операція

"АБО";

-операція

"АБО";![]() -операція "ВИКЛЮЧНЕ АБО".

-операція "ВИКЛЮЧНЕ АБО".

Таблиця 4.5 - Команди керування мікропроцесором.

|

Операція |

Адресація |

Мнемоніка |

Формат |

Символіка |

|

Дозвіл переривання |

|

ЕІ |

КОП |

Тригер переривання установлюється в ‘’1’’, переривання дозволено |

|

Заборона переривання |

|

DI |

КОП |

Тригер переривання установлюється в ‘’0’’, переривання заборонено |

|

Команди неробочого ходу |

Неявна |

NOP |

КОП |

Порожня операція. Програма виконується за наступною адресою (РС)=(РС)+1 |

|

Зупинка |

Невід’ємна (апаратна) |

HLT |

КОП |

Робота МП припиняється. (РС)=(РС)+1; (SP)=(SP)+2 |

Примітка: ( )-вміст; PC-лічильник команд.

Таблиця 4.6 – Команди керування ходом програми

|

Операція |

Адресація |

Мнемоніка |

Формат |

Символіка |

|

Перехід безумовний Перехід за умовою |

Безпосередня Безпосередня |

1.Переходи: JMP JX

|

КОП<B2><B3> КОП<B2><B3>

|

<B2><B3>(PC) Якщо умова виконується, тоді <B2><B3>(PC), інакше (РС)=(РС)+3 |

|

виклик безпосередній

Виклик умовний |

Безпосередня, опосередкована

Безпосередня, опосередкована |

2.Виклики процедури: CALL

CX |

КОП<B2><B3>

КОП<B2><B3> |

<B2><B3>(PC); (PC)(SP-1) (SP-2) ; (SP)=(SP)-2

Якщо умова виконується,тоді <B2><B3>(PC); (PC)(SP-1);(SP-2); (SP)=(SP)-2, інакше (PC)=(PC)+3 |

|

Повернення безумовне

Повернення умовне |

Опосередкована

Опосередкована |

3.Повернен RET

RX |

ня: КОП

КОП |

(SP+1)(SP)(PC), (SP)=(SP)+2

Якщо умова виконана, тоді (SP+1)(SP)(PC); (SP)=(SP)+2, інакше (PC)=(PC)+1 |

|

|

Опосередкована |

4.Повторни RCTx |

й запуск КОП |

(PC)(SP-1)(SP-2);(SP)=(SP)-2; (PC)8(NNN); X=NNN |

4.2 16-розрядний мікропроцесор 8086

Мікропроцесор 8086 фірми Intel є базовим 16-розрядним процесором в родині 8080.Удосконалене функціональне ядро 8086 є основою низки сучасних МП даної родини (80186,80286,80386... PENTIUM).Освоєння даного мікропроцесора будемо здійснювати на прикладі повного функціонального аналога К1810В86 МПК серії К1810,виробником якого є країни СНД і який добре описаний в навчальній літературі.

-Відняти

безпосередні дані з А

-Відняти

безпосередні дані з А