- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

Адресування пам'яті і організація вводу-виводу

1) Розміщення байтів і слів в пам'яті.

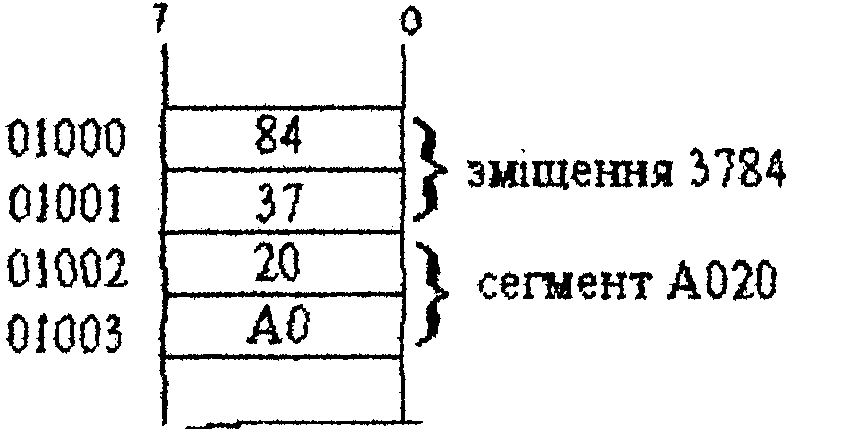

Пам'ять логічно організована як одновимірний масив байтів, кожний з яких має 20-бітову фізичну адресу в діапазоні 00000-FFFFF. Будь-які два суміжних байти в пам'яті можна розглядати як 16-бітове слово. Молодший байт слова має меншу адресу, а старший-більшу. Повна інформація, необхідна для визначення фізичної адреси, міститься в покажчику адреси. Для запам'ятовування покажчика адреси необхідно два слова пам'яті, причому слова з меншою адресою завжди містить зміщення, а з більшою-базову адресу сегмента.

Рисунок 4.28-Розміщення слова в памяті.

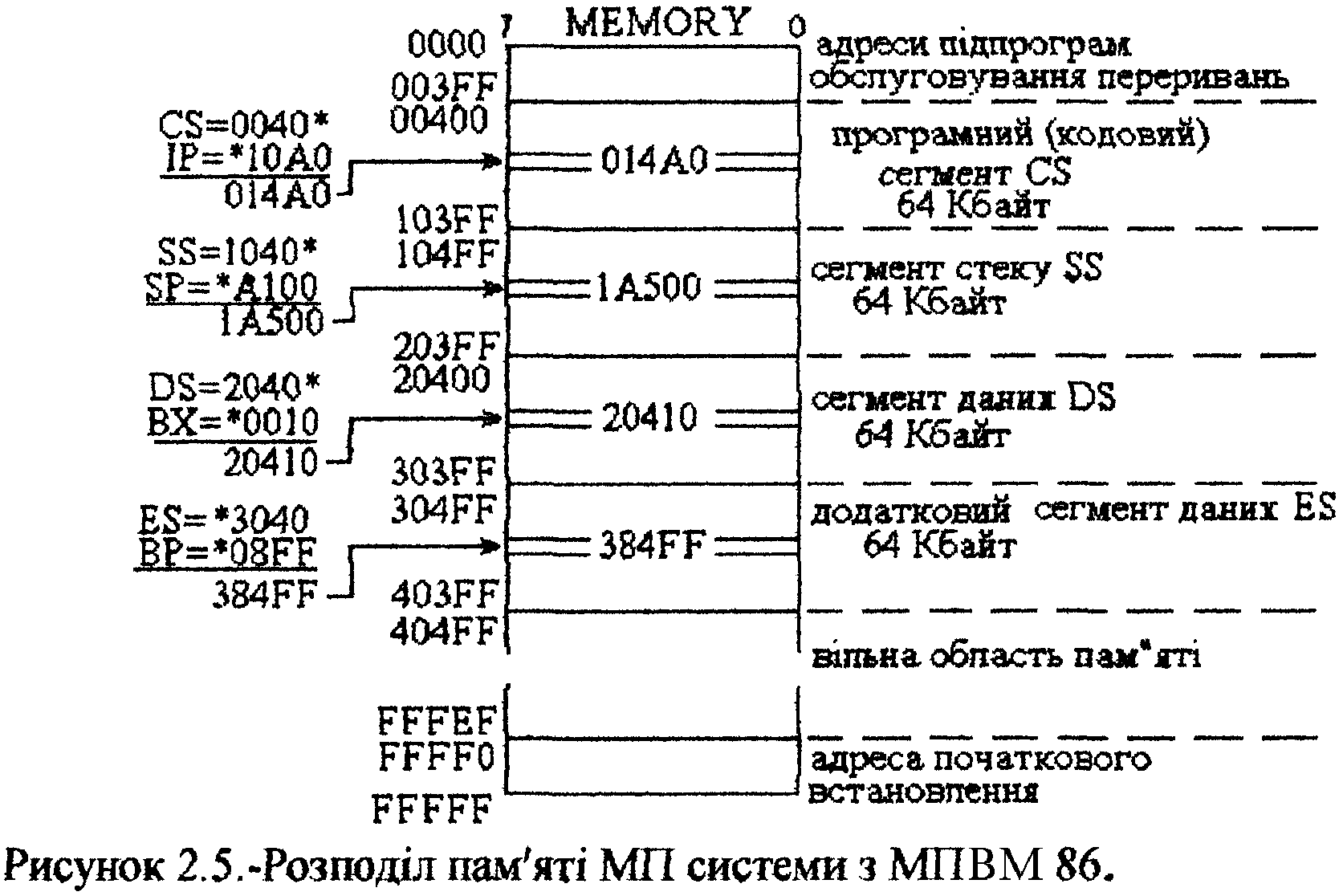

2) Сегментація пам'яті і обчислення адреси.

Простір пам'яті в 1 МБайт представляється як набір сегментів, що визначаються пограмним шляхом. Сегмент складається з суміжних комірок пам'яті і є незалежною і окремо заадресованою одиницею пам'яті ємністю в 64 КБайт. Кожному сегменту програмою призначається початкова (базова) адреса, що є адресою першого байта сегмента в просторі пам'яті. Оперативна та постійна пам'ять МП системи на основі МП 86 утворюють єдиний простір пам'яті із спільною адресацією 1048576 8-розрядних комірок від 00000 до FFFFF. Двобайтові операнди займають дві сусідні комірки, причому молодший байт операндa розміщається у комірці з меншою адресою, яка і вважається адресою цілого операндa. Комірки з адресами від 00000 до 003FF, а також від FFFF0 до FFFFF бажано зарезервувати для обслуговування переривань та для початкового встановлення МП системи при включенні живлення. Максимальна ємність кожного з сегментів пам'яті- 64 КБайт, тобто одночасно МП має доступ до 256 КБайт пам'яті. На рисунку 4.29 наведений приклад розміщення сегментів у просторі пам'яті МП системи.

При необхідності збільшення об'єму будь-якого з сегментів потрібна зміна початкової адреси у відповідному сегментному регістрі. Будь-який з сегментів може бути відсутній, а для нескладних програм, де загальний обсяг оперативної та постійної пам'яті не перевищує 64 КБайт, всі сегменти можна об'єднати (сегментні регістри мають однакову початкову адресу). Початкові адреси чотирьох сегментів записують в регістри СS, DS, SS і ЕS, тим самим фіксуючи біжучі сегменти коду, даних, стеку і додаткових даних. Для звернення до команд і даних, які знаходяться в інших сегментах, необхідно змінити вміст сегментних регістрів, що дозволяє використовувати весь простір пам'яті. Сегментні регістри ініціалізуються програмним шляхом при запису в них відповідних констант.

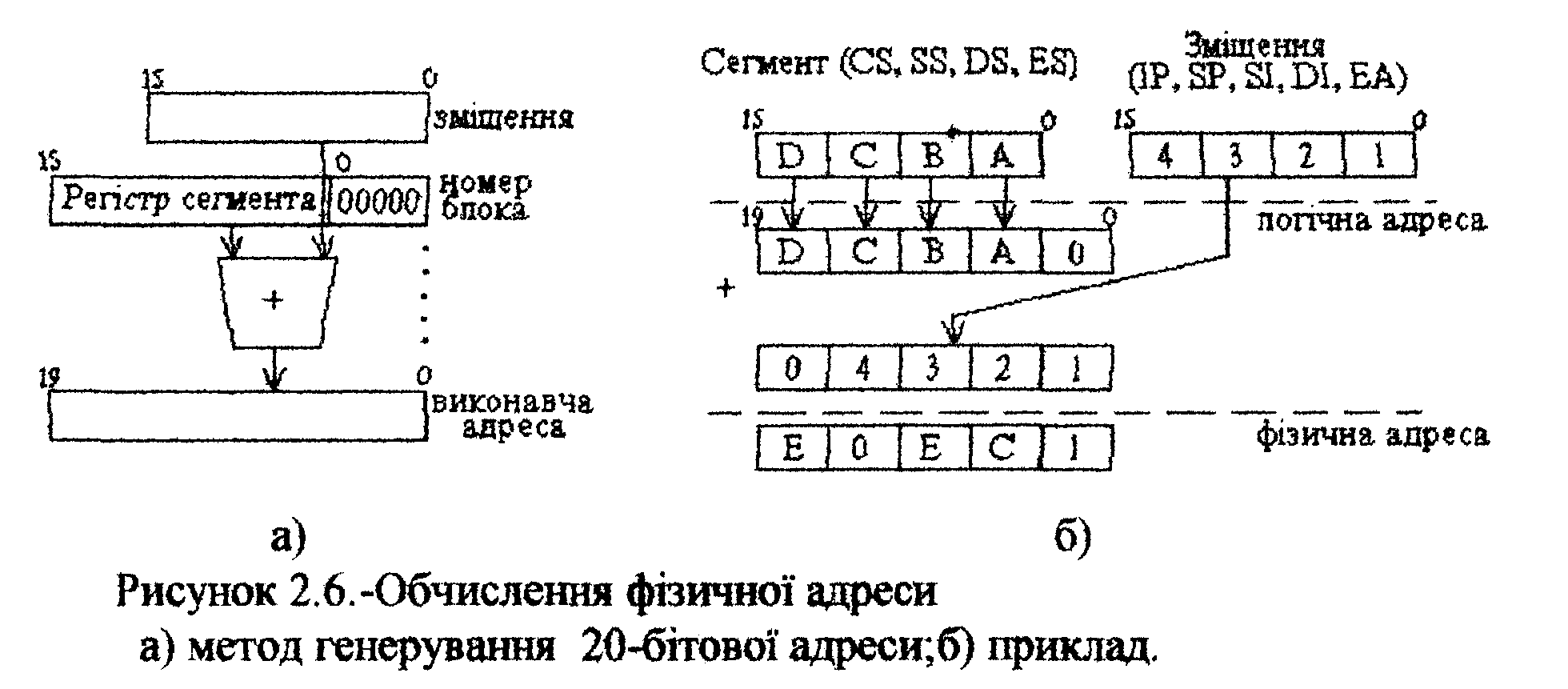

МП ВМ 86 генерує 20-бітову адресу за таким алгоритмом:

фізична адреса=зміщення+16•(регістр сегмента).

На рисунку 2.6 поданий приклад обчислення фізичної адреси:

Для обчислення фізичної адреси база сегмента зміщується на 4 біти вліво і сумується зі зміщенням. На малюнку приведені можливі джерела компонентів логічної адреси (ЕА-ефективна адреса, яка обчислюється у відповідності до способу адресації).

Джерела логічної адреси для різних типів звернення до памяті приведені в таблиці 4.11.

Таблиця 4.11.

|

Тип звернення до памяті |

Сегмент (без означення) |

Варіант |

Зміщення |

|

Вибірка команд |

СS |

Hемає |

IP |

|

Стекові операції |

SS |

Немає |

SР |

|

Змінна |

DS |

СS,SS,ЕS |

ЕА |

|

Ланцюжок-джерело |

DS |

СS,SS, ЕS |

SI |

|

Ланцюжок-приймач |

ЕS |

Нема |

DI |

|

ВР як базовий регістр |

ЕS |

СS,SS, ЕS |

EA |

Таким чином, команди завжди вибираються із біжучого сегмента коду у відповідності з логічною адресою СS:ІР. Стекові команди завжди звертаються до сегмента стеку за адресою SS:SР. Якщо при обчисленні адреси EА використовується регістр ВР, тоді звернення відбувається до стекового сегмента, але при цьому він функціонує як ОЗП з довільною вибіркою.

2) Організація вводу-виводу

Ввід-вивід даних може здійснюватися двома способами: з використанням адресного простору вводу-виводу і з використанням загального з памяттю адресного простору, тобто відображенням на память.

При першому способі використовуються спеціальні команди IN (ввід) і ОUТ (вивід), які забезпечують передачу даних між акумуляторами АL або АХ і адресованими портами. При використанні цих команд генеруються сигнали М/IО=0, які забезпечують вибір простору вводу-виводу і в сукупності з сигналами WR і RD формуються системні сигнали IOW і IOR для керування операціями запису даних в порт або читання з порта.

Команди ЇN і OUT можуть використовувати пряму адресацію, коли адреса порту представлена константою у другому байті команди і опосередковану, коли адреса розмішується в регістрі DХ. В першому випадку можна заадресувати до 256 портів для вводу і виводу даних. В другому забезпечується адресний простір до 64 К 8-бітових портів.

При другому способі адреси портів розміщуються в загальному адресному просторі. Це підвищує гнучкість програмування, оскільки для вводу-виводу можна використати будь-яку команду звернення до памяті.

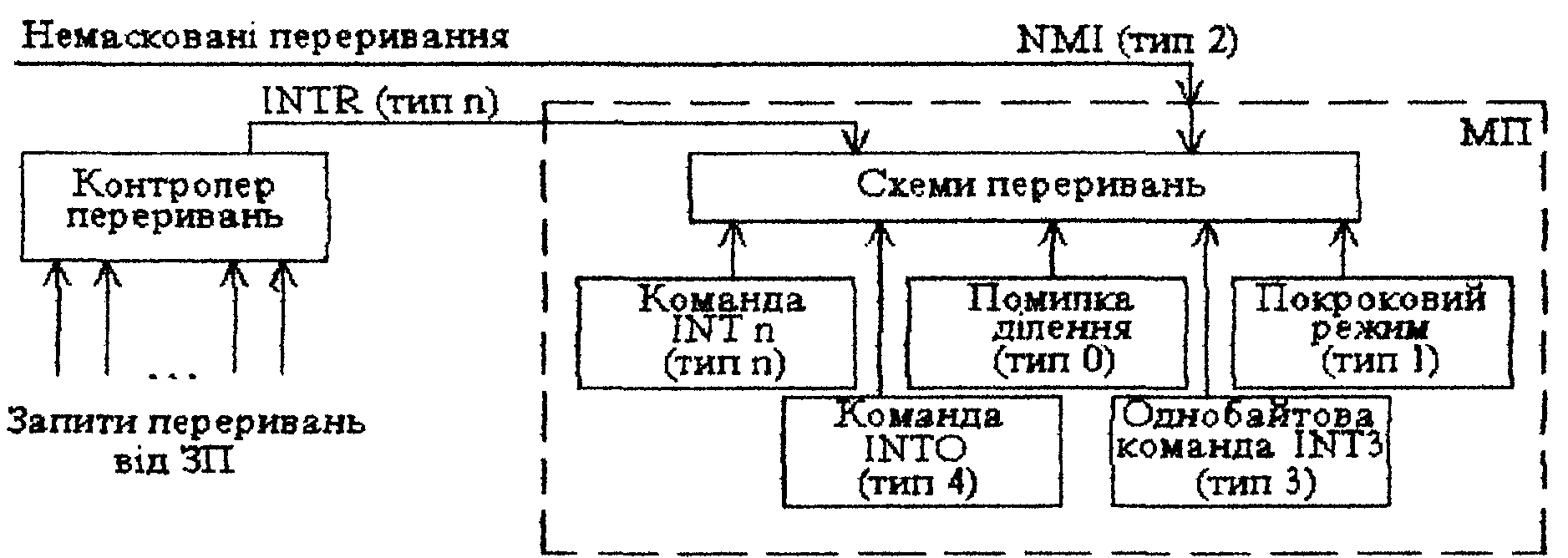

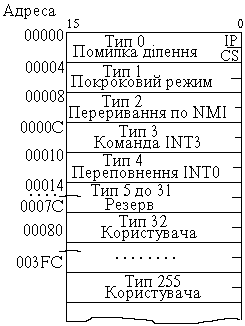

Організація переривань

Мікропроцесор ВМ 86 має ефективну систему переривань, в якій кожному перериванню поставлений у відповідність код (від 0 до 255). Переривання можуть ініціюватись зовнішніми пристроями (зовнішнє переривання) або командами програмних переривань, а також інколи-автоматично самим МП (внутрішнє переривання). Можливі джерела переривань показані на рисунку 4.31.

Рисунок 4.31 -Джерела переривань

Переривання заставляє МП тимчасово зупинити виконання поточної програми і перейти до виконання підпрограми обробки переривань. При цьому в стеці запамятовується адреса повернення (СS і РІ) і вміст регістра індикаторів F, а спеціальними командами на початку і в кінці підпрограми зберігають та відновлюють вміст інших необхідних регістрів.

Зовнішнє переривання. Запит на зовнішнє переривання поступає в МП двома входами: ІNTR і NМІ. Запит на масковані переривання від ЗвП надходять на програмований контролер переривань К1810 ВМ59А, який формує сигнал на вхід INTR=1. Дія МП залежить від стану індикатора IF дозволу переривання. Якщо IF=0, переривання по входу заборонено (замасковано) і МП переходить до іншої команди. Коли МП відповість на сигнал ІNTR, підтвердженням INТА=1 і ІF=1, то він розпізнає запит переривання і обробляє його (в другому такті INТА2, контролер переривань посилає байт, що характеризує тип переривань). Станом індикатора ІF програміст може керувати при допомозі команди SТІ (установка) і СLI (обнуління).

Запит на немасковані переривання по входу NMI використовуються для переривань роботи МП в аварійних ситуаціях (пропадання живлення, виявлення помилок пам'яті тощо). Перериваня відбуваються за переднім (додатнім) фронтом на вході NМІ, при цьому МП формує код типу 2. Стан індикатора IF не впливає на даний тип переривань.

Внутрішнє переривання характеризується типом переривань, які або передбачені або містяться в коді команд.

Переривання за помилкою ділення (тип 0) генерується МП після виконання команд ділення DIV і IDIV, якщо результат ділення перевищує формат приймача або при діленні на нуль.

Переривання по переповненню (типу 4) генерується однобайтовою командою INTО, якщо установлений індикатор ОF.

Покрокове переривання (тип 1) генерується автоматично при ТF=1 після виконання кожної команди. Стан індикатора ТF можна задати тільки через стек шляхом накладання відповідної маски на вміст регістра F в стеку.

Переривання, яке визначається користувачем при складанні програм, здійснюється двобайтовою командою INТ n в якому тип переривання вказується у другому байті команди. Команда ІNТ n викликає необхідну підпрограму, як і команда САLL.

Однобайтова команда INТЗ викликає переривання типу 3, яке визначає переривання контрольної точки. Контрольною точкою може бути будь-яке місце в програмі, де відбувається переривання і здійснюються деякі спеціальні дії (індикація вмісту регістрів, памяті і портів при відлагодженні).

Процедура обслуговування переривань. Звязок між кодом, який визначає тип переривання і підпрограмою обслуговування переривань встановлюється при допомозі таблиці вказівників векторів переривань (рисунок 4.32). Повна таблиця займає 1 КБайт памяті і містить 256 елементів. Кожний елемент таблиці містить два слова, які визначають початкову логічну адресу підпрограми. Слово з більшою адресою є базова адреса сегмента, а слово з меншою адресою-зміщення програми від початку кодового сегмента.

Структура підпрограми переривань повинна бути такою:

1) Занести в стек ті регістри МП, які будуть використані в підпрограмі;

2) Дозволити, якщо необхідно, зовнішнє переривання командою STI;

3) Забезпечити заборону повторного переривання за процедурою даного вектора переривань;

4) Основна процедура обслуговування переривань;

5) Заборонити переривання по входу INTR, командою CLI;

6) Відновити вміст регістрів, занесених в стек;

7) Дозволити переривання по входу INTR командою STI;

8) Вихід з підпрограми IRET.

Рисунок 4.32

Функціонування мікропроцесора

Виконання команд можна представити послідовністю циклів шини (циклів обміну), протягом яких МП звертається до памяті за командами або

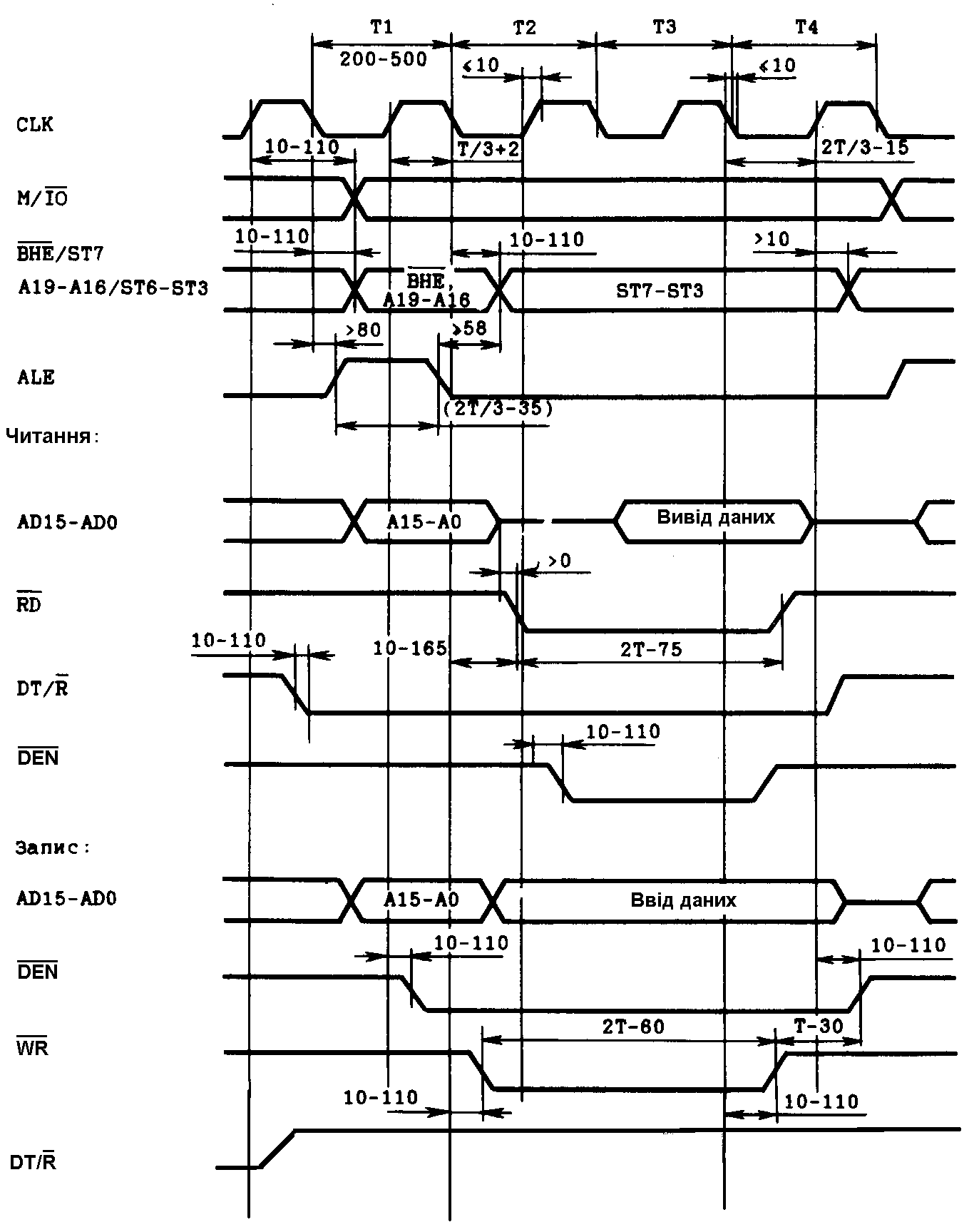

обмінюється даними з периферійними пристроями. Кожний цикл шини ініціюється пристроєм шинного інтерфейсу і містить чотири обовязкові такти Т1-Т4. В такті Т1 видається адреса на суміщену шину адреси/даних, в такті Т2 здійснюється комутація напрямку передачі, в тактах Т3 і Т4-передача даних.Функціонування МП ВМ86 в мінімальному режимі ілюструється діаграмами на рисунку 4.33.

Рисунок 4.33-Часові діаграми роботи ВМ86 в мінімальному режимі

Цикл починається з формування в такті Т1 сигналу М/IO, який визначає тип пристрою (запамятовуючий пристрій чи зовнішній пристрій), до якого відбувається звернення для пересилки даних. Тривалість сигналу М/IO рівна тривалості циклу шини, і він використовується для селектування адреси пристрою. В такті Т1 і на початку Т2 МП формує адресу запамятовуючого пристрою (ЗпП) на лініях А19-А16 і AD15-AD0 або адресу зовнішнього пристою (ЗвП) на лініях AD15-AD0, а також виробляє сигнал ВНЕ, який сумісно з А0 визначає передачу слова або одного з байтів. Одночасно формується строб адреси ALE, за спадом якого адреса фіксується у внутрішніх регістрах-фіксаторах, на виході яких адреса зберігається протягом всього циклу шини.

В такті Т2 відбувається перемикання шин: на лініях А19/S6-A16/S3 появляються сигнали стану S6-S3, які зберігаються до кінця такту Т4.

В циклі читання в такті Т2 лінії AD15-AD0 переходять в третій стан до появи даних від адресованого пристрою. В такті Т2-Т4 виробляється сигнал читання RD=0, який вказує цьому пристрою на необхідність передачі даних. Для керування буферами даних, які підключені до ліній AD15-AD0, в тактах Т2-Т4 формується сигнал , який дозволяє передачу даних. Напрям передачі даних при читанні визначається сигналом DT/R=0, який діє протягом всього циклу.

Після виконання читання і установлення сигналу RD=1 МП закінчує такт Т4 наступним чином: лінії А15-А0 переходять в третій стан, сигнали М/IO, DE, DT/R, S7-S3 неактивні, буфери даних відключені від каналу.

В циклі запису в такті Т2 адреса на лініях AD15-AD0 замінюється даними, які треба записати в адресований пристрій. Дaні залишаються дійсними до середини такту Т4 і супроводжуються сигналом WR=0, який є стробом запису даних в пристрій. Сигнал DE=0 появляється в такті Т1 і використовується для підготовки буферів до передачі даних.

Сигнал DT/R=1, який перемикає буфери на передачу даних в напрямку до МП, утримується протягом всього циклу запису. Після установки WR=1 такт Т4 закінчуєтся аналогічно до циклу читання.

Таким чином, цикл читання і запису розрізняються не тільки активними значеннями сигналів RD або WR і станом сигналу DT/R, але і тим, що в циклі запису сигнали DE і WR стають активними раніше і мають більшу тривалість, ніж в циклі читання.

Крім основного режиму роботи МП ВМ86 характеризується особливими станами та режимами роботи.

Стан «зупинка» мікропроцесора ініціюється командою HLT, аналогічно до МП КР 580 ИК80. Вихід з цього стану можливий за умови надходження сигналів зовнішніх переривань або сигналу початкової установки.

Початкова установка забезпечується високим рівнем сигналу на вході RESET (CLR) мікропроцесора. При цьому зупиняється виконання всіх внутрішніх операцій і процесор починає процес початкової ініціалізації регістрів, який триває 10 тактів, і полягає у встановленні в нульовий стан індикаторів IF, TF, покажчика команд ІР та сегментних регістрів DS, ES i SS. До кодового сегментного регістру CS заноситься значення FFFF, що призводить до адресації першої команди програми з адресою FFFF0. Як правило, першою командою програми є команда безумовного переходу JMP до початку виконання програми.

Робота МП ВМ86 при виконанні команди WAIT (очікування) забезпечує синхронізацію із зовнішініми процесами. Під час дії команди WAIT стан мікропроцесора буде визначатись сигналом на вході TEST. Якщо на цьому вході високий рівень сигналу МП відключає свої магістральні шини від системи і очікує появи сигналу низького рівня на вході TEST. При появі і підтримці його на даному рівні на протязі шести машинних тактів процес виконання команд продовжується у звичайному порядку.

Режим прямого доступу до памяті аналогічний як і для процесора КР 580 ИК 80. Він ініціюється подачею на вхід HOLD ВМ86 одиничного сигналу запиту. По завершенні поточного машинного циклу МП формує сигнал HLDA підтвердження захоплення і переводить свої шини в третій стан.

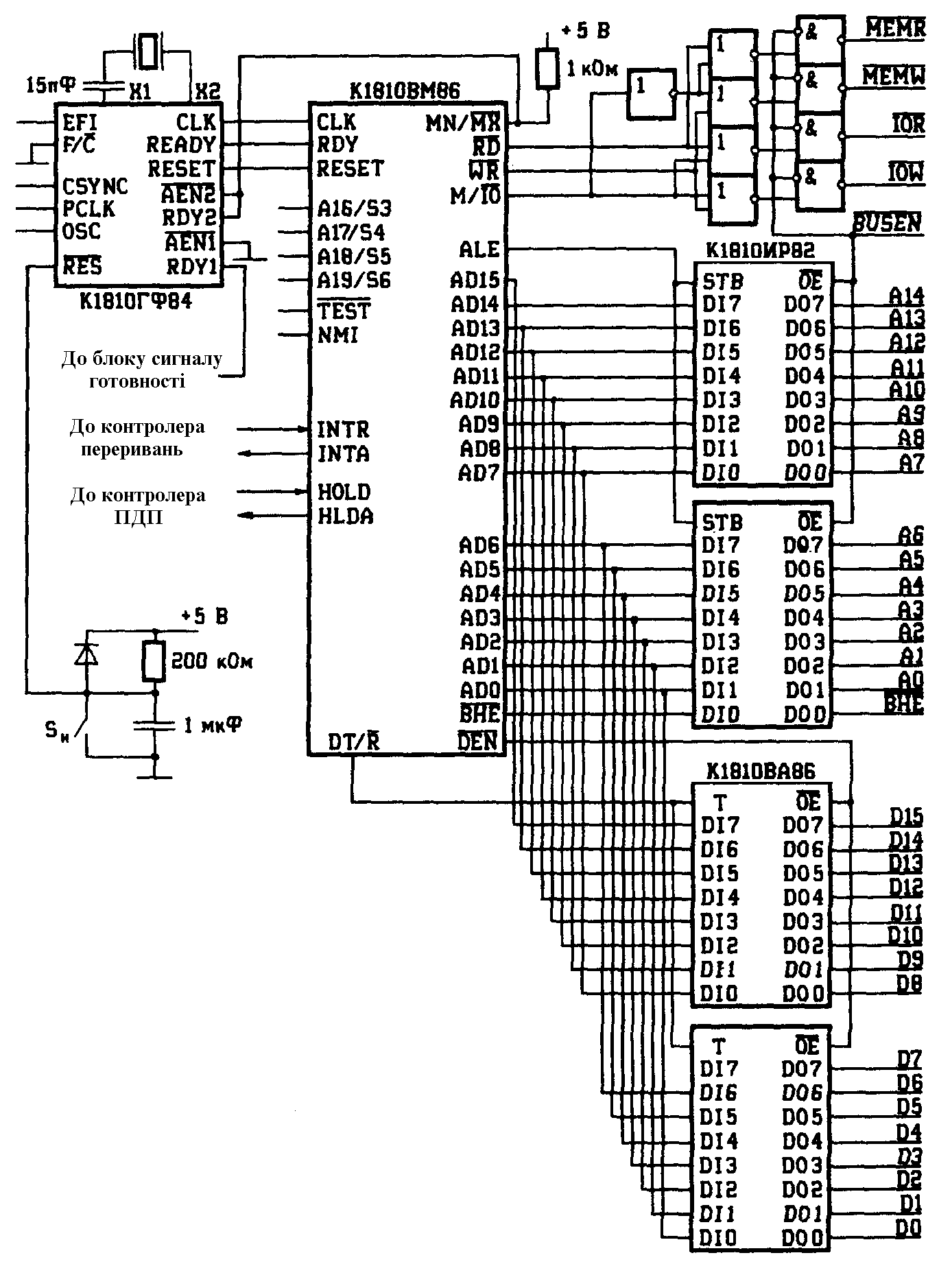

Побудова блока центрального процесора

В однопроцесорних мікроЕОМ та мікроконтролерах МП ВМ86 працює в мінімальному режимі (MN/MX=1).При розробці структури блоку центрального процесора (ЦП) (рисунок 4.34) виникають задачі поділу (демультиплексування) шини адреси/даних (ШАД), буферування шин адреси (ША) і шини даних (ШД), а також формування системних керуючих сигналів для блоку памяті і зовнішніх пристроїв.

Перша задача вирішується при допомозі інтегральної схеми (ІС) К1810 ИР 82/83, яка виконує функції адресного фіксатора. Так як сигнал ВНЕ формується в той же інтервал часу, що і адресні сигнали, то його теж необхідно зафіксувати у фіксаторі. Тому на рисунку два 8-бітових регістри К1810 ИР82 забезпечують запамятовування 16 розрядів адреси. Для доступу до памяті ємністю в 1 МБайт необхідно підключити ще один регістр, на який подаються решта старших розрядів AD15, A19/S6-A16/S3.

Друга задача розвязується при допомозі двонаправлених 8-бітових шинних формувачів К1810 ВА86/87, які підсилюють сигнали системної шини даних.

Третя задача може бути розвязана при допомозі комбінаційних логічних схем, які формують необхідні керуючі сигнали на основі сигналів, які виробляє МП. Якщо в системі використовується адресний простір вводу-виводу, ізольований від простору памяті, то доцільно сформувати сигнали при допомозі системного контролера. Ці сигнали керують запамятовуючими

Рисунок 4.34-Структурна схема ЦП на основі ВМ86.

та зовнішніми пристроями. Роль формувачів цих сигналів можуть виконувати (рисунок 4.34) елементи АБО-НІ або дешифратор на три входи (наприклад К155 ИД7). Якщо ж в МПС ввід-вивід організований з відображенням на память, тоді сигнал M/IO не використовується і на ЗпП та ЗвП подаються сигнали RD i WR після підсилення.

Використані підсилювачі і формувачі повинні забезпечувати три вихідних стани для організації прямого доступу до памяті. В цьому випадку після переводу МП в стан захоплення ці підсилювачі переходять в третій стан за сигналом BUSEN від контролера ПДП. Якщо захоплення шин і обмін даними через ПДП не передбачений, то необхідність в такому підключенні відпадає.