- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

-

Двійкова арифметика

Більшість мікропроцесорів мають команди додавання і віднімання двійкових чисел, деякі, крім того, мають команди множення та ділення.

Операції множення та додавання виконуються аналогічно до арифметики десяткових чисел (рисунок 2.3)

1 1 1 1 Переноси 1

1-й доданок +00111011 +59

2-й доданок 00101010 42

сума

1100101(2)

101(10)

сума

1100101(2)

101(10)

а)

множене х1101 х13

множник 101 5

1

-й

проміжний добуток 1101

65(10)

-й

проміжний добуток 1101

65(10)

2-й проміжний добуток 0000

3-й проміжний добуток 1101

Добуток

1000001(2)

Добуток

1000001(2)

б)

Рисунок 2.3 - Приклади виконання арифметичних операцій:

а) додавання; б) множення.

Однак, якщо потрібно використовувати числа зі знаком, застосовують спеціальний додатковий код, що суттєво спрощує апаратні засоби МП пристроїв.

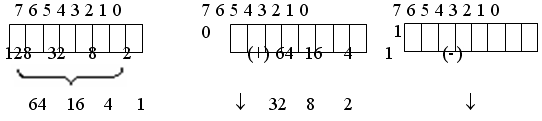

На рисунку 2.4 приведене звичайне зображення регістра МП або комірки пам’яті поза МП.

Рисунок 2.4 - Зображення типового регістра МП чи комірки пам’яті:

а) розташування двійкових позицій; б) представлення додатних чисел нулем у знаковому біті; в) представлення від’ємного числа одиницею в знаковому біті.

Як видно з рисунка, всі від’ємні числа мають 1 в старшому розряді. На прикладі розглянемо основні етапи одержання додаткового коду від’ємного числа (наприклад -9).

|

Десяткове число |

9 |

Етап 1 |

Запис десяткового числа без знака (9) |

|

Двійкове число

|

0000 1001 |

Етап 2 |

Перетворення десяткового числа в двійковий код |

|

Доповнення до 1 (інверсний код)

|

1111 0110 |

Етап 3 |

Одержати інверсний код двійкового числа заміною нулів одиницями, а одиниць - нулями |

|

Доповнення до 2 (інверсний код)

|

1111 0111 |

Етап 4 |

Додати одиницю до інверсного коду |

Одержаний результат є додатковим кодом від’ємного числа -9, оскільки знаковий біт рівний одиниці.

Зворотна процедура одержання десяткового еквівалента числа 11110000, записаного у формі додаткового коду, буде такою:

|

Додатковий код |

11110000 |

Етап 1 |

Запис додатково-го коду |

|

Доповнення до 1 |

00001111 |

Етап 2 |

Одержання інверсного коду |

|

|

+1 |

Етап 3 |

Додати 1 |

|

Двійкове число |

00010000=16(10) |

|

|

Оскільки запис у додатковому коді вказує, що число від’ємне, то остаточно будемо мати: 1111 0000=-16.

МП не виконує прямого віднімання і оперує над додатковими кодами.

Нехай потрібно скласти десяткові числа +7 і -3. Процедура віднімання виконується у такий спосіб:

|

1-число |

+(+7) |

+00000111 |

Додатковий код |

|

2-число |

(-3) |

|

Додатковий код |

|

Результат |

(+4) |

100000100 |

|

Знехтувати переповненням.

Старший біт є переповненням 8-розрядного регістра і ним нехтують. Одержана сума 0000 0100(2) еквівалентна +4(10).

Розглянемо ще один приклад, віднімання від числа 3 числа 8.

|

1-е число |

+(+3) |

+0000 0011 |

|

|

( |

|

|

Результат |

(-5) |

1111 1011(2)=-5(10) |

Операції ділення та множення змішаних двійкових чисел вимагають спеціальних алгоритмів, які тут розглядатись не будуть.

МП може оперувати також з числами, які представлені в BDC-коді, але при цьому процедури є складнішими. Наприклад, сумування чисел, представлених в двійково-десятковому коді 8421, виконується в два етапи. На першому етапі обчислюється попередня сума Sn, причому сумування відбувається за звичайними правилами двійкової арифметики, але з наступними уточненнями:

-якщо в і-тій тетраді Sni попередньої суми утворюється природній перенос, то він враховується в наступній (і+1)-й тетраді;

-якщо в і-тій тетраді Sni природного переносу немає, але Sni10, то рахують, що є штучний перенос, і він знову враховується в (і+1)-й тетраді;

-при Sni<10 переносу немає.

На другому етапі кожна тетрада Sni коректується за таким правилом:

-якщо Sni10, тобто є штучний або природній перенос, то до неї додають число 6;

-утворений при цьому перенос не враховують.

Далі на прикладі природній перенос позначають 1П, штучний - 1Ш.

0,2098 0,0010 00001Ш 10011П 1000

+ +

0,3729 0,0011 0111 0010 1001 .

0,5827 0,0101 1000 1100 0001 Попередня сума

+

0000 0000 0110 0110 корекція

0,0101 1000 0010 0111 сума

+1

+1

11111101

11111101 2-е

число

2-е

число -8)

-8) 1111

1000

1111

1000