- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

Режими адресації

Мікропроцесор ВМ86 дозволяє багато способів доступу до операндів. Операнди можуть знаходитися в регістрах, в самих командах, в пам`яті або в портах вводу-виводу.

ВМ 86 має сім груп режимів адресації:

1.Регістрова адресація.

2.Безпосередня адресація.

3.Пряма адресація.

4.Опосередкована адресація.

5.Адресація по базі.

6.Пряма адресація з індексуванням.

7.Адресація по базі з індексуванням.

В таблиці приведені формати операндів мови асемблера для всіх семи режимів адресації.

Таблиця 4.12- Режими адресації мікропроцесора ВМ 86

|

Режим адресації |

Формат операнда |

Регістр сегмента |

|

1. Регістровий 2. Безпосередній 3. Прямий

4. Опосередкований регістровий

5. По базі

6. Прямий з індексуванням

7. По базі з індексуванням

|

Регістр Дані Зміщення Мітка [BX] [BP] [DI] [SI] [BX] + зміщення [BP] + зміщення [DI] + зміщення [SI] + зміщення [SI]+зміщення [BX][SI]+зміщення [BX] [DI]+зміщення [BP] [ SI]+зміщення [BP] [DI]+зміщення |

Не використовується Не використовується DS DS DS SS DS DS DS SS DS DS DS DS SS SS |

Зауваження:

1. Компонент <зміщення> при адресації по базі з індексуванням є необовязковим.

2. Операнд <регістр> може бути будь-який 8- або 16- бітовий регістр, крім ІР.

3. Операнд <дані> може бути 8- або 16- бітовою константою.

4. Компонент <зміщення> може бути 8- або 16- бітовим зміщенням зі знаком.

5. При роботі зі стрічками регістр DI вказує на сегмент ES.

Розглянемо конкретніше режими адресації.

При регістровій адресації мікропроцесор добуває операнд із регістра (або завантажує його в регістр). Наприклад, команда

MOV AX, CX (CX) AX

копіює 16-бітове слово із регістра лічильника СХ в акумулятор АХ.

При безпосередній адресації, як операнд-джерело вказують 8- або 16- бітові значення констант. Наприклад, команда

MOV CX, 500

завантажує значення 500 в регістр СХ. Діапазон зміни констант: -для 8-бітових чисел від -128(80Н) до 127(7FH);

- для 16- бітових чисел зі знаком від -32768(8000Н) до 32767(7FFFH).

- для 8- та 16-бітових чисел без знака з діапазоном відповідно до 255 (OFF)H i 65535 (OFFFFH).

Для адресації памяті використовують інші пять режимів адресації.

Пряма адресація

При прямій адресації виконавча адреса є складовою частиною команди. Виконавча адреса-це зміщення, яке обчислюється операційним блоком і вказує на якій відстані (в байтах) знаходиться операнд від початку сегмента.

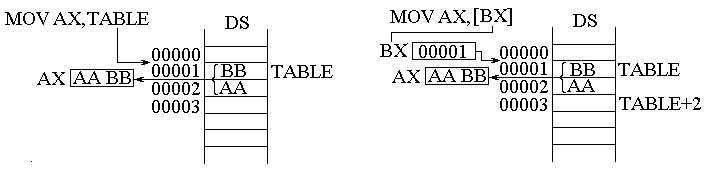

MOV AX, TABLE

завантажує вміст комірки памяті TABLE в регістр АХ (рисунок 4.35).

Рисунок 4.35-Пряма адресація Рисунок 4.36-

Опосередкована ре- гістрова адресація

Опосередкована регістрова адресація

При опосередкованій регістровій адресації виконавча адреса операнда міститься в базовому регістрі ВХ, регістрі покажчику бази ВР або індексному регістрі (SI або DI). Опосередковані регістрові операнди потрібно брати в квадратні дужки. Наприклад команда

МОV AX, [BX]

завантажує вміст комірки памяті, адресованої з ВХ (рисунок 4.36).

Рисунок 4.37- Адресація по базі Рисунок 4.38-Пряма

з індексуванням адресація

Адресація по базі

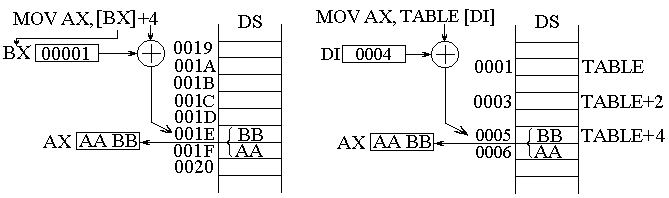

При адресації по базі асемблер вираховує виконавчу адресу сумуванням зміщення з вмістом регістрів ВХ або ВР. Наприклад, команда

MOV AX , [BX] +4

завантажує регістр АХ даними за схемою, приведеною на рисунку 4.36. Асемблер дозволяє вказувати адресований по базі операнд такими способами:

MOV AX, [BP]+4

MOV AX, 4 [BP]

MOV AX, [BP+4].

Ці записи є еквівалентними.

Пряма адресація з індексуванням

При прямій адресації з індексуванням виконавча адреса вираховується як сума зміщення та індексного регістру ( DI або SI).

Наприклад, якщо мітка B_TABLE - є міткою в таблиці слів, то для завантаження в регістр АХ її третього елемента треба виконати таку послідовність команд:

MOV DI, 4

MOV AХ , TABLE [DI].

Алгоритм роботи команди поданий на рисунку 4.37. Таким чином цей тип адресації корисний при роботі з одномірними таблицями.

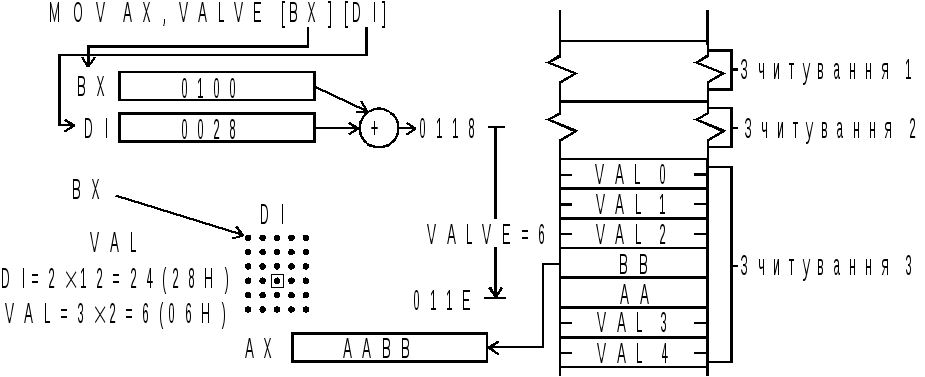

Адресація по базі з індексуванням

При адресації по базі з індексуванням виконавча адреса вираховується як сума значення базового регістра, індексного регістра і, можливо, зміщення. Даний режим адресації є доцільним при адресації двомірних масивів, коли базовий регістр вказує на початкову адресу масиву, а значення зміщення та індексного регістра є відповідно зміщенням по стрічках і стовпчиках.

Наприклад, нехай ЕОМ слідкує за шістьма запобіжними клапанами на хімічному підприємстві. Вона зчитує їх стан кожні півгодини і запамятовує в комірки памяті. За тиждень ці зчитування утворюють масив, який складається з 336 блоків (48 зчитувань на протязі семи днів) по шість елементів в кожному, а всього-2016 значень.

Якщо початкова адреса масиву записана в ВХ, зміщення блоку (номер зчитування, помножений на 12)- в регістрі DI, а номер клапана заданий в змінній VAL, тоді команда

MOV AX, VAL [BX] [DI]

завантажує потрібне значення стану клапана в регістр АХ.

На рисунку 4.38 зображений процес добування результату третього зчитування (номер 2) для клапана 4 із масиву, в якого зміщення в сегменті даних рівне 100Н.

Рисунок 4.38-Добування елемента двовимірного масиву