- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

8.1.1 Мікроконтролер мк 51

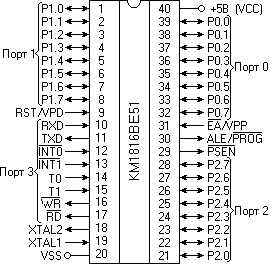

Мікроконтролер (МК) виконаний на базі n-МОП технології, випускається у 40-вивідному корпусі (характерно для аналогу країн СНД). Топологія МК51 подана на рисунку 8.1. МК51 вимагає одного джерела живлення +5В. Через чотири програмованих порти вводу-виводу контролер взаємодіє з периферією. Призначення виводів розшифровані в таблиці 8.4.

Рисунок 8.1 Топологія і найменування виводів

Таблиця 8.4- Призначення виводів МК51

|

Виводи |

Призначення |

|

XTAL2, XTAL1 VCC,VSS

RST/VPD P0.0-P0.7 P1.0-P1.7 P2.0-P2.7 P3.0-P3.7 PSEN ALE/PROG EA/VPP

RST/VPD P2.0-P2.7 P0.0-P0.7

P3.0(RXD) P3.1(TXD) P3.2(INTO) P3.3(INT1) P3.4(TO) P3.5(T1) P3.6(WR)

P3.7(RD)

P1.0-P1.7 P2.0-P2.3 P0.0-P0.7 ALE/PROG EA/VPP |

Однофункціональні виводи Входи підключення зовнішнього резонатора

Входи живлення (+5В,загальний)

Багатофункціональні виводи 1) Основне призначення Початкове встановлення (обнуління)

Двонаправлені порти

Дозвіл читання із зовнішньої пам’яті програм Дозвіл фіксації адреси у зовнішній пам’яті Режим доступу тільки до зовнішньої пам’яті програм (ЕА=0)

Вхід напруги живлення при зменшеному енергопостачанні Старший байт адреси при зверненнях до зовнішньої пам’яті Молодший байт адреси при зверненнях до зовнішньої пам’яті або байт даних, який зчитується із зовнішньої пам’яті чи записується до зовнішньої пам’яті даних Вхід приймача послідовного порту Вихід передавача послідовного порту Вхід зовнішнього переривання 0 Вхід зовнішнього переривання 1 Зовнішній вхід таймера 0 Зовнішній вхід таймера 1 Вихід дозволу запису даних до зовнішніх пристроїв через порт РО під дією команд MOVX@R1,A i MOVX@DPTR,A Вихід дозволу зчитування даних із зовнішніх пристроїв через порт РО під дією команд MOVX A,@R1 i MOVX A,@DPTR

Молодший байт адреси внутрішнього ПЗП Старша тетрада адреси внутрішнього ПЗП Байт даних, який записується до ПЗП Вхід імпульсу програмування ПЗП Вхід напруги програмування +12,75В |

Архітектура МК51

Основу архітектури МК51 (рисунок 8.2) складає внутрішня двонаправлена 8-бітова шина, яка зв’язує між собою всі вузли і пристрої: резидентну пам’ять, АЛП, блок регістрів спеціальних функцій, пристрій керування і порти вводу-виводу. Розглянемо основні елементи архітектури.