- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

Доступ до зовнішньої і резидентної пам’яті

В

МПС на базі МК51 можливе використання

двох типів зовнішньої пам’яті: постійної

пам’яті програм (ЗПП) і оперативної

пам’яті даних (ЗПД). Доступ до ЗПП

здійснюється за допомогою строб-сигналу

читання

![]() .

Доступ до ЗПД можливий через сигнали

.

Доступ до ЗПД можливий через сигнали

![]() i

i

![]() ,

які формуються на лініях Р3.7 і Р3.6 порту

3 в режимі альтернативних функцій.

,

які формуються на лініях Р3.7 і Р3.6 порту

3 в режимі альтернативних функцій.

При зверненні до ЗПП завжди використовується 16-бітова адреса, а до ЗПД-16-бітова адреса (MOVX, @ DPTR) або 8-бітова адреса (MOVX A, @ R1).

Доступ

до ЗПП можливий при наявності двох умов:

або на вхід відключення резидентної

пам’яті програм (![]() )

подається сигнал низького рівня, або

вміст лічильника перевищує значення

0FFFH

(при суміщенні РПП і ЗПП). Наявність

сигналу

)

подається сигнал низького рівня, або

вміст лічильника перевищує значення

0FFFH

(при суміщенні РПП і ЗПП). Наявність

сигналу

![]() забезпечує доступ до молодших 4К адрес

адресного простору ЗПП.

забезпечує доступ до молодших 4К адрес

адресного простору ЗПП.

Часова

діаграма вибирання коду команди з ЗПП

приведена на рисунку 8.6. У фазах S2P1,

S2P2 на

виводах порту Р0 формується молодший

байт комірки зовнішньої пам’яті програм,

де знаходиться код наступної команди.

В цей же момент старший байт адреси

видається через порт Р2. Заднім фронтом

сигналу

![]() (фаза S2P2)

фіксується, а порт РО переходить у

Z-стан.

За переднім фронтом стробу PSEN

(фаза S4P1)

код команди зчитується із ЗПП.

(фаза S2P2)

фіксується, а порт РО переходить у

Z-стан.

За переднім фронтом стробу PSEN

(фаза S4P1)

код команди зчитується із ЗПП.

Таймер - лічильник

МК51 має два програмованих 16-бітних таймери/лічильники (Т/Л0 Т/Л1), які можуть використовуватись як таймери або лічильники зовнішніх подій. При роботі його в режимі таймера вміст Т/Л інкрементується в кожному машинному циклі, тобто через кожні 12 періодів резонатора. При роботі його в режимі лічильника вміст Т/Л інкрементується під дією переходів з 1 в 0 зовнішнього вхідного сигналу на відповідних (Т0 і Т1) виводах МК51. Максимальна частота підрахунку вхідних сигналів рівна 1/24 частоти резонатора.

Для керування роботою Т/Л і організації взаємодії таймерів з системою переривань використовуються два регістри спеціальних функцій (TMOD i TCON), опис яких приведений в таблицях 8.7 – 8.8 відповідно.

Таблиця 8.7- Регістр режиму роботи таймера/лічильника.

|

Символ |

Позиція |

Ім’я та призначення |

||

|

GATE |

TMOD.7 для Т/Л1 і TMOD.3 для Т/Л0 |

Керування блокуванням. Якщо біт установлено, то таймер/ лічильник “х” дозволений до тих пір, доки на вході “INTx” високий рівень і біт керування “TRx” установлено. Якщо біт скинуто, тоді Т/Л дозволений, як тільки біт керування “TRx” установлено. |

||

|

Л/ |

TMOD.6 для Т/Л1 і TMOD.2 для Т/Л0 |

Біт вибору режиму таймера або лічильника подій. Якщо його скинуто, то працює таймер від внутрішнього джерела сигналу синхронізації. Якщо біт установлено, тоді працює лічильник від зовнішніх сигналів на вході “Тх”. |

||

|

М1

М0 |

TMOD.5 для Т/Л1 і TMOD.1 для Т/Л0

TMOD.4 для Т/Л1 і TMOD.0 для Т/Л0 |

М1 |

М0 |

Режими роботи |

|

|

|

0 |

0 |

Таймер-лічильник ”TLx” працює як 5-бітовий дільник. |

|

|

|

0 |

1 |

16-бітовий таймер/лічильник. “THx” і “TLx” включені послідовно. |

|

|

|

1 |

0 |

8-бітовий таймер-лічильник з автоперезавантаження. “THx” зберігає значення, яке перезавантажується в “TLx” після чергового переповнення. |

|

|

|

1 |

1 |

Таймер/лічильник 1 зупиняється. Таймер/ лічильник 0: TLO працює як 8-бітовий таймер/ лічильник, і його режим визначається керуючим бітом таймера 0. ТНО працює як 8-бітовий таймер, і його режим визначається керуючим бітом таймера1. |

Таблиця 8.8- Регістр керування/статуса таймера

|

Символ |

Позиція |

Ім’я та призначення |

|

TF1 |

TCON.7 |

Індикатор переповнення таймера 1. Установлюється апаратно. Скидається апаратно при обслуговуванні переривань. |

|

TR1 |

TCON.6 |

Біт керування таймера 1. Визначається програмно, для його пуску або зупинки. |

|

TF0 |

TCON.5 |

Індикатор переповнення таймера 0. Установлюється апаратно і скидається при обслуговуванні переривань. |

|

TR0 |

TCON.4 |

Біт керування таймера 0. Визначається програмно для пуску або зупинки таймера/лічильника. |

|

IE1 |

TCON.3 |

Індикатор фронту переривання 1. Визначається програмно для специфікації запиту INT1. |

|

IT1 |

TCON.2 |

Біт керування типом переривання 1. Визначається програмно для специфікації запиту INT1 (зріз / низький рівень). |

|

IE0 |

TCON.1 |

Індикатор фронту переривання 0. Установлюється за зрізом сигналу INT0. Скидається при обслуговуванні переривань. |

|

IT0 |

TCON.0 |

Біт керування типом переривання 0. Визначається програмно для специфікації запиту INT0 (зріз / низький рівень). |

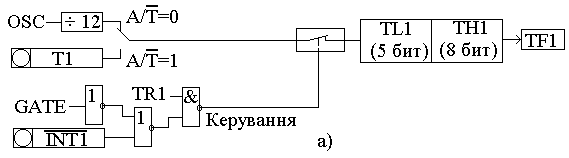

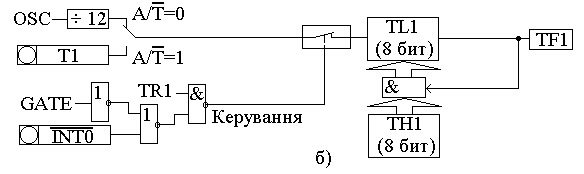

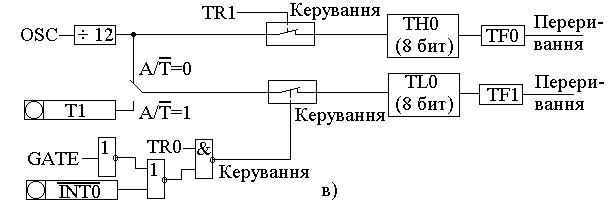

Для розуміння роботи таймерів/лічильників необхідно попередньо проглянути схемотехніку організації режимів роботи таймера/лічильника, показану на рисунку 8.7. Таймери/лічильники можуть працювати в режимах 0,1,2 і 3 (таблиця 8.7). Коротко розглянемо роботу Т/Л в цих режимах.

Рисунок 8.7- Таймер/лічильник подій:

а-Т/Л1 в режимі 0: 13-бітовий лічильник; б-Т/Л1 в режимі 2: 8-бітовий лічильник з перезавантаженням; в-Т/Л0 в режимі 3: два 8- бітових лічильники.

Режим 0. В цьому режимі Т/Л працює як 13-бітовий лічильник/таймер. При переході зі стану “всі одиниці” в стан “всі нулі” установлюється індикатор TF1 (рисунок8.7а). Вхідний сигнал таймера 1 дозволений, якщо TR1=1 і або GATE=0 або INT1=1. Коли GATE=1, таймер можна використовувати для вимірювання тривалості імпульсного сигналу на вході INT1.

Режим1. Робота Т/Л аналогічна режиму 0, але таймерний регістр має розрядність 16 бітів.

Режим 2. В Цьому режимі переповнення 8-бітового лічильника TL1 викликає не тільки установку індикатора TF1, але і автоматично перезавантажує в TL1 вміст старшого байта (ТН1) таймерного регістра, що задається програмно (рисунок 8.7б). Вміст ТН1 не змінюється. Т/Л0 і Т/Л1 працюють однаково.

Режим 3. В даному режимі Т/Л0 і Т/Л1 працюють у такий спосіб. Т/Л1 не змінює свого вмісту, а Т/Л0 (рисунок 8.7в) функціонує, як два незалежний 8-бітових лічильники. Проте ТН0 може працювати тільки як таймер при TR1=1. При цьому ТН0 використовує індикатор переповнення TF1.

Робота ТL0 визначається керуючими бітами Л/T, GATE, TRO, вхідним сигналом INTO та індикатором TF0.

Послідовний інтерфейс

Універсальний асинхронний приймач-передавач (УАПП) забезпечує обмін інформації, поданої у послідовному коді (молодшими бітами вперед), в повному дуплексному режимі обміну. В склад УАПП (послідовний порт) входять приймаючі і передаючі зсуваючі регістри, а також спеціальний буферний регістр (SBUF). Запис байта в буфер приводить до автоматичного перезапису байта в зсуваючий регістр передавача і ініціюється початок передачі байта. Наявність буферного регістра приймача дозволяє суміщати операцію читання раніше прийнятого байта, з прийманням чергового байта.

Послідовний порт може працювати в чотирьох режимах.

Режим 0. В цьому режимі інформація передається і сприймається через зовнішній вивід входу приймача (RXD). Довжина посилки даних складає 8 біт. Через зовнішні виводу виходу передавача (TXD) видаються імпульси зсуву, що супроводжують кожен біт. Частота передачі біта інформації рівна 1/12 частоти резонатора.

Режим 1. В цьому режимі передаються через TXD або приймаються через RXD 10 бітів інформації: старт-біт (0), 8 бітів даних і стоп-біт (1). Швидкість передачі/прийому – величина змінна і задається таймером.

Режим 2. В цьому режимі через TXD передаються або із RXD приймаються 11 бітів інформації: старт-біт, 8 бітів даних програмований 9 біт і стоп-біт. При передачі дев’ятий біт даних може приймати значення 0 або1, або ознаку контролю за парністю (вміст індикатора паритету PSW.0). Частота обміну задається програмно і складає 1/32 або 1/64 частоти резонатора (визначається керуючим бітом SMOD).

Режим 3. Цей режим співпадає з режимом 2, проте частота обміну задається таймером.

Керування режимом роботи УАПП здійснюється через програмування спеціального регістра SCON. Функціональне призначення бітів цього регістра показане в таблиці 8.9.

Прикладна програма визначає режим роботи УАПП шляхом завантаження в старші біти регістра SCON 2-бітового коду. У всіх режимах роботи передача із УАПП ініціюється будь-якою командою, де буферний регістр SBUF є приймачем байта. Приймання інформації в УАПП в режимі 0 можливе за умови, що RI=0 i REN=1. В режимах 1,2,3 прийом починається з переходом старт-біта, якщо REN=1.

Таблиця 8.9- Регістр керування/статуса УАПП

|

Символ |

Позиція |

Ім’я та призначення |

||

|

SM0 SM1 |

SCON.7 SCON.6 |

Біти керування режимом роботи УАПП: |

||

|

|

|

SM0 |

SM1 |

Режими роботи УАПП |

|

|

|

0 |

0 |

Зсувний регістр розширення вводу-виводу |

|

|

|

0 |

1 |

УАПП-8 бітів. Змінна швидкість передачі |

|

|

|

1 |

0 |

УАПП-9 бітів. Фіксована швидкість передачі |

|

|

|

1 |

1 |

УАПП-9 бітів. Змінна швидкість передачі |

|

SM2 |

SCON.5 |

Біт керування режимом УАПП. Установлюється програмно для заборони прийому повідомлень, в яких дев’ятий біт має значення 0 |

||

|

REN |

SCON.4 |

Біт дозволу прийому. Установлюється/скидується програмно для дозволу/заборони прийому послідовних даних |

||

|

TB8 |

SCON.3 |

Передача біта 8. Установлюється/скидається програмно для запису дев’ятого біта в режимі передачі УАПП-9 бітів |

||

|

RB8 |

SCON.2 |

Прийом біта 8. Установлюється/скидається апаратно для фіксації дев’ятого прийнятого біта в режимі УАПП-9 бітів |

||

|

TI |

SCON.1 |

Індикатор переривання передавача. Установлюється апаратно при закінченні передачі байта. Скидається програмно після обслуговування переривання |

||

|

RI |

SCON.0 |

Індикатор переривання передавача. Установлюється апаратно після прийому байта. Скидається програмно після обслуговування переривання |

||

В біті ТВ8 програмно установлюється значення дев’ятого біта даних, який характерний для режиму 2 і 3. В біті RB8 фіксується в режимі 2 і 3 дев’ятий прийнятий біт даних. В режимі 1, якщо SM2=0, в біті RB8 заноситься стоп-біт. В режимі 0 біт RB8 не використовується.

Індикатор переривання передавача ТІ установлюється апаратно в кінці періоду передачі восьмого біта даних в режимі 0 і на початку періоду передачі стоп-біта в режимах 1,2,3. У підпрограмі обслуговування переривань необхідно обнулювати біт ТІ.

Індикатор переривання приймача RI установлюється апаратно в кінці періоду приймання восьмого біта даних в режимі 0 і в середині періоду прийому стоп-біта в режимах 1,2,3. Підпрограма обслуговування переривань має скидати біт RI.

Швидкість

обміну УАПП в різних режимах роботи

визначається різними способами. В режимі

0 частота передачі залежить тільки від

резонансної частоти резонатора

![]() За один машинний цикл послідовний порт

передає один біт інформації.

За один машинний цикл послідовний порт

передає один біт інформації.

В режимах 1,2,3 швидкість обміну залежить від керуючого біта SMOD в регістрі спеціальних функцій (регістр PCON). Призначення регістра PCON показане в таблиці 8.10.

В

режимі 2 частота передачі визначається

виразом

![]() .

Якщо SMOD=0

частота

передачі рівна

.

Якщо SMOD=0

частота

передачі рівна

![]() ,

а при SMOD=1

-

,

а при SMOD=1

-

![]() .

.

Таблиця 8.10- Регістр керування потужністю PCON

|

Символ |

Позиція |

Найменування та функція |

|

SMOD |

PCON.7 |

Подвоєння швидкості обміну |

|

|

PCON.6 |

|

|

- |

PCON.5 |

Не використовуються |

|

- |

PCON.4 |

|

|

GF1 |

PCON.3 |

Індикатори, що визначаються користувачем |

|

GF2 |

PCON.2 |

|

|

PD |

PCON.1 |

Біт зниження споживаної потужності МК |

|

IDL |

PCON.0 |

Біт неробочого ходу. Якщо IDL=1, то наступає режим неробочого ходу |

Зауваження. Обнуління вмісту PCON виконується шляхом завантаження в нього коду ****0000.

В режимах 1 і 3 у формуванні частоти передачі крім керуючого біта SMOD приймає участь таймер 1. При цьому частота передачі залежить від частоти переповнення (OVT1) і визначається у такий спосіб:

![]()

Переривання від таймера 1 в цьому випадку має бути заблоковане. Сам Т/Л1 може працювати і як таймер, і як лічильник подій в будь-якому з трьох режимів. Однак найвдалішим є використання режиму таймера з автозавантаженням (старша тетрада TMOD=0010 B). При цьому частота передачі визначається виразом:

![]()

З особливостями роботи УАПП в різних режимах детально можна ознайомитись у спеціальній літературі [ ].

Система переривань

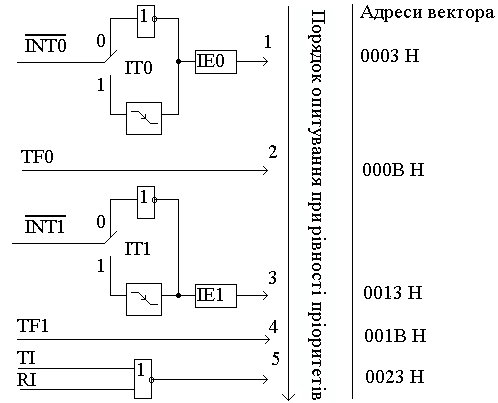

Спрощена схема переривань МК51 подана на рисунку 8.8.

Рисунок 8.8- Схема переривань МК51

Зовнішні

переривання

![]() і

і

![]() можуть викликатись рівнем 0 або переходом

сигналу з 1 в 0 на входах МК в залежності

від значень керуючих бітів ІТ0 і ІТ1 в

регістрі ТCON. Від зовнішніх переривань

установлюється індикатори ІЕ0 і ІЕ1 в

регістрі ТCON, які ініціюють виклик

відповідної програми обслуговування

переривань. Обнуління цих індикаторів

виконується апаратно лише тоді, коли

переривання викликане за зрізом сигналу.

Якщо ж переривання викликане рівнем

вхідного сигналу, то скинути індикатор

ІЕ можна у підпрограмі обслуговування

переривань шляхом впливу на джерело

переривань з метою скасування запиту.

можуть викликатись рівнем 0 або переходом

сигналу з 1 в 0 на входах МК в залежності

від значень керуючих бітів ІТ0 і ІТ1 в

регістрі ТCON. Від зовнішніх переривань

установлюється індикатори ІЕ0 і ІЕ1 в

регістрі ТCON, які ініціюють виклик

відповідної програми обслуговування

переривань. Обнуління цих індикаторів

виконується апаратно лише тоді, коли

переривання викликане за зрізом сигналу.

Якщо ж переривання викликане рівнем

вхідного сигналу, то скинути індикатор

ІЕ можна у підпрограмі обслуговування

переривань шляхом впливу на джерело

переривань з метою скасування запиту.

Індикатори запиту переривань від таймерів TFO i TF1 обнулюється автоматично при передачі керування підпрограмі обслуговування. Індикатори запиту переривання RI i TI установлюються блоком керування УАПП апаратно, але скидувати треба їх програмно.

Переривання можуть ініціюватись і відмінятись програмно, оскільки всі перераховані індикатори програмно-доступні.

В блоці регістрів спеціальних функцій є два регістри для керування режимами переривань і рівнями пріоритету (відповідно символьні імена ІЕ і ІР). Формати цих регістрів описані в таблицях 8.11 – 8.12. Можливість програмної установки бітів цих регістрів забезпечує гнучку систему переривань МК51.

Таблиця 8.11- Регістр масок переривань ІЕ

|

Символ |

Позиція |

Ім’я та призначення |

|

ЕА |

IE.7 |

Заблокування переривань. Скидається програмно для заборони всіх переривань незалежно від стану ІЕ4-ІЕ0 |

|

|

IE.6 |

Не використовується |

|

- |

IE.5 |

|

|

ES |

IE.4 |

Біт дозволу переривання від УАПП. Програмна установка/ скидання програмне для дозволу /заборони переривань від індикаторів TI i RI |

|

ET1 |

IE.3 |

Біт дозволу переривання від таймера 1. Програмна установка/ скидання для дозволу /заборони переривань від таймера 1 |

|

EX1 |

IE.2 |

Біт дозволу зовнішнього переривання 1. Програмна установка/ скидання для дозволу /заборони зовнішнього переривання 1 |

|

ET0 |

IE.1 |

Біт дозволу переривання від таймера 0. Програмна установка/ скидання для дозволу /заборони переривань від таймера 0 |

|

EX0 |

IE.0 |

Біт дозволу зовнішнього переривання 0. Програмна установка/ скидання для дозволу /заборони зовнішнього переривання 0 |

Таблиця 8.12- Регістр пріоритетних переривань

|

Символ |

Позиція |

Ім’я та призначення |

|

- |

IP.7-IP.5 |

Не використовуються |

|

PS |

IP.4 |

Біт пріоритету УАПП. Програмна установка/ скидання для присвоєння перериванню від УАПП вищого/нижчого пріоритету |

|

PT1 |

IP.3 |

Біт пріоритету таймера 1. Програмна установка/ скидання для присвоєння перериванню від таймера 1 вищого/нижчого пріоритету |

|

PX1 |

IP.2 |

Біт

пріоритету зовнішнього переривання

1. Теж для переривання

|

|

PT0 |

IP.1 |

Біт пріоритету таймера 0. |

|

PX0 |

IP.0 |

Біт пріоритету зовнішнього переривання 0. Працює аналогічно ІР.2 |

Індикатори переривань опитуються в момент S5P2 кожного машинного циклу. Ранжування переривань за рівнем пріоритету виконується на наступному машинному циклі. Система переривань генерує апаратний виклик (LCALL) відповідної програми обслуговування, якщо вона не блокується однією з таких умов:

-

в даний момент обслуговується запит переривань рівного або вищого рівня пріоритету;

-

поточний машинний цикл – не останній в циклі виконання команди;

-

виконується команда RETI або інша команда, пов’язана зі зверненням до регістрів ІЕ або ІР.

За апаратно-сформованим кодом LCALL система переривань розміщує в стеку тільки вміст лічильника команд РС і завантажує в нього адресу вектора підпрограми обслуговування. За адресою вектора має бути розміщена команда безумовного переходу (JMP) до початкової адреси підпрограми обслуговування переривань. Підпрограма обслуговування у випадку необхідності має починатись командами запису в стек (PUSH) регістра PSW, акумулятора, покажчика даних тощо і закінчуватись командами відновлення із стеку (РОР). Підпрограма обслуговування переривань має завершуватись командою RETI, за якою у лічильник команд завантажується зі стеку адреса повернення в основну програму.

Cистема команд МК 51

Система базових команд МК 51 містить 111 базових команд,які за функціональною ознакою поділяють на п’ять груп: команди передачі даних, арифметичні операції, логічних операцій, передачі керування і операцій з бітами. Серед цих команд: 50 однобайтових, 45 двобайтові, 16 трибайтові. Більшість команд (64 однобайтових і двобайтових) виконуються за один машинний цикл, 45 команд за 2 машинні цикли, а комнди множення і ділення виконуються за чотири машинні цикли. При тактовій частоті 2 МГц довжина машинного циклу складає 1 мкс. Перелік базових типів команд МК 51 поданий в таблиці 2.11.

Перший байт команди будь-якого типу і формату операції завжди містить код операції (КОП). Другий і третій байти є або адресою операндів або безпосередні операнди. На рисунку 8.9 показані 13 форматів команд МК 51.

-

- -

-