- •Введение

- •Глава 1. Системы элементов эвм

- •§ 1.1 Потенциальная система элементов ттл.

- •§ 1.2 Система элементов мдп (кмдп).

- •§ 1.3 Выходные каскады логических элементов.

- •1. Выход с открытым коллектором

- •2. Открытый эмиттерный выход

- •3. Выход с тремя состояниями

- •§ 1.4 Основные параметры логических элементов.

- •§ 1.5 Соглашения положительной и отрицательной логики.

- •§ 1.6 Особенности базисов современных элементов. Двойственность логических элементов.

- •§ 1.7 Разветвление по входу и выходу.

- •§ 1.8 Гонки.

- •§ 1.9 Гонки по входу.

- •Глава 2. Устройство эвм.

- •§ 2.1 Триггеры.

- •§ 2.2 Классификация триггеров.

- •§ 2.3 Синхронные (статические) rs-триггеры.

- •§ 2.4 D-триггер (dv-триггер).

- •§ 2.5 Класс двухступенчатых триггеров. Jk-триггер.

- •§ 2.6 Дешифраторы, шифраторы.

- •§ 2.7 Преобразователи произвольных кодов.

- •§ 2.8 Мультиплексоры.

- •§ 2.9 Регистры.

- •§ 2.10 Счетчики.

- •§ 2.11 Счетчики с параллельным переносом.

- •§ 2.12 Двоично-кодированные счетчики с произвольным модулем.

- •§ 2.13 Счетчики с недвоичным кодированием.

- •§ 2.14 Полиномиальные счетчики.

- •§ 2.15 Компараторы.

- •Глава 3. Сумматоры

- •§ 3.1 Инкременторы.

- •§ 3.2 Многоразрядные сумматоры с последовательным переносом.

- •§ 3.3 Сумматор с двухколейным переносом.

- •§ 3.4 Сумматоры с параллельным переносом.

- •Глава 4. Алу

- •§ 4.1 Классификация алу. Его назначение.

- •§ 4.2 Языки описания вычитаемых устройств.

- •§ 4.3 Алу для сложения (вычитания) чисел с фиксированной точкой.

- •§ 4.4 Методы умножения двоичных чисел.

- •§ 4.5 Алу для умножения чисел с фиксированной точкой.

- •§ 4.6 Деление целых чисел с фиксированной точкой.

- •§ 4.7 Арифметические операции над десятичными числами (двоично-десятичные сумматоры)

- •§ 4.8 Матричные умножители.

- •§ 4.9 Блок логических операций.

- •§ 4.10 Последовательные умножители.

- •Глава 5. Операции над числами с плавающей точкой.

- •§ 5.1 Сложение и вычитание чисел с плавающей точкой.

- •§ 5.2 Умножение чисел с плавающей точкой.

- •§ 5.3 Деление чисел с плавающей точкой.

- •§ 5.4 Драйверы, шинные приемопередатчики

- •Глава 6. Процессор, его состав

- •§ 6.1 Структурная схема цп

- •§ 6.4 Микропроцессоры

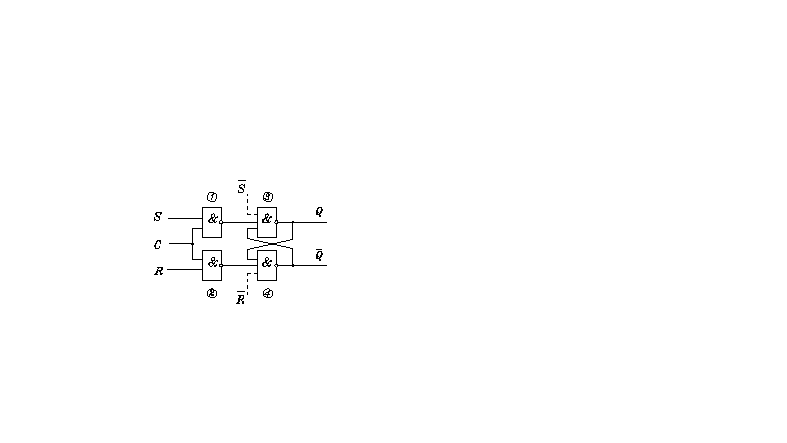

§ 2.3 Синхронные (статические) rs-триггеры.

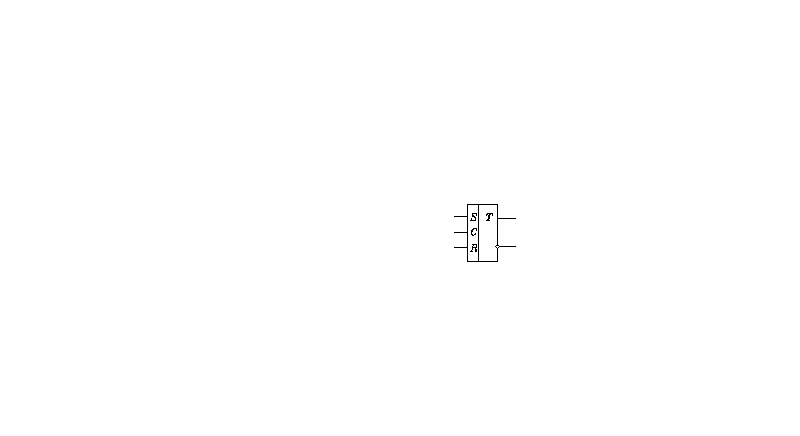

УГО:

На входе RS-триггера ставится коньюнктор на элементах 1 и 2 с управляемыми входами по C, S, R.

При неактивном сигнале C триггер находится в режиме хранения и не реагирует на сигналы по входам S и R. Таким образом, между выходом коньюнктора и входом RS-триггера можно осекать переходные процессы управляющих сигналов. Благодаря этому свойству синхронные RS-триггеры нашли широкое применение.

П римечательное

свойство:

в течение отрезка времени, когда C=1,

сигналы на входах S

и R

и их изменения передаются на выход –

прозрачность

схемы по

входам S и

R.

римечательное

свойство:

в течение отрезка времени, когда C=1,

сигналы на входах S

и R

и их изменения передаются на выход –

прозрачность

схемы по

входам S и

R.

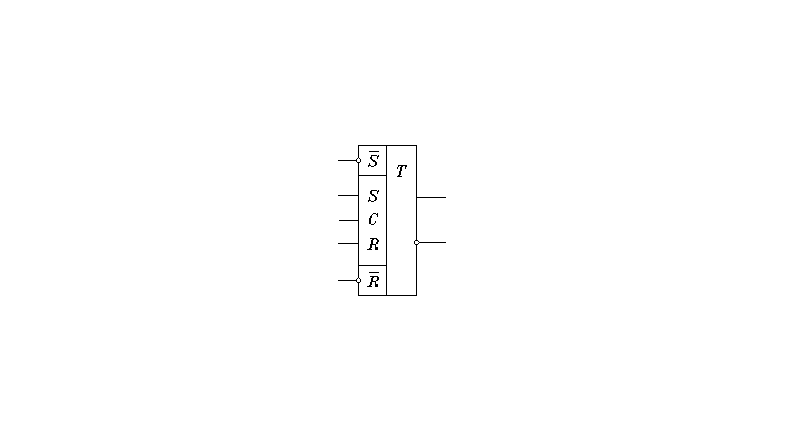

Синхронные

RS-триггеры

могут быть дополнены асинхронными

установочными входами

![]() и

и![]() непосредственно наRS-триггере.

Эти входы приоритетны по отношению к

другим.

непосредственно наRS-триггере.

Эти входы приоритетны по отношению к

другим.

(

—![]() - сигналы низкого уровня)

- сигналы низкого уровня)

Схема синхронного RS-триггера при C=1 функционирует как асинхронный RS-триггер.

§ 2.4 D-триггер (dv-триггер).

D-триггер DV-триггер

D-триггер имеет один информационный вход D, информация с которого записывается только по сигналу C, т.е. D-триггер может быть только синхронным.

C-сигнал играет роль команды «записать».

Из временной диаграммы работы D-триггера видно, что изменение сигнала на D-входе при C=0 не влияют на Q-выход (моменты t1, t2, t7), т.е. триггер запирается по входу С и находится в режиме хранения.

Фронт сигнала C (момент t3) переключает триггер в состояние, соответствующее значению сигнала на входе D. В этом смысле D-триггер задерживает прохождение входного сигнала D до поступления сигнала C. Отсюда и название триггера – «Delay» (задержка)

Другие названия D-триггера: прозрачная защелка, прозрачный фиксатор или синхронный фиксатор.

При C = 1 триггер прозрачен.

По срезу C-сигнала (момент t6) D-триггер фиксирует на выходе Q то значение входного сигнала, которое перед этим моментом было на входе D. Следующее изменение Q будет только по фронту сигнала C (момент t8).

При C=1 постоянном свойства запоминания у D-триггера теряются, и он становится просто усилителем мощности в тракте передач, т.е. полностью прозрачным для входного сигнала.

Способы табличного описания D-триггера:

-

Режимы

Входы

Выходы

C

D

Q

Управление

H(1)

L(0)

L(0)

H(1)

H(1)

H(1)

H(1)

L(0)

Хранение

L

x

q

Иногда в D-триггер вводят дополнительные входы (см. пунктир):

1)

![]() – вход для сброса триггера в ноль приC=0.

При C=1,

если D=1,

RS-триггер

на элементах 3, 4 окажется под воздействием

R

и S

входов, что приведет к неопределенности

выходов.

– вход для сброса триггера в ноль приC=0.

При C=1,

если D=1,

RS-триггер

на элементах 3, 4 окажется под воздействием

R

и S

входов, что приведет к неопределенности

выходов.

2) При наличии V-входа триггер называют DV-триггером, который будет работать также как и D-триггер, но при подаче двух разрешающих сигналов: V и C.

Динамические характеристики D-триггера:

Временная диаграмма построена с учетом состояний неопределенности. Переходной процесс характеризуется значениями задержек распространения по двум трактам:

1) tзд.р.CQ – от входа C до выхода Q при входном сигнале D=const.

2) tзд.р.DQ – от входа D до выхода Q при C=1 – const.

1. Чтобы процесс фиксации состояния D-входа прошел без сбоев, переходной процесс в схеме, вызванный срезом С-сигнала, не должен накладываться на переходный процесс, вызванный переключением D-входа, т.е. необходимы промежутки tпд (время подготовки) и tвд (время выдержки).

Обычно эти времена составляют: tпд=(12), tвд=(01), где - длительность фронтов сигнала.

2. Существует минимально допустимая длительностьC-сигнала, которая обеспечивает отсутствие сбоев из-за наложения переходных процессов переднего и заднего его фронтов. Подобные выводы справедливы для многих цифровых устройств.

Типы серийно-выпускаемых D-триггеров: К155ТМ7, К155ТМ5, К561ТМ3.