- •Введение

- •Глава 1. Системы элементов эвм

- •§ 1.1 Потенциальная система элементов ттл.

- •§ 1.2 Система элементов мдп (кмдп).

- •§ 1.3 Выходные каскады логических элементов.

- •1. Выход с открытым коллектором

- •2. Открытый эмиттерный выход

- •3. Выход с тремя состояниями

- •§ 1.4 Основные параметры логических элементов.

- •§ 1.5 Соглашения положительной и отрицательной логики.

- •§ 1.6 Особенности базисов современных элементов. Двойственность логических элементов.

- •§ 1.7 Разветвление по входу и выходу.

- •§ 1.8 Гонки.

- •§ 1.9 Гонки по входу.

- •Глава 2. Устройство эвм.

- •§ 2.1 Триггеры.

- •§ 2.2 Классификация триггеров.

- •§ 2.3 Синхронные (статические) rs-триггеры.

- •§ 2.4 D-триггер (dv-триггер).

- •§ 2.5 Класс двухступенчатых триггеров. Jk-триггер.

- •§ 2.6 Дешифраторы, шифраторы.

- •§ 2.7 Преобразователи произвольных кодов.

- •§ 2.8 Мультиплексоры.

- •§ 2.9 Регистры.

- •§ 2.10 Счетчики.

- •§ 2.11 Счетчики с параллельным переносом.

- •§ 2.12 Двоично-кодированные счетчики с произвольным модулем.

- •§ 2.13 Счетчики с недвоичным кодированием.

- •§ 2.14 Полиномиальные счетчики.

- •§ 2.15 Компараторы.

- •Глава 3. Сумматоры

- •§ 3.1 Инкременторы.

- •§ 3.2 Многоразрядные сумматоры с последовательным переносом.

- •§ 3.3 Сумматор с двухколейным переносом.

- •§ 3.4 Сумматоры с параллельным переносом.

- •Глава 4. Алу

- •§ 4.1 Классификация алу. Его назначение.

- •§ 4.2 Языки описания вычитаемых устройств.

- •§ 4.3 Алу для сложения (вычитания) чисел с фиксированной точкой.

- •§ 4.4 Методы умножения двоичных чисел.

- •§ 4.5 Алу для умножения чисел с фиксированной точкой.

- •§ 4.6 Деление целых чисел с фиксированной точкой.

- •§ 4.7 Арифметические операции над десятичными числами (двоично-десятичные сумматоры)

- •§ 4.8 Матричные умножители.

- •§ 4.9 Блок логических операций.

- •§ 4.10 Последовательные умножители.

- •Глава 5. Операции над числами с плавающей точкой.

- •§ 5.1 Сложение и вычитание чисел с плавающей точкой.

- •§ 5.2 Умножение чисел с плавающей точкой.

- •§ 5.3 Деление чисел с плавающей точкой.

- •§ 5.4 Драйверы, шинные приемопередатчики

- •Глава 6. Процессор, его состав

- •§ 6.1 Структурная схема цп

- •§ 6.4 Микропроцессоры

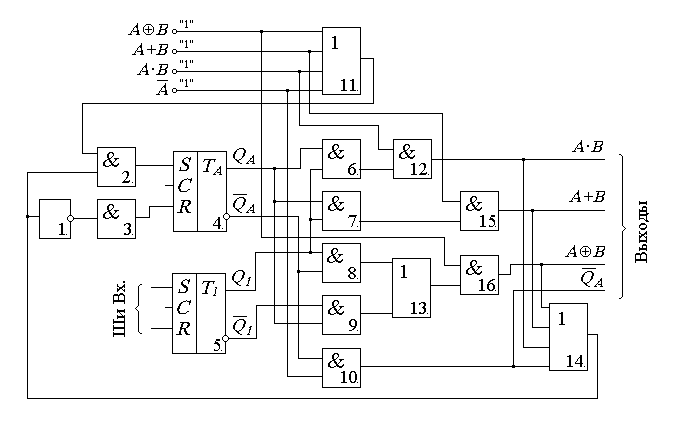

§ 4.9 Блок логических операций.

АЛУ, помимо арифметических операций, выполняет и логические. Приведем структурную схему одного разряда логического блока, входящего в состав АЛУ:

Комментарий: триггер ТА (элемент 4) является триггером (разрядов) регистра сумматора АЛУ (аккумулятора), а триггер Т1 (элемент 5) является триггером регистра А АЛУ (входной регистр). Остальные элементы составляют дополнительный блок в схеме АЛУ.

Представленный блок выполняет операции:

• логического умножения (&)

• сложения (+)

• сложения по mod2 ()

•

инверсия

разряда (![]() )

)

Отличительной особенностью логического блока является то, что все перечисленные операции, которые могут выполняться одновременно и поразрядно, т.е. операции выполняются между разрядами ТА и Т1, которые хранят исходную информацию. Полученный результат операции может быть записан в один из этих триггеров (в нашем случае он записывается в регистр сумматора).

Выбор операции с записью ее результата производится подачей логической единицы на соответствующий управляющий вход (15, 16, 12, 10 – элементы).

Подача такой единицы на два или более входа (выхода) недопустима, т.к. результат должен записываться в один и тот же регистр (элементы 12, 15, 16, 13).

|

Например: |

выходы

триггеров QА

и

|

|

|

выходы

триггеров

|

|

|

выходы элементов 9-го и 8-го – на входы ИЛИ (13). |

В

результате имеем сумму по mod2:

![]() .

.

Подав единицу на элемент & (16) через элемент ИЛИ (14), результат через элемент & (2) запишем в триггер ТА. Другие операции записываются аналогично.

Устройство можно дополнить или расширить узлами, выполняющими другие логические операции, т.е. можно расширять логические возможности АЛУ.

§ 4.10 Последовательные умножители.

В

последовательных умножителях вычисляется

(n+m)

– разрядное произведение:

![]() , гдеAn

= an-1…a0

– множимое, Bm

= bm-1…b0

– множитель.

, гдеAn

= an-1…a0

– множимое, Bm

= bm-1…b0

– множитель.

Множимое записывается параллельно во внутренний регистр памяти умножителя, а разряды множителя подаются на умножитель последовательно, начиная с младшего разряда.

Из традиционного алгоритма умножения чисел известно, что умножитель должен иметь накапливающий сумматор, состоящий из n-разрядного комбинационного двоичного сумматора и сдвигающего регистра, который используется в качестве аккумулятора старших разрядов суммы.

УГО

8-разрядного

последовательного

умножителя:

Прежде чем рассматривать схему умножителя, кратко познакомимся с двумя типами триггера Эрла, которые используются в последовательных умножителях:

1) триггер D – L

D – вход данных (информационный вход)

L – вход сигнала загрузки

при L=1 – режим загрузки

при L=0 – режим хранения

2) триггер D – L/R

R – приоритетный вход

при R=0 триггер работает как D–L триггер

при R=1 триггер сбрасывается в исходное состояние

Схема 8-разрядного последовательного умножителя:

8-разрядный регистр RG1 (регистр памяти) для числа А построен на D-L-триггерах, а 9-разрядный сдвигающий регистр RG2 – на D-L/R-триггерах.

Выход

сумматора – 9-разрядный, с учетом

переноса. Загрузка множимого А

в регистр 1

производится параллельно по сигналу

![]() ,

который одновременно сбрасывает регистрRG2

в ноль.

,

который одновременно сбрасывает регистрRG2

в ноль.

Умножение

числа A

на один разряд

![]() числаВ

(его разряды поступают последовательно,

k

– номер разряда и такта) производится

набором из восьми логических элементов

И.

числаВ

(его разряды поступают последовательно,

k

– номер разряда и такта) производится

набором из восьми логических элементов

И.

![]()

Пока

поступают разряды

![]() множителя,

сдвигающий регистрRG2

работает в режиме синхронной

(параллельной) загрузки (сигнал L=0).

множителя,

сдвигающий регистрRG2

работает в режиме синхронной

(параллельной) загрузки (сигнал L=0).

Эффект сдвига регистра в это время при передаче суммы из RG2 в сумматор SM обеспечивается подачей разрядов RG2 с весом на единицу больше на разряды сумматора, т.е. подаются разряды RG2 Qk+1 (с весом 2k+1) на входы разрядов сумматора bk (с весом 2k).

Умножение выполняется за (m+n) тактов с выдачей произведения Р в последовательном коде с выхода Q0 сдвигающего регистра RG2. Первые m разрядов произведения выдаются при загрузке RG2 за счет эффекта сдвига при вышеупомянутой передаче из RG2 в сумматор, а остальные n разрядов – после подачи сигнала L=1, который переключает RG2 в режим сдвига под действием тактового сигнала С.

Множитель Вm может иметь произвольную разрядность.

Пример серийно-выпускаемых умножителей: К555ИП9.