- •Введение

- •Глава 1. Системы элементов эвм

- •§ 1.1 Потенциальная система элементов ттл.

- •§ 1.2 Система элементов мдп (кмдп).

- •§ 1.3 Выходные каскады логических элементов.

- •1. Выход с открытым коллектором

- •2. Открытый эмиттерный выход

- •3. Выход с тремя состояниями

- •§ 1.4 Основные параметры логических элементов.

- •§ 1.5 Соглашения положительной и отрицательной логики.

- •§ 1.6 Особенности базисов современных элементов. Двойственность логических элементов.

- •§ 1.7 Разветвление по входу и выходу.

- •§ 1.8 Гонки.

- •§ 1.9 Гонки по входу.

- •Глава 2. Устройство эвм.

- •§ 2.1 Триггеры.

- •§ 2.2 Классификация триггеров.

- •§ 2.3 Синхронные (статические) rs-триггеры.

- •§ 2.4 D-триггер (dv-триггер).

- •§ 2.5 Класс двухступенчатых триггеров. Jk-триггер.

- •§ 2.6 Дешифраторы, шифраторы.

- •§ 2.7 Преобразователи произвольных кодов.

- •§ 2.8 Мультиплексоры.

- •§ 2.9 Регистры.

- •§ 2.10 Счетчики.

- •§ 2.11 Счетчики с параллельным переносом.

- •§ 2.12 Двоично-кодированные счетчики с произвольным модулем.

- •§ 2.13 Счетчики с недвоичным кодированием.

- •§ 2.14 Полиномиальные счетчики.

- •§ 2.15 Компараторы.

- •Глава 3. Сумматоры

- •§ 3.1 Инкременторы.

- •§ 3.2 Многоразрядные сумматоры с последовательным переносом.

- •§ 3.3 Сумматор с двухколейным переносом.

- •§ 3.4 Сумматоры с параллельным переносом.

- •Глава 4. Алу

- •§ 4.1 Классификация алу. Его назначение.

- •§ 4.2 Языки описания вычитаемых устройств.

- •§ 4.3 Алу для сложения (вычитания) чисел с фиксированной точкой.

- •§ 4.4 Методы умножения двоичных чисел.

- •§ 4.5 Алу для умножения чисел с фиксированной точкой.

- •§ 4.6 Деление целых чисел с фиксированной точкой.

- •§ 4.7 Арифметические операции над десятичными числами (двоично-десятичные сумматоры)

- •§ 4.8 Матричные умножители.

- •§ 4.9 Блок логических операций.

- •§ 4.10 Последовательные умножители.

- •Глава 5. Операции над числами с плавающей точкой.

- •§ 5.1 Сложение и вычитание чисел с плавающей точкой.

- •§ 5.2 Умножение чисел с плавающей точкой.

- •§ 5.3 Деление чисел с плавающей точкой.

- •§ 5.4 Драйверы, шинные приемопередатчики

- •Глава 6. Процессор, его состав

- •§ 6.1 Структурная схема цп

- •§ 6.4 Микропроцессоры

§ 2.9 Регистры.

Регистром называют группу (линейку) запоминающих элементов (чаще всего, триггеров), предназначенных для записи, хранения, сдвига или выдачи двоичного числа.

Регистр может выполнять следующие операции:

– установка (сброс) в исходное (нулевое)состояние

– запись параллельного кода

– запись последовательного кода

– хранение записанного слова

– сдвиг хранимого кода вправо или влево

– выдача хранимого слова в последовательном или параллельном коде

– поразрядные логические операции

Классификация регистров:

а) По способу приема и выдачи информации:

• параллельные (статические) – запись и считывание происходит в параллельном коде, слова в таких регистрах могут быть подвергнуты поразрядным логическим операциям;

• последовательные (сдвигающие) – запись и считывание происходит в последовательном коде, сдвиг как влево или вправо, так и в обоих направлениях (реверсивный регистр);

• последовательно-параллельные (универсальные) – запись и считывание как в параллельном, так и в последовательном коде;

б) По числу каналов передачи:

• парафазные – информация запоминается и считывается как в прямом, так и в обратном коде;

• однофазные – запись или считывание происходит либо в прямом, либо в обратном коде;

в) По системе синхронизации:

• однотактные;

• двухтактные;

• многотактные.

Типовые внешние связи:

1) информационные входы Di;

2) вход сигнала записи/считывания C;

3) вход сброса R;

4) информационные выходы Qi.

Параллельные регистры:

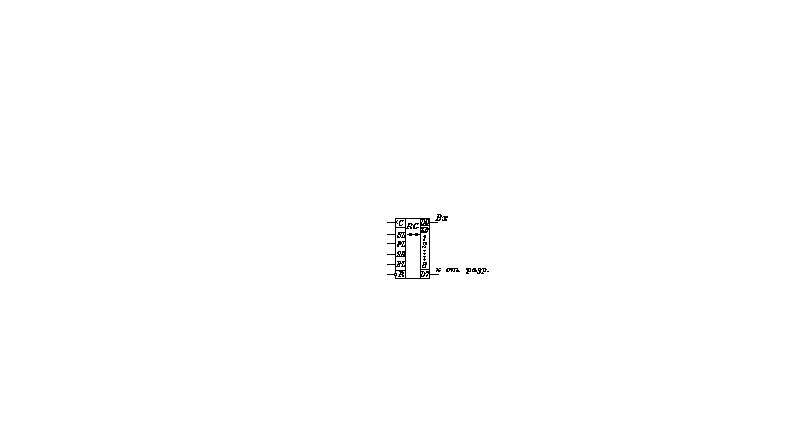

УГО:

Линейка

триггеров T0–T3

управляется сигналами C

и R.

По фронту C-сигнала

записываются данные D0–D3,

причем за один такт, т.е. регистр

однотактный. Сигналом

![]() регистр может быть сброшен в ноль, по

сигналуEZ

происходит считывание информации. Знак

""

означает схему с тремя состояниями

выхода. Наличие этой схемы позволяет

использовать регистр в качестве

буферного, регистра ввода/вывода,

магистрального передатчика и т.д.

регистр может быть сброшен в ноль, по

сигналуEZ

происходит считывание информации. Знак

""

означает схему с тремя состояниями

выхода. Наличие этой схемы позволяет

использовать регистр в качестве

буферного, регистра ввода/вывода,

магистрального передатчика и т.д.

С ерийно-выпускаемый

регистр: К1533ИР38.

ерийно-выпускаемый

регистр: К1533ИР38.

Примечание: на входах и выходах регистров могут быть подключены дополнительные схемы, решающие заданные логические задачи. Эти схемы не меняют сути построения параллельного регистра.

Рассматривается схема одного разряда регистра. На входы подключены элементы, выполняющие роль мультиплексоров, под управлением сигналов C0 и C1 в разряд могут записываться парафазные коды от разных источников.

Без

учета входа

![]() регистр считывает парафазный код. При

наличии пунктирной линии регистр может

записывать прямой код и становится

двухтактным: 1 такт – запись по сигналуC,

2 такт – сброс по сигналу R.

регистр считывает парафазный код. При

наличии пунктирной линии регистр может

записывать прямой код и становится

двухтактным: 1 такт – запись по сигналуC,

2 такт – сброс по сигналу R.

На параллельных регистрах может быть построена регистровая память (КЭШ-память).

КР1533ИР26 – четыре четырехразрядных слова с возможностью независимой и одновременной записи одного слова и считывания другого.

Пример выполнения регистром поразрядной дизъюнкции или конъюнкции:

У правление

передачи изRG1

в RG2

по прямому и инверсному каналу происходит

под управлением сигналов х1,

х2

с помощью вентелей.

правление

передачи изRG1

в RG2

по прямому и инверсному каналу происходит

под управлением сигналов х1,

х2

с помощью вентелей.

Процесс передачи из RG1 в RG2 отражен в таблице:

-

передачи

по Х1

передачи

по Х2

Состояние Т1

Старое состояние Т2

Новое состояние Т2

дизъюнкция

дизъюнкция(ИЛИ)

конъюнкция

(И)

0

0

0

0

1

1

1

0

1

1

1

1

0

0

0

0

1

0

1

0

0

1

1

1

При одновременной передаче по сигналам Х1, Х2 имеем обычную парафазную связь, т.е. данные из RG1 переписываются в RG2 без изменения.

Сдвигающие регистры:

DSR

– Data

Serial Right

DSR

– Data

Serial Right

В однотактной схеме со сдвигом на один разряд вправо сдвиг осуществляется по фронту каждого C-сигнала, содержимое (n-1)го разряда переписывается в (n-2)ой разряд; Q0 поступает на выход.

Очевидно, возможен сдвиг и без записи. Связи между триггерами последовательные.

Регистр со сдвигом влево:

D SL

– Data

Serial Left

SL

– Data

Serial Left

Очевидно, что в сдвигающих регистрах, не имеющих логических элементов в межразрядных связях, нельзя применять одноступенчатые триггеры (например, RS-триггер), управляемые уровнем C-сигнала, поскольку некоторые триггеры в цепочках за время действия C-сигнала могут переключаться.

УГО:

Реверсивные регистры:

У ГО:

ГО:

SL - сигнал сдвига влево

SR - сигнал сдвига вправо

PL - параллельная запись

R - сброс

Di - данные

EZ - сигнал управления тремя состояниями выхода регистра

C - тактовый сигнал

На входах регистров 0, 1, 2, … стоят элементы 3-2И-ИЛИ (выполняют роль мультиплексора), которые управляют режимами работы (параллельная запись, сдвиг влево, сдвиг вправо). При сдвиге влево (от младшего разряда к старшему) подается сигнал SL, нижний конъюнктор открывается, и содержимое младшего разряда регистра переписывается в следующий.

Аналогично происходит сдвиг вправо.

При параллельной записи подаются сигналы PL и EZ. EZ переводит выходную схему в третье состояние, данные Di подаются на входы средних конъюнкторов и записывается в триггеры по тактовому сигналу.

Можно производить запись последовательного кода, при его подаче на вход.

При наращивании разрядов следующая микросхема присоединяется к выходу DZ. Линии управления (входы управления) подсоединяются к общим шинам.

Серийно-выпускаемый регистр: КР1533ИР29.

Широко применяется в микропроцессорных системах.

Для сокращения выводов в подобных микросхемах ставится дешифратор со входами S0 S1, который управляет входами мультиплексора:

|

S0 |

S1 |

|

|

0 |

0 |

хранение |

|

0 |

1 |

сдвиг вправо |

|

1 |

0 |

сдвиг влево |

|

1 |

1 |

параллельная запись |