- •Министерство образования и науки украины

- •Содержание

- •Глава 1 Арифметико-логические основы эвм

- •1.1 Информационные процессы

- •1.2. Обмен информацией между различными информационными устройствами

- •1.3. Аппаратные средства хранения и обработки информации

- •Глава 2 представление числовой информации в цифровом автомате

- •2.1. Системы счисления и понятие кода

- •2.2. Выбор системы счисления

- •2.3. Формальные правила двоичной арифметики

- •2.4. Перевод числа из одной позиционной системы счисления в другую

- •Глава 3 формы представления чисел в цифровых автоматах

- •3.1. Форма представления двоичных чисел с фиксированной запятой

- •3.2. Представление отрицательных чисел в формате с фиксированной запятой

- •3.3. Форма представление чисел с плавающей запятой

- •3.4. Перевод чисел из формата с фиксированной запятой в формат с плавающей запятой и обратно

- •3.5. Погрешности представления чисел

- •20 [A]ф2n- 1 для целых чисел

- •Глава 4. Арифметические действия с двоичными числами

- •4.1. Сложение двоичных чисел

- •4.1.1. Алгебраическое сложение чисел, представленных в форме с фиксированной запятой

- •4.1.2. Переполнение разрядной сетки

- •4.1.3. Модифицированный прямой, обратный и дополнительный код

- •4.1.4. Алгебраическое сложение чисел, представленных в форме с плавающей запятой

- •4.2. Умножение двоичных чисел

- •4.2.1. Методы умножения двоичных чисел

- •4.2.2. Умножение чисел, представленных в форме с фиксированной запятой

- •4.2.3. Умножение чисел, представленных в форме с плавающей запятой

- •4.2.4. Ускорение операции умножения

- •4.3. Деление двоичных чисел

- •4.3.1. Деление двоичных чисел, представленных в форме с фиксированной запятой.

- •4.3.2. Деление двоичных чисел, представленных в форме с плавающей запятой.

- •4.4. Оценка точности выполнения арифметических операций

- •4.4.1. Погрешность округления

- •Глава 5. Выполнение операций над двоично-десятичными числами

- •5.1. Представление десятичных чисел в д-кодах

- •5.2. Формальные правила поразрядного сложения в д-кодах

- •5.3. Представление отрицательных чисел в д-кодах

- •5.4. Выполнение операций сложения и вычитания в д-кодах

- •5.5. Умножение чисел в д-кодах

- •5.6. Деление чисел в д-кодах

- •5.7. Перевод чисел из д-кода в двоичный и из двоичного в д-код

- •Глава 6 Информационные основы цифровых автоматов

- •6.1. Понятие об информации и её преобразованиях

- •6.2. Преобразования алфавитной информации

- •6.3 Понятие об алгоритме

- •6.4 Понятие о дискретном (цифровом) автомате

- •Глава 7 Основы логического проектирования ца. Основные понятия алгебры логики.

- •7.1. Свойства элементарных функций алгебры логики

- •7.2. Аналитическое представление функций алгебры логики

- •7.3. Совершенные нормальные формы

- •7.4. Системы функций алгебры логики

- •7.5. Числовое и геометрическое представление фал

- •Глава 8 Минимизация функций алгебры логики

- •8.1 Метод Квайна

- •Ядро: мднф:

- •8.2 Метод Квайна-Мак-Класки

- •Простые импликанты: *111, 111*, 0**1

- •8.3 Метод Нельсона

- •8.4 Метод диаграмм Вейча

- •8.5 Метод самопонижающихся циклов

- •8.6 Минимизация монотонных функций

- •8.7 Минимизация конъюнктивных нормальных форм

- •8.8 Минимизация частично определенных булевых функций

- •8.9 Минимизация функций в базисах и-не и или-не

- •8.10 Минимизация систем булевых функций

- •Глава 9 Абстрактная теория автоматов

- •9.2 Декомпозиция абстрактных автоматов

- •Глава 10 Структурная теория автоматов

- •10.1 Композиция автоматов

- •Глава 11 Проектирование асинхронных цифровых автоматов

- •11.1 Проектирование комбинационных схем (кс) с учетом кобъед по входу и по выходу

- •11.2 Проектирование кс на дешифраторах и мультиплексорах

- •11.3 Проектирование кс на пзу

- •11.4 Проектирование кс на плм

- •Глава 12 Канонический метод структурного синтеза ца с памятью

- •12.1 Кодирование

- •12.2 Выбор элементов памяти автомата

- •12.3 Выбор структурно-полной системы элементов

- •12.4 Построение уравнений булевых функций возбуждения и выходов автомата

- •12.5 Построение функциональной схемы автомата

- •Глава 13 Обеспечение устойчивости функционирования ца

- •13.2 Проблема синтеза надёжных схем из ненадёжных элементов

- •13.3 Коды Хэмминга

- •Глава 14 Микропрограммные автоматы

- •14.2 Граф-схемы алгоритмов

11.2 Проектирование кс на дешифраторах и мультиплексорах

Дешифратор (DC) – это КС, реализующая все

конституэнты "1" или схема, имеющая

nвходов и![]() выходов, включающая один из выходных

каналов при подаче соответствующего

входного набора.

выходов, включающая один из выходных

каналов при подаче соответствующего

входного набора.

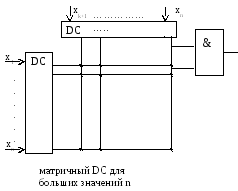

Рассмотри два способа синтеза дешифратора: матричный и прямоугольный.

П ри

синтезе DC используют только элементы

И или ИЛИ-НЕ:

ри

синтезе DC используют только элементы

И или ИЛИ-НЕ:

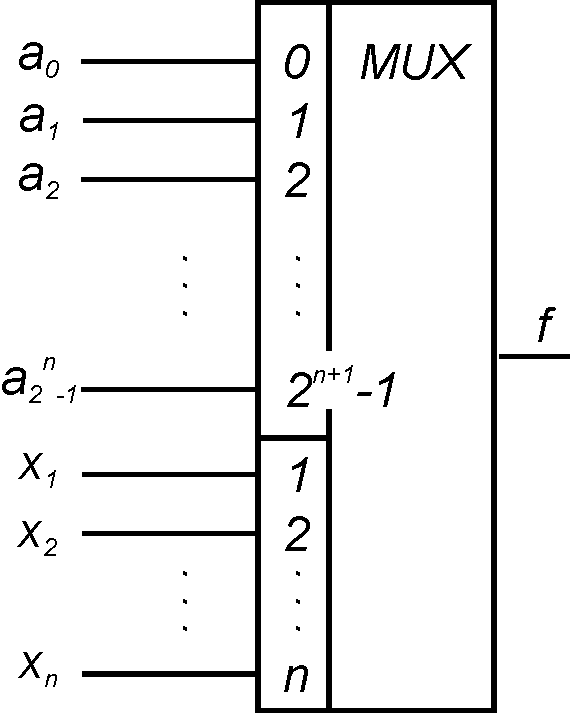

Имея DC можно реализовать произвольную булеву функцию, объединив с помощью схемы ИЛИ те его выходы, которые соответствуют «1» в таблице истинности. Для этой цели можно использовать мультиплексор (MUX).

Под MUX понимают конструктивный элемент с одним выходом и двумя группами входов: адресные входы (входы управления, селекторные) и входы данных. MUX позволяет подачей двоичного набора на адресные входы подключать к выходу требуемый вход данных. Т.е. MUX является коммутатором соответствующего входа данных на свой выход.

|

|

|

|

|

|

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

0 |

|

1 |

0 |

1 |

1 |

|

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

0 |

сли

на входы данных подать двоичный набор,

соответствующий столбцу значений

функцииf, а на адресные входы –

значения переменных, то MUX реализует

функцию заданную таблицей.

сли

на входы данных подать двоичный набор,

соответствующий столбцу значений

функцииf, а на адресные входы –

значения переменных, то MUX реализует

функцию заданную таблицей.

Если MUX имеет n-адресных входов, то

на таком MUX можно реализовать любую

булеву функцию от (n+1) для этого

представим функцию![]() ее таблицей истинности. Переменные

ее таблицей истинности. Переменные![]() выделим как адресные, а переменную

выделим как адресные, а переменную![]() - как переменную данных MUX. Тогда возможны

4 ситуации для любых двух соседних

наборов длины (n+1) с одинаковой

адресной частью:

- как переменную данных MUX. Тогда возможны

4 ситуации для любых двух соседних

наборов длины (n+1) с одинаковой

адресной частью:

1 )

)![]() ;

2)

;

2)![]() ;

3)

;

3)![]() ;

4)

;

4)![]() .

.

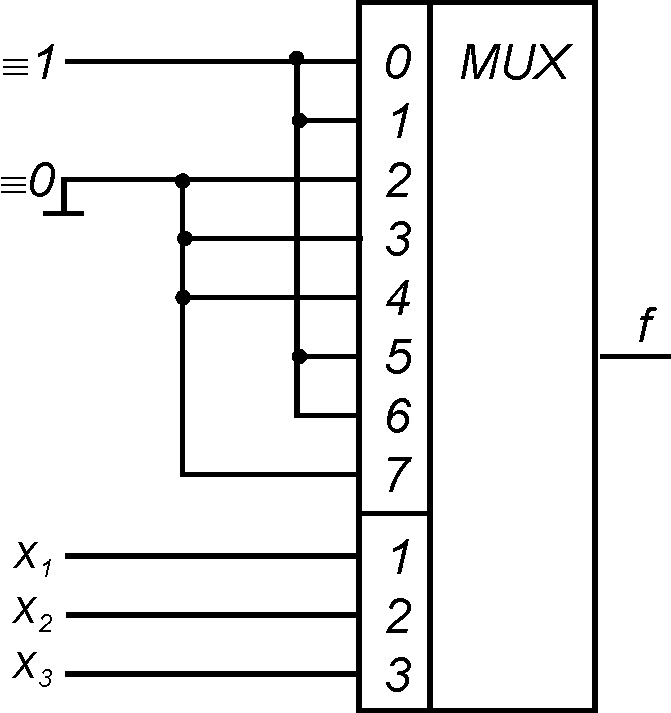

Пример: Для функции от 3х переменных,

приведенной в табличной форме имеем

следующее. Переменные

![]() и

и![]() -

выделим как адресные. Тогда если на

адресные входы поступает набор 1)

-

выделим как адресные. Тогда если на

адресные входы поступает набор 1)![]() ,

то

,

то![]() ;

2)

;

2)![]() ,

то

,

то![]() ;

3)

;

3)![]() ,

то

,

то![]() ;

4)

;

4)![]() ,

то

,

то![]() .

.

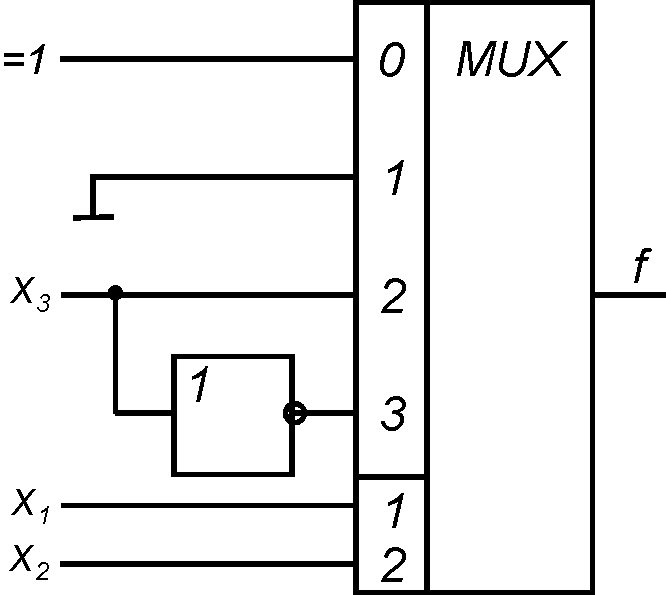

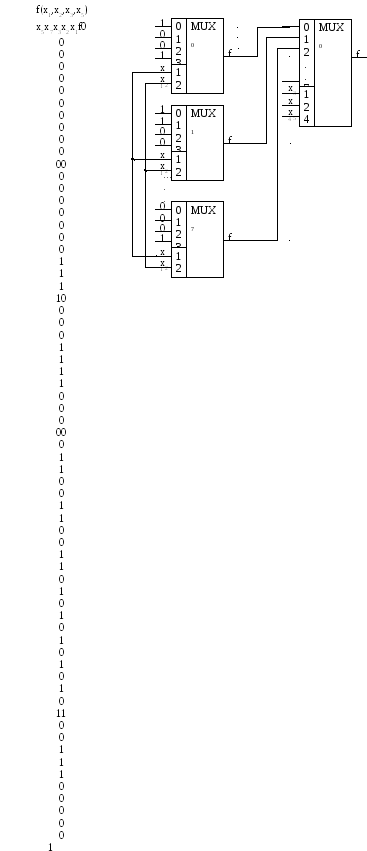

Можно использовать MUX для реализации

булевых функций большого числа переменных.

Для этого производят разложение функции

от nпеременных по переменным![]()

![]()

где

![]() ,

а

,

а

![]() реализуется отдельнымиMUXiи подключается ко входам данных MUX для

переменных

реализуется отдельнымиMUXiи подключается ко входам данных MUX для

переменных

![]() .

Рассмотрим пример реализации функции

от 5 переменных.

.

Рассмотрим пример реализации функции

от 5 переменных.

11.3 Проектирование кс на пзу

(Краткая информация о ПЗУ и ППЗУ.)

Любое ПЗУ имеет nвходов (адресных)

иkвыходов. Если![]() ,

а

,

а![]() ,

то ПЗУ содержит

,

то ПЗУ содержит![]() ячеек памяти, в каждую из которых может

быть записано слово длиной в 2 бита.

ячеек памяти, в каждую из которых может

быть записано слово длиной в 2 бита.

ПЗУ можно использовать не только для хранения информации, но и для ее обработки. Они могут быть использованы для реализации булевых функций, построения устройств управления различного назначения и т.д.

Рассмотрим проектирование КС на ПЗУ.

Пусть есть

![]() булевых

функций от

булевых

функций от![]() переменных, представленных таблицами

истинности. В ячейку памяти с нулевым

адресом некоторого ПЗУ запишем значения

функций из первой строки правой части

таблицы истинности, в ячейку с адресом

переменных, представленных таблицами

истинности. В ячейку памяти с нулевым

адресом некоторого ПЗУ запишем значения

функций из первой строки правой части

таблицы истинности, в ячейку с адресом![]() - значения функций из второй строки

таблицы истинности и т.д. Если теперь

на адресные входы ПЗУ (

- значения функций из второй строки

таблицы истинности и т.д. Если теперь

на адресные входы ПЗУ (![]() ;

;![]() )

подать набор

)

подать набор![]() ,

то на выходах ПЗУ появятся значения

функций на наборе

,

то на выходах ПЗУ появятся значения

функций на наборе![]() .

.

Если

![]() ,

а

,

а

![]() ,

то для реализации системы булевой

функций необходимо разбить её на

подсистемы, каждая из которых содержит

не болееk функций и может быть

реализована на одной схеме ПЗУ. Если

,

то для реализации системы булевой

функций необходимо разбить её на

подсистемы, каждая из которых содержит

не болееk функций и может быть

реализована на одной схеме ПЗУ. Если

![]() ,

то могут быть использованы различные

приёмы декомпозиции булевых функций

по переменным, с реализацией получаемых

подфункций на ПЗУ и последующим

объединением выходов ПЗУ через различные

элементы. Пусть существует система

булевой функций

,

то могут быть использованы различные

приёмы декомпозиции булевых функций

по переменным, с реализацией получаемых

подфункций на ПЗУ и последующим

объединением выходов ПЗУ через различные

элементы. Пусть существует система

булевой функций![]() от 4-х переменных, заданная таблицей

истинности; её реализация на К155ПР6.

от 4-х переменных, заданная таблицей

истинности; её реализация на К155ПР6.

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

1 |

0 |

1 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

1 |

1 |

0 |

|

0 |

1 |

1 |

1 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

0 |

1 |

1 |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

1 |

0 |

0 |

0 |

1 |

|

1 |

0 |

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

0 |

1 |

Более общий способ синтеза КС, реализующий булевы функции с применением ПЗУ и MUX, заключается в следующем.

Производят разложение булевых функций по kпеременных, гдеk- число адресных входов MUX. Оставшиеся2kфункций от (n-k) переменных реализуют, используя ПЗУ, после чего подключают выходы ПЗУ к входам данных MUX в соответствии с формулой разложения заданной функции. При этом дизъюнктивные члены разложения будут иметь вид:

![]() ,

,

где

![]() .

.

Пример:

![]() э

э

Запишем f в виде:

|

|

|

|

|

|

|

|

|

0 |

0 |

|

|

|

1 х |

|

|

1 |

1 |

|

|

|

х 1 |

|

|

0 |

1 |

|

|

|

|

1 1 |

|

0 |

1 |

|

|

|

|

1 х |

|

1 |

0 |

|

|

|

|

х 1 |

|

1 |

0 |

|

|

|

|

1 1 |

Схема реализации функции от пяти переменных.