- •Министерство образования и науки украины

- •Содержание

- •Глава 1 Арифметико-логические основы эвм

- •1.1 Информационные процессы

- •1.2. Обмен информацией между различными информационными устройствами

- •1.3. Аппаратные средства хранения и обработки информации

- •Глава 2 представление числовой информации в цифровом автомате

- •2.1. Системы счисления и понятие кода

- •2.2. Выбор системы счисления

- •2.3. Формальные правила двоичной арифметики

- •2.4. Перевод числа из одной позиционной системы счисления в другую

- •Глава 3 формы представления чисел в цифровых автоматах

- •3.1. Форма представления двоичных чисел с фиксированной запятой

- •3.2. Представление отрицательных чисел в формате с фиксированной запятой

- •3.3. Форма представление чисел с плавающей запятой

- •3.4. Перевод чисел из формата с фиксированной запятой в формат с плавающей запятой и обратно

- •3.5. Погрешности представления чисел

- •20 [A]ф2n- 1 для целых чисел

- •Глава 4. Арифметические действия с двоичными числами

- •4.1. Сложение двоичных чисел

- •4.1.1. Алгебраическое сложение чисел, представленных в форме с фиксированной запятой

- •4.1.2. Переполнение разрядной сетки

- •4.1.3. Модифицированный прямой, обратный и дополнительный код

- •4.1.4. Алгебраическое сложение чисел, представленных в форме с плавающей запятой

- •4.2. Умножение двоичных чисел

- •4.2.1. Методы умножения двоичных чисел

- •4.2.2. Умножение чисел, представленных в форме с фиксированной запятой

- •4.2.3. Умножение чисел, представленных в форме с плавающей запятой

- •4.2.4. Ускорение операции умножения

- •4.3. Деление двоичных чисел

- •4.3.1. Деление двоичных чисел, представленных в форме с фиксированной запятой.

- •4.3.2. Деление двоичных чисел, представленных в форме с плавающей запятой.

- •4.4. Оценка точности выполнения арифметических операций

- •4.4.1. Погрешность округления

- •Глава 5. Выполнение операций над двоично-десятичными числами

- •5.1. Представление десятичных чисел в д-кодах

- •5.2. Формальные правила поразрядного сложения в д-кодах

- •5.3. Представление отрицательных чисел в д-кодах

- •5.4. Выполнение операций сложения и вычитания в д-кодах

- •5.5. Умножение чисел в д-кодах

- •5.6. Деление чисел в д-кодах

- •5.7. Перевод чисел из д-кода в двоичный и из двоичного в д-код

- •Глава 6 Информационные основы цифровых автоматов

- •6.1. Понятие об информации и её преобразованиях

- •6.2. Преобразования алфавитной информации

- •6.3 Понятие об алгоритме

- •6.4 Понятие о дискретном (цифровом) автомате

- •Глава 7 Основы логического проектирования ца. Основные понятия алгебры логики.

- •7.1. Свойства элементарных функций алгебры логики

- •7.2. Аналитическое представление функций алгебры логики

- •7.3. Совершенные нормальные формы

- •7.4. Системы функций алгебры логики

- •7.5. Числовое и геометрическое представление фал

- •Глава 8 Минимизация функций алгебры логики

- •8.1 Метод Квайна

- •Ядро: мднф:

- •8.2 Метод Квайна-Мак-Класки

- •Простые импликанты: *111, 111*, 0**1

- •8.3 Метод Нельсона

- •8.4 Метод диаграмм Вейча

- •8.5 Метод самопонижающихся циклов

- •8.6 Минимизация монотонных функций

- •8.7 Минимизация конъюнктивных нормальных форм

- •8.8 Минимизация частично определенных булевых функций

- •8.9 Минимизация функций в базисах и-не и или-не

- •8.10 Минимизация систем булевых функций

- •Глава 9 Абстрактная теория автоматов

- •9.2 Декомпозиция абстрактных автоматов

- •Глава 10 Структурная теория автоматов

- •10.1 Композиция автоматов

- •Глава 11 Проектирование асинхронных цифровых автоматов

- •11.1 Проектирование комбинационных схем (кс) с учетом кобъед по входу и по выходу

- •11.2 Проектирование кс на дешифраторах и мультиплексорах

- •11.3 Проектирование кс на пзу

- •11.4 Проектирование кс на плм

- •Глава 12 Канонический метод структурного синтеза ца с памятью

- •12.1 Кодирование

- •12.2 Выбор элементов памяти автомата

- •12.3 Выбор структурно-полной системы элементов

- •12.4 Построение уравнений булевых функций возбуждения и выходов автомата

- •12.5 Построение функциональной схемы автомата

- •Глава 13 Обеспечение устойчивости функционирования ца

- •13.2 Проблема синтеза надёжных схем из ненадёжных элементов

- •13.3 Коды Хэмминга

- •Глава 14 Микропрограммные автоматы

- •14.2 Граф-схемы алгоритмов

12.5 Построение функциональной схемы автомата

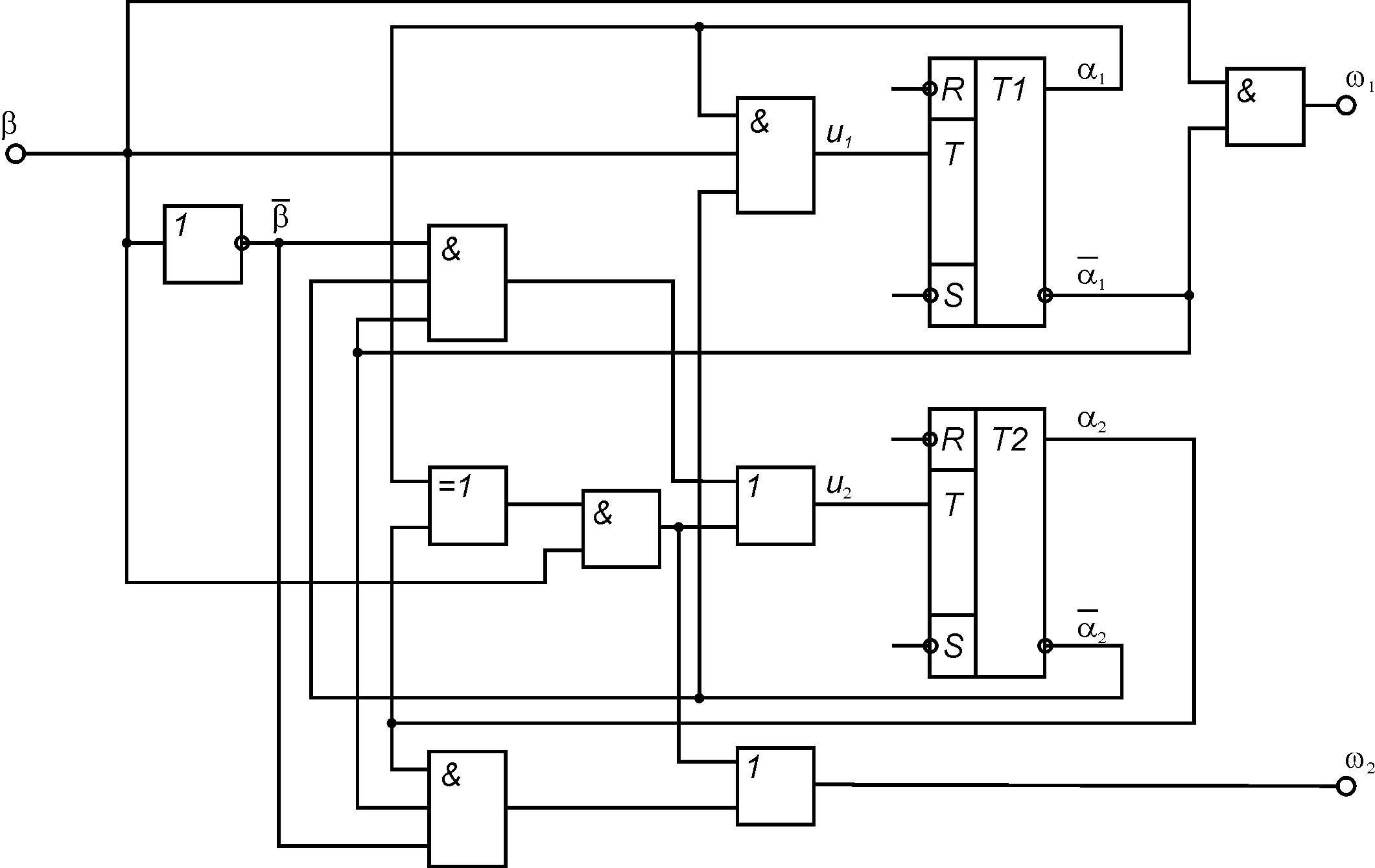

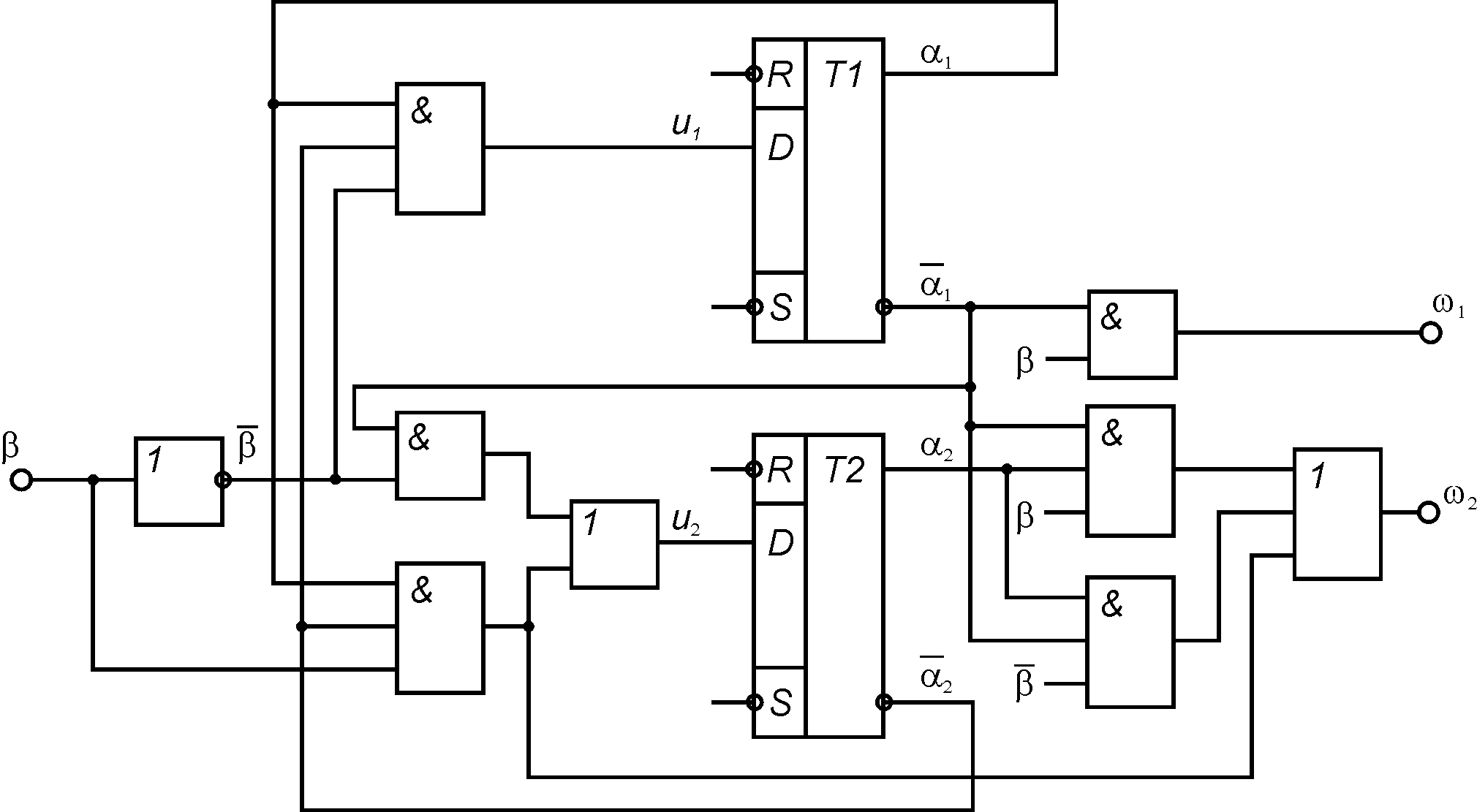

На основании полученных выражений для булевых функций возбуждений элементов памяти автомата и булевых функций выходов автомата строятся КС функций возбуждения и КС формирования выходных сигналов. Элементы памяти подключаются к построенным КС. Функциональная схема автомата Мили при использовании Т-триггера представлена на рис. 1, D-триггера – на рис. 2,RS-триггера – на рис. 3,JK-триггера – на рис.4.

Рис. 12.5.

Рис. 12.6.

Рис. 12.7.

Рис. 12.8.

Глава 13 Обеспечение устойчивости функционирования ца

Обеспечение устойчивости функционирования ЦА с памятью – одна из главных задач этапа структурного синтеза. Под устойчивым функционированием ЦА понимают его функционирование в соответствии с таблицей переходов и выходов. Неустойчивая работа ЦА связана с особенностями физической реализации ЛЭ и элементов памяти его схемы, а так же различными величинами задержек распространения сигнала в элементах и КС.

По характеру физических сигналов, которые используются в ЦА может выделить три основных типа схем: потенциальные, импульсные и импульсно-потенциальные.

Потенциальные схемы может быть построены как на принципе естественного тактирование(асинхронные схемы), так и на принципепринудительного тактирование(синхронные схемы). При естественном тактировании выходы ЗЭ (элементов задержки) через схему обратной связи (составленную из ЛЭ) управляют своими собственными входами. Это создаёт возможность появления в схеме “гонок”. Суть гонок состоит в следующем: ЗЭ (элементы задержки) имеют различные, хотя и близкие времена срабатывания. Если по условиям срабатывания (таблице переходов) ЦА в какой-то момент времени должен изменить свое состояние сразу несколько ЗЭ, то между элементами начинаются гонки. Тот элемент, который выиграет эти гонки, то есть изменит свое состояние раньше, чем другие элементы, может через цепь обратной связи изменить сигналы на входах некоторых ЗЭ до того, как другие участвующие в гонке элементы изменят свое состояние. Это может вызвать переход автомата совсем не в то состояние, которое предусмотрено таблицей переходов автомата.

Проблему гонок может решить за счёт исключения необходимости одновремённогоизменения состоянийсразу у несколькихЗЭ. С этой целью применяютпротивогоночноекодирование состояний ЦА, при котором (двоичные) коды любых двух соседних состояний (состояний переходящих одно в другое под воздействием какого-нибудь входного сигнала) отличаются друг от друга не более чем одним разрядом. Но противогоночное кодирование оказывается возможным далеко не во всех случаях.

Необходимость решения проблемы гонок и проблемы согласования переходов ЦА из одного состояния в другое с изменениями входных сигналов отпадает при введении принудительного тактирования автомата, то есть при превращение автомата всинхронный автомат. Для потенциальных схем принудительное тактирование осуществляется за счёт удвоения числа ЗЭ и введения тактового генератора.

Для асинхронных потенциальных схем, использующих ЗЭ с двумя выходами, существует опасность неправильного срабатывания, связанная с не одновременностью установления сигналов на прямом и на инверсном выходе после перехода ЗЭ из одного состояния в другое. В результате этого в какой-то момент времени может оказаться, что некоторая переменная х и её инверсия принимают одинаковые значения. Проблема устранения источников возникновения подобных ситуаций называется проблемой риска.

Риск неправильного срабатывания имеет место лишь для тех ЗЭ, которые должны сохранять свое состояние в течение рассматриваемого такта. Если это состояние – “1”, то говорят о риске в единице, если – “0”, то о риске в нуле.

Рассмотрим в качестве примера функцию

![]() .

Для этого представления функции

существует риск по переменной х. Функцияfсохраняет значение “1”

при изменении значения х, еслиy=1

иz=1, и сохраняет значение

“0”, когдаy=0,z=0.

При одновременном обращении в “0” х и

.

Для этого представления функции

существует риск по переменной х. Функцияfсохраняет значение “1”

при изменении значения х, еслиy=1

иz=1, и сохраняет значение

“0”, когдаy=0,z=0.

При одновременном обращении в “0” х и![]() выбранное представление функцииfдает нулевое значение при любыхyиz, в том числе и приz=y=1.

Таким образом имеется риск в единице

по переменной х. При других представлениях

функцииf, например

выбранное представление функцииfдает нулевое значение при любыхyиz, в том числе и приz=y=1.

Таким образом имеется риск в единице

по переменной х. При других представлениях

функцииf, например![]() ,

риск по х и по всем другим переменным

отсутствует.

,

риск по х и по всем другим переменным

отсутствует.

Справедливы следующие утверждения.

при представлении булевой функции произвольной ДНФ отсутствует риск в “0”, а при представлении произвольной КНФ отсутствует риск в “1”.

Для

существующих х произвольную ДНФ функции

f

может представить в виде:

![]() ,

где А, В, С – булевые функции не зависящие

от х. Если при каких-то фиксированных

значениях всех переменных, отличных от

х, функцияf=0

как при x=0,

так и при x=1,

то это значит что A=В=С=0. Но тогда f=0

при

,

где А, В, С – булевые функции не зависящие

от х. Если при каких-то фиксированных

значениях всех переменных, отличных от

х, функцияf=0

как при x=0,

так и при x=1,

то это значит что A=В=С=0. Но тогда f=0

при

![]() так и при

так и при![]() .

Таким образом риск в “0” по переменной

х отсутствует. Однако остаётся возможность

риска в “1”.

.

Таким образом риск в “0” по переменной

х отсутствует. Однако остаётся возможность

риска в “1”.

Представления булевой функции в виде СкДНФ и СкКНФ свободны от риска как в “0” так и в “1” по всем переменным. (Доказательство смотреть В.М.Глушков Синтез ЦА стр.356).

Таким образом при синтезе асинхронных потенциальных схем по соображениям надёжности иногда целесообразно отказаться от минимальных форм и пользоваться сокращенными.

Проблемы риска и гонок возникли лишь с появлением потенциальной элементной базы. Используемая ранее импульсно-потенциальная элементная база предусматривала применение статических триггеров со встроенной задержкой. При этом величина задержки была больше длительности импульсного сигнала поступающего на вход триггера. Таким образом переходные процессы формирования сигналов на выходах элементов памяти автомата начинались лишь после окончания входного импульсного сигнала и не оказывали воздействия на входы этих же элементов памяти по цепям обратной связи.