- •Оглавление

- •Предисловие

- •Почему я написал книгу?

- •Для кого эта книга?

- •Как использовать эту книгу?

- •Как организована книга?

- •Об авторе

- •Ошибки и предложения

- •Поддержка книги

- •Как помочь автору

- •Отказ от авторского права

- •Благодарность за участие

- •Перевод

- •Благодарности

- •I Введение

- •1. Введение в ассортимент микроконтроллеров STM32

- •1.1. Введение в процессоры на базе ARM

- •1.1.1. Cortex и процессоры на базе Cortex-M

- •1.1.1.10. Внедренные функции Cortex-M в ассортименте STM32

- •1.2. Введение в микроконтроллеры STM32

- •1.2.1. Преимущества ассортимента STM32….

- •1.2.2. ….И его недостатки

- •1.3. Краткий обзор подсемейств STM32

- •1.3.1. Серия F0

- •1.3.2. Серия F1

- •1.3.3. Серия F2

- •1.3.4. Серия F3

- •1.3.5. Серия F4

- •1.3.6. Серия F7

- •1.3.7. Серия H7

- •1.3.8. Серия L0

- •1.3.9. Серия L1

- •1.3.10. Серия L4

- •1.3.11. Серия L4+

- •1.3.12. Серия STM32WB

- •1.3.13. Как правильно выбрать для себя микроконтроллер?

- •1.4. Отладочная плата Nucleo

- •2. Установка инструментария

- •2.1. Почему выбирают Eclipse/GCC в качестве инструментария для STM32

- •2.1.1. Два слова о Eclipse…

- •2.2. Windows – Установка инструментария

- •2.2.1. Windows – Установка Eclipse

- •2.2.2. Windows – Установка плагинов Eclipse

- •2.2.3. Windows – Установка GCC ARM Embedded

- •2.2.4. Windows – Установка инструментов сборки

- •2.2.5. Windows – Установка OpenOCD

- •2.2.6. Windows – Установка инструментов ST и драйверов

- •2.3. Linux – Установка инструментария

- •2.3.2. Linux – Установка Java

- •2.3.3. Linux – Установка Eclipse

- •2.3.4. Linux – Установка плагинов Eclipse

- •2.3.5. Linux – Установка GCC ARM Embedded

- •2.3.6. Linux – Установка драйверов Nucleo

- •2.3.7. Linux – Установка OpenOCD

- •2.3.8. Linux – Установка инструментов ST

- •2.4. Mac – Установка инструментария

- •2.4.1. Mac – Установка Eclipse

- •2.4.2. Mac – Установка плагинов Eclipse

- •2.4.3. Mac – Установка GCC ARM Embedded

- •2.4.4. Mac – Установка драйверов Nucleo

- •2.4.5. Mac – Установка OpenOCD

- •2.4.6. Mac – Установка инструментов ST

- •3. Hello, Nucleo!

- •3.1. Прикоснитесь к Eclipse IDE

- •3.2. Создание проекта

- •3.3. Подключение Nucleo к ПК

- •3.5. Изучение сгенерированного кода

- •4. Инструмент STM32CubeMX

- •4.1. Введение в инструмент CubeMX

- •4.1.1. Представление Pinout

- •4.1.2. Представление Clock Configuration

- •4.1.3. Представление Configuration

- •4.1.4. Представление Power Consumption Calculator

- •4.2. Генерация проекта

- •4.2.1. Генерация проекта Си при помощи CubeMX

- •4.2.2. Создание проекта Eclipse

- •4.2.3. Ручное импортирование сгенерированных файлов в проект Eclipse

- •4.3. Изучение сгенерированного кода приложения

- •4.3.1. Добавим что-нибудь полезное в микропрограмму

- •4.4. Загрузка исходного кода примеров книги

- •5. Введение в отладку

- •5.1. Начало работы с OpenOCD

- •5.1.1. Запуск OpenOCD

- •5.1.2. Подключение к OpenOCD Telnet Console

- •5.1.3. Настройка Eclipse

- •5.1.4. Отладка в Eclipse

- •5.2. Полухостинг ARM

- •5.2.1. Включение полухостинга в новом проекте

- •5.2.2. Включение полуохостинга в существующем проекте

- •5.2.3. Недостатки полухостинга

- •5.2.4. Как работает полухостинг

- •II Погружение в HAL

- •6. Управление GPIO

- •6.2. Конфигурация GPIO

- •6.2.1. Режимы работы GPIO

- •6.2.2. Режим альтернативной функции GPIO

- •6.2.3. Понятие скорости GPIO

- •6.3. Управление GPIO

- •6.4. Деинициализация GPIO

- •7. Обработка прерываний

- •7.1. Контроллер NVIC

- •7.1.1. Таблица векторов в STM32

- •7.2. Разрешение прерываний

- •7.2.1. Линии запроса внешних прерываний и контроллер NVIC

- •7.2.2. Разрешение прерываний в CubeMX

- •7.3. Жизненный цикл прерываний

- •7.4. Уровни приоритета прерываний

- •7.4.1. Cortex-M0/0+

- •7.4.2. Cortex-M3/4/7

- •7.4.3. Установка уровня прерываний в CubeMX

- •7.5. Реентерабельность прерываний

- •8. Универсальные асинхронные последовательные средства связи

- •8.1. Введение в UART и USART

- •8.2. Инициализация UART

- •8.3. UART-связь в режиме опроса

- •8.3.1. Установка консоли последовательного порта в Windows

- •8.3.2. Установка консоли последовательного порта в Linux и MacOS X

- •8.4. UART-связь в режиме прерываний

- •8.5. Обработка ошибок

- •8.6. Перенаправление ввода-вывода

- •9. Управление DMA

- •9.1. Введение в DMA

- •9.1.1. Необходимость DMA и роль внутренних шин

- •9.1.2. Контроллер DMA

- •9.2. Модуль HAL_DMA

- •9.2.1. DMA_HandleTypeDef в HAL для F0/F1/F3/L0/L1/L4

- •9.2.2. DMA_HandleTypeDef в HAL для F2/F4/F7

- •9.2.3. DMA_HandleTypeDef в HAL для L0/L4

- •9.2.4. Как выполнять передачи в режиме опроса

- •9.2.5. Как выполнять передачи в режиме прерываний

- •9.2.8. Разнообразные функции модулей HAL_DMA и HAL_DMA_Ex

- •9.3. Использование CubeMX для конфигурации запросов к DMA

- •10. Схема тактирования

- •10.1. Распределение тактового сигнала

- •10.1.1. Обзор схемы тактирования STM32

- •10.1.1.1. Многочастотный внутренний RC-генератор в семействах STM32L

- •10.1.3.1. Подача тактового сигнала от высокочастотного генератора

- •10.1.3.2. Подача тактового сигнала от 32кГц генератора

- •10.2. Обзор модуля HAL_RCC

- •10.2.1. Вычисление тактовой частоты во время выполнения

- •10.2.2. Разрешение Выхода синхронизации

- •10.2.3. Разрешение Системы защиты тактирования

- •10.3. Калибровка HSI-генератора

- •11. Таймеры

- •11.1. Введение в таймеры

- •11.1.1. Категории таймеров в микроконтроллере STM32

- •11.1.2. Доступность таймеров в ассортименте STM32

- •11.2. Базовые таймеры

- •11.2.1. Использование таймеров в режиме прерываний

- •11.2.2. Использование таймеров в режиме опроса

- •11.2.3. Использование таймеров в режиме DMA

- •11.2.4. Остановка таймера

- •11.3. Таймеры общего назначения

- •11.3.1.1. Режим внешнего тактирования 2

- •11.3.1.2. Режим внешнего тактирования 1

- •11.3.2. Режимы синхронизации ведущего/ведомого таймеров

- •11.3.2.1. Разрешение прерываний, относящихся к триггерной цепи

- •11.3.2.2. Использование CubeMX для конфигурации синхронизации ведущего/ведомого устройств

- •11.3.3. Программная генерация связанных с таймером событий

- •11.3.4. Режимы отсчета

- •11.3.5. Режим захвата входного сигнала

- •11.3.5.1. Использование CubeMX для конфигурации режима захвата входного сигнала

- •11.3.6. Режим сравнения выходного сигнала

- •11.3.6.1. Использование CubeMX для конфигурации режима сравнения выходного сигнала

- •11.3.7. Генерация широтно-импульсного сигнала

- •11.3.7.1. Генерация синусоидального сигнала при помощи ШИМ

- •11.3.7.2. Использование CubeMX для конфигурации режима ШИМ

- •11.3.8. Одноимпульсный режим

- •11.3.8.1. Использование CubeMX для конфигурации одноимпульсного режима

- •11.3.9. Режим энкодера

- •11.3.9.1. Использование CubeMX для конфигурации режима энкодера

- •11.3.10.1. Режим датчика Холла

- •11.3.10.2. Комбинированный режим трехфазной ШИМ и другие функции управления двигателем

- •11.3.10.3. Вход сброса таймера и блокировка регистров таймера

- •11.3.10.4. Предварительная загрузка регистра автоперезагрузки

- •11.3.11. Отладка и таймеры

- •11.4. Системный таймер SysTick

- •12. Аналого-цифровое преобразование

- •12.1. Введение в АЦП последовательного приближения

- •12.2. Модуль HAL_ADC

- •12.2.1. Режимы преобразования

- •12.2.1.1. Режим однократного преобразования одного канала

- •12.2.1.2. Режим сканирования с однократным преобразованием

- •12.2.1.3. Режим непрерывного преобразования одного канала

- •12.2.1.4. Режим сканирования с непрерывным преобразованием

- •12.2.1.5. Режим преобразования инжектированных каналов

- •12.2.1.6. Парный режим

- •12.2.2. Выбор канала

- •12.2.3. Разрядность АЦП и скорость преобразования

- •12.2.4. Аналого-цифровые преобразования в режиме опроса

- •12.2.6. Аналого-цифровые преобразования в режиме DMA

- •12.2.6.1. Многократное преобразование одного канала в режиме DMA

- •12.2.6.3. Непрерывные преобразования в режиме DMA

- •12.2.7. Обработка ошибок

- •12.2.8. Преобразования, управляемые таймером

- •12.2.9. Преобразования, управляемые внешними событиями

- •12.2.10. Калибровка АЦП

- •12.3. Использование CubeMX для конфигурации АЦП

- •13.1. Введение в периферийное устройство ЦАП

- •13.2. Модуль HAL_DAC

- •13.2.1. Управление ЦАП вручную

- •13.2.2. Управление ЦАП в режиме DMA с использованием таймера

- •13.2.3. Генерация треугольного сигнала

- •13.2.4. Генерация шумового сигнала

- •14.1. Введение в спецификацию I²C

- •14.1.1. Протокол I²C

- •14.1.1.1. START- и STOP-условия

- •14.1.1.2. Формат байта

- •14.1.1.3. Кадр адреса

- •14.1.1.4. Биты «Подтверждено» (ACK) и «Не подтверждено» (NACK)

- •14.1.1.5. Кадры данных

- •14.1.1.6. Комбинированные транзакции

- •14.1.1.7. Удержание синхросигнала

- •14.1.2. Наличие периферийных устройств I²C в микроконтроллерах STM32

- •14.2. Модуль HAL_I2C

- •14.2.1.1. Операции I/O MEM

- •14.2.1.2. Комбинированные транзакции

- •14.3. Использование CubeMX для конфигурации периферийного устройства I²C

- •15.1. Введение в спецификацию SPI

- •15.1.1. Полярность и фаза тактового сигнала

- •15.1.2. Управление сигналом Slave Select

- •15.1.3. Режим TI периферийного устройства SPI

- •15.1.4. Наличие периферийных устройств SPI в микроконтроллерах STM32

- •15.2. Модуль HAL_SPI

- •15.2.1. Обмен сообщениями с использованием периферийного устройства SPI

- •15.2.2. Максимальная частота передачи, достижимая при использовании CubeHAL

- •15.3. Использование CubeMX для конфигурации периферийного устройства SPI

- •16. Циклический контроль избыточности

- •16.1. Введение в расчет CRC

- •16.1.1. Расчет CRC в микроконтроллерах STM32F1/F2/F4/L1

- •16.2. Модуль HAL_CRC

- •17. Независимый и оконный сторожевые таймеры

- •17.1. Независимый сторожевой таймер

- •17.1.1. Использование CubeHAL для программирования таймера IWDG

- •17.2. Системный оконный сторожевой таймер

- •17.2.1. Использование CubeHAL для программирования таймера WWDG

- •17.3. Отслеживание системного сброса, вызванного сторожевым таймером

- •17.4. Заморозка сторожевых таймеров во время сеанса отладки

- •17.5. Выбор сторожевого таймера, подходящего для вашего приложения

- •18. Часы реального времени

- •18.1. Введение в периферийное устройство RTC

- •18.2. Модуль HAL_RTC

- •18.2.1. Установка и получение текущей даты/времени

- •18.2.1.1. Правильный способ чтения значений даты/времени

- •18.2.2. Конфигурирование будильников

- •18.2.3. Блок периодического пробуждения

- •18.2.5. Калибровка RTC

- •18.2.5.1. Грубая калибровка RTC

- •18.2.5.2. Тонкая калибровка RTC

- •18.2.5.3. Обнаружение опорного тактового сигнала

- •18.3. Использование резервной SRAM

- •III Дополнительные темы

- •19. Управление питанием

- •19.1. Управление питанием в микроконтроллерах на базе Cortex-M

- •19.2. Как микроконтроллеры Cortex-M управляют рабочим и спящим режимами

- •19.2.1. Переход в/выход из спящих режимов

- •19.2.1.1. «Спящий режим по выходу»

- •19.3. Управление питанием в микроконтроллерах STM32F

- •19.3.1. Источники питания

- •19.3.2. Режимы питания

- •19.3.2.1. Рабочий режим

- •19.3.2.2. Спящий режим

- •19.3.2.3. Режим останова

- •19.3.2.4. Режим ожидания

- •19.3.2.5. Пример работы в режимах пониженного энергопотребления

- •19.4. Управление питанием в микроконтроллерах STM32L

- •19.4.1. Источники питания

- •19.4.2. Режимы питания

- •19.4.2.1. Рабочие режимы

- •19.4.2.2. Спящие режимы

- •19.4.2.2.1. Режим пакетного сбора данных

- •19.4.2.3. Режимы останова

- •19.4.2.4. Режимы ожидания

- •19.4.2.5. Режим выключенного состояния

- •19.4.3. Переходы между режимами питания

- •19.4.4. Периферийные устройства с пониженным энергопотреблением

- •19.4.4.1. LPUART

- •19.4.4.2. LPTIM

- •19.5. Инспекторы источников питания

- •19.6. Отладка в режимах пониженного энергопотребления

- •19.7. Использование калькулятора энергопотребления CubeMX

- •20. Организация памяти

- •20.1. Модель организации памяти в STM32

- •20.1.1. Основы процессов компиляции и компоновки

- •20.2.1. Исследование бинарного ELF-файла

- •20.2.2. Инициализация секций .data и .bss

- •20.2.2.1. Пара слов о секции COMMON

- •20.2.3. Секция .rodata

- •20.2.4. Области Стека и Кучи

- •20.2.5. Проверка размера Кучи и Стека на этапе компиляции

- •20.2.6. Различия с файлами скриптов инструментария

- •20.3. Как использовать CCM-память

- •20.3.1. Перемещение таблицы векторов в CCM-память

- •20.4.1. Программирование MPU с использованием CubeHAL

- •21. Управление Flash-памятью

- •21.1. Введение во Flash-память STM32

- •21.2. Модуль HAL_FLASH

- •21.2.1. Разблокировка Flash-памяти

- •21.2.2. Стирание Flash-памяти

- •21.2.3. Программирование Flash-памяти

- •21.3. Байты конфигурации

- •21.3.1. Защита от чтения Flash-памяти

- •21.4. Дополнительные памяти OTP и EEPROM

- •21.5. Задержка чтения Flash-памяти и ускоритель ART™ Accelerator

- •21.5.1. Роль TCM-памятей в микроконтроллерах STM32F7

- •22. Процесс начальной загрузки

- •22.1.1. Программное физическое перераспределение памяти

- •22.1.2. Перемещение таблицы векторов

- •22.1.3. Запуск микропрограммы из SRAM с помощью инструментария GNU MCU Eclipse

- •22.2. Встроенный загрузчик

- •22.2.1. Запуск загрузчика из встроенного программного обеспечения

- •22.2.2. Последовательность начальной загрузки в инструментарии GNU MCU Eclipse

- •22.3. Разработка пользовательского загрузчика

- •22.3.2. Как использовать инструмент flasher.py

- •23. Запуск FreeRTOS

- •23.1. Введение в концепции, лежащие в основе ОСРВ

- •23.2.1. Структура файлов с исходным кодом FreeRTOS

- •23.2.1.2. Как импортировать FreeRTOS с использованием CubeMX и CubeMXImporter

- •23.3. Управление потоками

- •23.3.1. Состояния потоков

- •23.3.2. Приоритеты потоков и алгоритмы планирования

- •23.3.3. Добровольное освобождение от управления

- •23.3.4. Холостой поток idle

- •23.4. Выделение памяти и управление ею

- •23.4.1. Модель динамического выделения памяти

- •23.4.1.1. heap_1.c

- •23.4.1.2. heap_2.c

- •23.4.1.3. heap_3.c

- •23.4.1.4. heap_4.c

- •23.4.1.5. heap_5.c

- •23.4.2. Модель статического выделения памяти

- •23.4.3. Пулы памяти

- •23.4.4. Обнаружение переполнения стека

- •23.5. Примитивы синхронизации

- •23.5.1. Очереди сообщений

- •23.5.2. Cемафоры

- •23.5.3. Сигналы потоков

- •23.6. Управление ресурсами и взаимное исключение

- •23.6.1. Мьютексы

- •23.6.2. Критические секции

- •23.6.3. Обработка прерываний совместно с ОСРВ

- •23.7. Программные таймеры

- •23.7.1. Как FreeRTOS управляет таймерами

- •23.8. Пример из практики: Управление энергосбережением с ОСРВ

- •23.8.1. Перехват холостого потока idle

- •23.8.2. Бестиковый режим во FreeRTOS

- •23.9. Возможности отладки

- •23.9.1. Макрос configASSERT()

- •23.9.2. Статистика среды выполнения и информация о состоянии потоков

- •23.10. Альтернативы FreeRTOS

- •23.10.1. ChibiOS

- •23.10.2. ОС Contiki

- •23.10.3. OpenRTOS

- •24. Продвинутые методы отладки

- •24.1. Введение в исключения отказов Cortex-M

- •24.1.1.1. Как инструментарий GNU MCU Eclipse обрабатывает исключения отказов

- •24.1.1.2. Как интерпретировать содержимое регистра LR при переходе в исключение

- •24.1.2. Исключения отказов и их анализ

- •24.2.1. Представление Expressions

- •24.2.1.1. Мониторы памяти

- •24.2.2. Точки наблюдения

- •24.2.3. Режим Instruction Stepping Mode

- •24.2.4. Keil Packs и представление Peripheral Registers

- •24.2.5. Представление Core Registers

- •24.3. Средства отладки от CubeHAL

- •24.4. Внешние отладчики

- •24.4.1. Использование SEGGER J-Link для отладчика ST-LINK

- •24.4.2. Использование интерфейса ITM и трассировка SWV

- •24.5. STM Studio

- •24.6. Одновременная отладка двух плат Nucleo

- •25. Файловая система FAT

- •25.1. Введение в библиотеку FatFs

- •25.1.1. Использование CubeMX для включения в ваши проекты библиотеки FatFs

- •25.1.2. Наиболее важные структуры и функции FatFs

- •25.1.2.1. Монтирование файловой системы

- •25.1.2.2. Открытие файлов

- •25.1.2.3. Чтение и запись файла

- •25.1.2.4. Создание и открытие каталога

- •25.1.3. Как сконфигурировать библиотеку FatFs

- •26. Разработка IoT-приложений

- •26.2. Ethernet контроллер W5500

- •26.2.1. Как использовать шилд W5500 и модуль ioLibrary_Driver

- •26.2.1.1. Конфигурирование интерфейса SPI

- •26.2.1.2. Настройка буферов сокетов и сетевого интерфейса

- •26.2.2. API-интерфейсы сокетов

- •26.2.2.1. Управление сокетами в режиме TCP

- •26.2.2.2. Управление сокетами в режиме UDP

- •26.2.3. Перенаправление ввода-вывода на сокет TCP/IP

- •26.2.4. Настройка HTTP-сервера

- •26.2.4.1. Веб-осциллограф

- •27. Начало работы над новым проектом

- •27.1. Проектирование оборудования

- •27.1.1. Послойная разводка печатной платы

- •27.1.2. Корпус микроконтроллера

- •27.1.3. Развязка выводов питания

- •27.1.4. Тактирование

- •27.1.5. Фильтрация вывода сброса RESET

- •27.1.6. Отладочный порт

- •27.1.7. Режим начальной загрузки

- •27.1.8. Обратите внимание на совместимость с выводами…

- •27.1.9. …и на выбор подходящей периферии

- •27.1.10. Роль CubeMX на этапе проектирования платы

- •27.1.11. Стратегии разводки платы

- •27.2. Разработка программного обеспечения

- •27.2.1. Генерация бинарного образа для производства

- •Приложение

- •Принудительный сброс микроконтроллера из микропрограммы

- •B. Руководство по поиску и устранению неисправностей

- •Проблемы с установкой GNU MCU Eclipse

- •Проблемы, связанные с Eclipse

- •Eclipse не может найти компилятор

- •Eclipse постоянно прерывается при выполнении каждой инструкции во время сеанса отладки

- •Пошаговая отладка очень медленная

- •Микропрограмма работает только в режиме отладки

- •Проблемы, связанные с STM32

- •Микроконтроллер не загружается корректно

- •Невозможно загрузить микропрограмму или отладить микроконтроллер

- •C. Схема выводов Nucleo

- •Nucleo-F446RE

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F411RE

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F410RB

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F401RE

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F334R8

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F303RE

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F302R8

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F103RB

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F091RC

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F072RB

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F070RB

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-F030R8

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-L476RG

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-L152RE

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-L073R8

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •Nucleo-L053R8

- •Разъемы, совместимые с Arduino

- •Morpho-разъемы

- •D. Корпусы STM32

- •LFBGA

- •LQFP

- •TFBGA

- •TSSOP

- •UFQFPN

- •UFBGA

- •VFQFP

- •WLCSP

- •E. Изменения книги

- •Выпуск 0.1 – Октябрь 2015

- •Выпуск 0.2 – 28 октября 2015

- •Выпуск 0.2.1 – 31 октября 2015

- •Выпуск 0.2.2 – 1 ноября 2015

- •Выпуск 0.3 – 12 ноября 2015

- •Выпуск 0.4 – 4 декабря 2015

- •Выпуск 0.5 – 19 декабря 2015

- •Выпуск 0.6 – 18 января 2016

- •Выпуск 0.6.1 – 20 января 2016

- •Выпуск 0.6.2 – 30 января 2016

- •Выпуск 0.7 – 8 февраля 2016

- •Выпуск 0.8 – 18 февраля 2016

- •Выпуск 0.8.1 – 23 февраля 2016

- •Выпуск 0.9 – 27 марта 2016

- •Выпуск 0.9.1 – 28 марта 2016

- •Выпуск 0.10 – 26 апреля 2016

- •Выпуск 0.11 – 27 мая 2016

- •Выпуск 0.11.1 – 3 июня 2016

- •Выпуск 0.11.2 – 24 июня 2016

- •Выпуск 0.12 – 4 июля 2016

- •Выпуск 0.13 – 18 июля 2016

- •Выпуск 0.14 – 12 августа 2016

- •Выпуск 0.15 – 13 сентября 2016

- •Выпуск 0.16 – 3 октября 2016

- •Выпуск 0.17 – 24 октября 2016

- •Выпуск 0.18 – 15 ноября 2016

- •Выпуск 0.19 – 29 ноября 2016

- •Выпуск 0.20 – 28 декабря 2016

- •Выпуск 0.21 – 29 января 2017

- •Выпуск 0.22 – 2 мая 2017

- •Выпуск 0.23 – 20 июля 2017

- •Выпуск 0.24 – 11 декабря 2017

- •Выпуск 0.25 – 3 января 2018

- •Выпуск 0.26 – 7 мая 2018

Введение в ассортимент микроконтроллеров STM32 |

4 |

которых 10 миллиардов было произведено в 2013 году. Процессорами на базе ARM оснащены примерно 75 процентов мобильных устройств в мире. Многие крупносерийные

ипопулярные 64-разрядные и многоядерные процессоры, используемые в устройствах

иставшие иконами в электронной промышленности (например, iPhone от Apple), основаны на архитектуре ARM (ARMv8-A).

Будучи своего рода широко распространенным стандартом, существует множество компиляторов и инструментов, а также операционных систем (Linux является наиболее используемой ОС на процессорах Cortex-A), которые поддерживают данные архитектуры, предлагая разработчикам множество возможностей для создания своих приложений.

1.1.1. Cortex и процессоры на базе Cortex-M

ARM Cortex является обширным набором 32/64-разрядных архитектур и ядер, довольно популярных в мире встраиваемых систем. Микроконтроллеры Cortex делятся на три основных подсемейства:

•Cortex-A, что означает Application – прикладной, представляет собой серию процессоров, предоставляющих широкий спектр решений для устройств, выполняющих сложные вычислительные задачи, такие как хостинг платформы операционной системы (ОС) мобильных устройств (rich OS) (наиболее распространенными являются Linux и его производные Android) и поддержка нескольких программных приложений. Ядрами Cortex-A оснащены процессоры большинства мобильных устройств, таких как смартфоны и планшеты. В данном сегменте рынка мы можем найти несколько производителей интегральных схем: от тех, кто продает каталог компонентов (TI или Freescale) до тех, кто производит процессоры для других лицензиатов. Среди наиболее распространенных ядер в этом сегменте можно выделить 32-разрядные процессоры Cortex-A7 и Cortex-A9, а также новейшие высокопроизводительные 64-разрядные ядра Cortex-A53 и

Cortex-A57.

•Cortex-M, что означает eMbedded – встраиваемый, представляет собой линейку масштабируемых, совместимых, энергоэффективных и простых в использовании процессоров, предназначенных для недорогого встраиваемого рынка. Семейство Cortex-M оптимизировано для чувствительных к стоимости и энергопотреблению микроконтроллеров, подходящих для таких приложений, как Интернет вещей (Internet of Things, IoT), связь, управление двигателем, интеллектуальный учет, устройства взаимодействия с человеком (human interface devices, HID), автомобильные и промышленные системы управления, домашняя бытовая техника, потребительские товары и медицинские инструменты. В данном сегменте рынка мы можем найти многих производителей интегральных схем, которые производят процессоры Cortex-M: ST Microelectronics является одним из них.

•Cortex-R, что означает Real-Time – реального времени, представляет собой серию процессоров, предлагающих высокопроизводительные вычислительные решения для встраиваемых систем, где необходимы надежность, высокая доступность, отказоустойчивость, ремонтопригодность и детерминированный отклик в реальном времени. Процессоры серии Cortex-R обеспечивают быструю и детерминированную обработку и высокую производительность при одновременном решении сложных задач в режиме реального времени. Они объединяют эти функции

Введение в ассортимент микроконтроллеров STM32 |

5 |

в корпусе, оптимизированном по производительности, энергопотреблению и занимаемой площади, что делает их верным выбором в надежных системах, требовательных к отказоустойчивости.

В следующих параграфах будут представлены основные возможности процессоров Cortex-M, особенно с точки зрения встраиваемого разработчика.

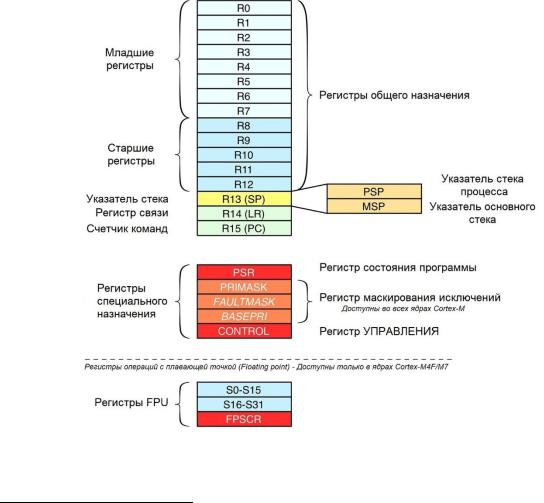

1.1.1.1.Регистры ядра

Как и все архитектуры RISC, процессоры Cortex-M являются машинами загрузки/хранения, которые выполняют операции только с регистрами ЦПУ, за исключением2 двух инструкций: load и store, используемых для передачи данных между регистрами ЦПУ и ячейками памяти.

На рисунке 2 показаны основные регистры Cortex-M. Некоторые из них доступны только в высокопроизводительных сериях, таких как M3, M4 и M7. R0-R12 являются регистрами общего назначения и могут использоваться в качестве операндов для инструкций ARM. Однако некоторые регистры общего назначения могут использоваться компилятором в качестве регистров со специальными функциями. R13 – регистр указателя стека (Stack Pointer, SP), который также считается банковым. Это означает, что содержимое регистра изменяется в соответствии с текущим режимом ЦПУ (привилегированным или непривилегированным). Данная функция обычно используется операционными системами реального времени (ОСРВ) для переключения контекста.

Рисунок 2: Регистры ядра ARM Cortex-M

2 Это не совсем верно, поскольку в архитектуре ARMv6/7 доступны другие инструкции, обращающиеся к ячейкам памяти, но для целей данного обсуждения лучше всего считать это предположение верным.

Введение в ассортимент микроконтроллеров STM32 |

6 |

Например, рассмотрим следующий код Cи с использованием локальных переменных

“a”, “b”, “c”:

...

uint8_t a,b,c;

a = 3; b = 2;

c = a * b;

...

Компилятор сгенерирует следующий ассемблерный код ARM3:

1 |

movs |

r3, #3 |

;поместить "3" в регистр |

r3 |

||

2 |

strb |

r3, [r7, #7] |

;сохранить содержимое |

r3 |

в "a" |

|

3 |

movs |

r3, #2 |

;поместить "2" в регистр |

r3 |

||

4 |

strb |

r3, [r7, #6] |

;сохранить содержимое |

r3 |

в "b" |

|

5 |

ldrbr |

r2, [r7, #7] |

;загрузить содержимое |

"a" |

в r2 |

|

6 |

ldrb |

r3, [r7, #6] |

;загрузить содержимое |

"b" |

в r3 |

|

7 |

smulbb |

r3, r2, r3 |

;перемножить "a" на "b" и |

сохранить результат в r3 |

||

8 |

strb |

r3, [r7, #5] |

;сохранить результат в "c" |

|

||

Как мы видим, все операции всегда выполняются с регистром. Команды в строках 1-2 перемещают число 3 в регистр r3 и затем сохраняют его содержимое (то есть число 3) в ячейке памяти, заданной регистром r7 (который является указателем стекового кадра (frame pointer), как мы увидим в Главе 20) плюс смещение в 7 ячеек памяти – это ячейка, в которой хранится переменная. То же самое происходит для переменной b в строках 3-4. Затем строки 5-7 загружают содержимое переменных a и b и выполняют умножение. Наконец, строка 8 сохраняет результат в ячейке памяти переменной c.

1.1.1.2.Карта памяти

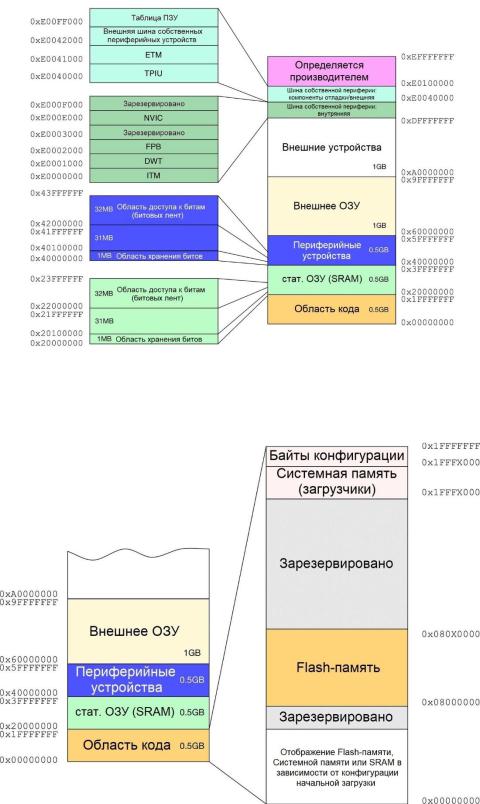

ARM определяет стандартизированное адресное пространство памяти, общее для всех ядер Cortex-M, что обеспечивает переносимость кода между различными производителями интегральных схем. Адресное пространство размером 4 ГБ и состоит из нескольких секций с различными логическими функциями. На рисунке 3 показана карта памяти (или схема распределения памяти) процессора Cortex-M4.

3 Этот ассемблерный код был скомпилирован в режиме thumb с отключенной оптимизацией, вызывая GCC следующим образом:

$ arm-none-eabi-gcc -mcpu=cortex-m4 -mthumb -fverbose-asm -save-temps -O0 -g -c file.c

4 Хотя организация памяти и размер секций (а, следовательно, и их адресов) стандартизированы для всех ядер Cortex-M, некоторые функции могут отличаться. Например, Cortex-M7 не предоставляет области доступа к битам (битовых лент), а некоторые периферийные устройства в области Шины собственных периферийных устройств (Private Peripheral Bus, PPB) различаются. Всегда обращайтесь к справочному руководству по архитектуре, которую вы рассматриваете.

Введение в ассортимент микроконтроллеров STM32 |

7 |

Рисунок 3: Фиксированное адресное пространство памяти Cortex-M

Первые 512 МБ выделены для области кода. Устройства STM32 дополнительно делят эту область на несколько секций, как показано на рисунке 4. Давайте кратко рассмотрим их.

Рисунок 4: Карта памяти области кода на микроконтроллерах STM32

Введение в ассортимент микроконтроллеров STM32 |

8 |

Все процессоры Cortex-M отображают область кода, начиная с адреса 0x0000 00005. Данная область также включает указатель на начало стека (обычно помещается в SRAM) и таблицу векторов, как мы увидим в Главе 7. Расположение области кода стандартизировано среди всех других производителей Cortex-M, несмотря на то что архитектура ядра достаточно гибкая, чтобы позволить им организовать данную область по-другому. Фактически, для всех устройств STM32 область, начинающаяся с адреса 0x0800 0000, связана с внутренней Flash-памятью микроконтроллера и является областью, в которой находится программный код. Тем не менее, благодаря определенной конфигурации начальной загрузки, которую мы рассмотрим в Главе 22, данная область также отражается (aliased) на адрес 0x0000 0000. Это означает, что вполне возможно ссылаться на содержимое Flashпамяти, начиная с адреса 0x0800 0000 и 0x0000 0000 (например, процедура, расположенная по адресу 0x0800 16DC, также доступна из 0x0000 16DC).

Последние две секции выделены под Системную память и Байты конфигурации (Option bytes). Первая – это область ПЗУ, зарезервированная для загрузчиков. Каждое семейство STM32 (и их подсемейства – low density, medium density и т. д.) предоставляет загрузчик, предварительно запрограммированный в микросхему во время производства. Как мы увидим в Главе 22, данный загрузчик можно использовать для загрузки кода с нескольких периферийных устройств, включая USART, USB и CAN-шину. Область Байтов конфигурации содержит последовательность битовых флагов, которые могут использоваться для конфигурации некоторых аспектов микроконтроллера (таких как защита от чтения Flash-памяти, аппаратный сторожевой таймер, режим начальной загрузки и т. д.) и связаны с конкретным микроконтроллером STM32.

Возвращаясь ко всему 4 ГБ адресному пространству, следующая основная область – это область, ограниченная внутренним статическим ОЗУ (SRAM) микроконтроллера. Она начинается с адреса 0x2000 0000 и потенциально может расширяться до 0x3FFF FFFF. Однако фактический конечный адрес зависит от действующего количества внутреннего SRAM. Например, в случае микроконтроллера STM32F103RB с 20 КБ SRAM конечный адрес 0x2000 4FFF6. Попытка получить доступ к ячейке за пределами данной области вызовет исключение отказа шины Bus Fault (подробнее о нем позже).

Следующие 0,5 ГБ памяти предназначены для отображения периферийных устройств. Каждое периферийное устройство, предоставляемое микроконтроллером (таймеры, интерфейсы I²C и SPI, USART и т. д.), имеет отображение в данной области. Организация данного пространства памяти зависит от конкретного микроконтроллера.

1.1.1.3.Технология битовых лент (bit-banding)

Во встроенных приложениях достаточно часто необходимо работать с отдельными битами слова, используя битовое маскирование. Например, предположим, что мы хотим установить или сбросить 3-й бит (бит 2) беззнакового байта. Мы можем сделать это, просто воспользовавшись следующим кодом Си:

5Чтобы улучшить читабельность, все 32-битные адреса в данной книге написаны так, что старшие два байта отделены от младших. Таким образом, всякий раз, когда вы видите адрес, записанный таким образом (0x0000 0000), вы должны интерпретировать его как один общий 32-битный адрес (0x00000000). Данное правило не распространяется на исходные коды языков Си и ассемблера.

6Конечный адрес вычисляется следующим образом: 20 КБ = 20 * 1024 Байт, которые в шестнадцатеричной системе счисления равны 0x5000. Но адреса начинаются с 0, следовательно, конечный адрес 0x2000 0000 +

0x4FFF.

Введение в ассортимент микроконтроллеров STM32 |

9 |

...

uint8_t temp = 0;

temp |= 0x4; temp &= ~0x4;

...

Битовое маскирование используется, когда мы хотим сэкономить место в памяти (используя одну переменную и назначая различное значение для каждого из ее битов) или когда нам приходится иметь дело с внутренними регистрами микроконтроллера и периферийными устройствами. Разбирая предыдущий код Си, мы увидим, что компилятор сгенерирует следующий ассемблерный код ARM7:

#temp |= 0x4; |

|

|

|

|

a: |

79fb |

|

ldrb |

r3, [r7, #7] |

c: |

f043 |

0304 |

orr.w |

r3, r3, #4 |

10: |

71fb |

|

strb |

r3, [r7, #7] |

#temp &= ~0x4; |

|

|

|

|

12: |

79fb |

|

ldrb |

r3, [r7, #7] |

14: |

f023 |

0304 |

bic.w |

r3, r3, #4 |

18: |

71fb |

|

strb |

r3, [r7, #7] |

Как мы видим, такая простая операция требует трех ассемблерных инструкций (fetch, modify, save – выборка, изменение, сохранение). Это приводит к двум типам проблем. Во-первых, это пустая трата тактовых циклов процессора, использующихся на выполнение этих трех инструкций. Во-вторых, данный код работает нормально, если процессор работает в режиме одной задачи, и у нас есть только один поток выполнения, но, если мы имеем дело с одновременным выполнением, другая задача (или просто процедура прерывания) может повлиять на содержимое памяти перед завершением операции «битовое маскирование» (например, если между командами в строках 0xC-0x10 или 0x14- 0x18 в вышеприведенном ассемблерном коде происходит прерывание).

Битовые ленты – это способность отображать каждый бит определенной области памяти на целое слово в участке памяти области доступа к битам (битовых лент), англ. alias bit-banding region, обеспечивая атомарный доступ к такому биту. На рисунке 5 показано, как процессор Cortex отражает содержимое адреса памяти 0x2000 0000 с областью доступа к битам (битовых лент) 0x2200 0000-1c. Например, если мы хотим изменить бит 2 ячейки памяти 0x2000 0000, мы можем просто получить доступ к ячейке памяти

0x2200 0008.

Формула для вычисления адресов областей доступа к битам (битовых лент):

bit_band_address = alias_region_base + (region_base_offset x 32) + (bit_number x 4)

где:

alias_region_base – базовый адрес области доступа к битам; region_base_offset – смещение области доступа к битам;

bit_number – номер бита.

7 Этот ассемблерный код был скомпилирован в режиме tumb с отключенной оптимизацией, вызывая GCC следующим образом:

$ arm-none-eabi-gcc -mcpu=cortex-m4 -mthumb -fverbose-asm -save-temps -O0 -g -c file.c

Введение в ассортимент микроконтроллеров STM32 |

10 |

Рисунок 5: Отображение памяти адреса SRAM 0x2000 0000 в области битовых лент (показаны первые 8 из 32 битов)

Например, учитывая адрес памяти на рисунке 5, для доступа к биту 2:

alias_region_base = 0x22000000 region_base_offset = 0x20000000 - 0x20000000 = 0

bit_band_address = 0x22000000 + 0 × 32 + (0x2 × 0x4) = 0x22000008

ARM определяет две области хранения битов для микроконтроллеров на базе Cortex-M8, каждая из которых размером 1 МБ и отображается в 32-Мбитной области доступа к битам. Каждое последовательное 32-битное слово в области доступа к битам (bit-band alias) относится к каждому последовательному биту в области хранения бит (bit-band region) (что объясняет данное соотношение размеров: 1 Мбит <-> 32 Мбит). Первая область хранения бит начинается с 0x2000 0000 и заканчивается в 0x200F FFFF, а область доступа к битам с отраженными битами начинается от 0x2200 0000 до 0x23FF FFFF. Область доступа к битам предназначена для битового доступа к ячейкам памяти SRAM.

Рисунок 6: Карта памяти и области доступа к битам (битовых лент)

Другая область хранения битов начинается с 0x4000 0000 и заканчивается 0x400F FFFF, как показано на рисунке 6. Эта область посвящена отображению памяти периферийных

8 К сожалению, микроконтроллеры на базе Cortex-M7 не предоставляют возможности битовых лент.

Введение в ассортимент микроконтроллеров STM32 |

11 |

устройств. Например, ST отображает регистр GPIO выходных данных (Output Data Register, ODR) (GPIO->ODR) периферийного устройства GPIOA с 0x4002 0014. Это означает, что каждый бит слова, расположенного по адресу 0x4002 0014, позволяет изменять состояние вывода GPIO (с НИЗКОГО на ВЫСОКОЕ, и наоборот). Поэтому, если мы хотим изменить состояние вывода PIN5 порта GPIOA9, используя предыдущую формулу, то получим:

alias_region_base = 0x42000000

region_base_offset = 0x40020014 - 0x40000000 = 0x20014

bit_band_address = 0x42000000 + 0x20014 × 32 + (0x5 × 0x4) = 0x42400294

Мы можем определить два макроса в Си, которые позволяют легко вычислять адреса слов в области доступа к битам (битовых лент):

1// Определение базового адреса области хранения бит SRAM

2#define BITBAND_SRAM_BASE 0x20000000

3// Определение базового адреса области доступа к битам SRAM

4#define ALIAS_SRAM_BASE 0x22000000

5// Преобразование адресов SRAM (области хранения бит) в адреса области доступа к битам

6#define BITBAND_SRAM(a,b) ((ALIAS_SRAM_BASE + ((uint32_t)&(a)-BITBAND_SRAM_BASE)*32 + \

7(b*4)))

8 9 // Определение базового адреса области хранения бит периферийных устройств

10#define BITBAND_PERI_BASE 0x40000000

11// Определение базового адреса области доступа к битам периферийных устройств

12#define ALIAS_PERI_BASE 0x42000000

13// Преобразование адресов PERI (области хранения бит) в адреса области доступа к битам

14#define BITBAND_PERI(a,b) ((ALIAS_PERI_BASE + ((uint32_t)a-BITBAND_PERI_BASE)*32 + (b*4)))

Продолжая использовать приведенный выше пример, мы можем быстро изменить состояние вывода PIN5 порта GPIOA следующим образом:

1#define GPIOA_PERH_ADDR 0x40020000

2#define ODR_ADDR_OFF 0x14

3

4uint32_t *GPIOA_ODR = GPIOA_PERH_ADDR + ODR_ADDR_OFF;

5uint32_t *GPIOA_PIN5 = BITBAND_PERI(GPIOA_ODR, 5);

6

7 *GPIOA_PIN5 = 0x1; // GPIO переключается на ВЫСОКИЙ

1.1.1.4.Thumb-2 и выравнивание памяти

Исторически процессоры ARM предоставляют систему 32-битных команд. Это не только обеспечивает богатую систему команд, но и также гарантирует наилучшую производительность при выполнении команд, включающих арифметические операции и передачу данных из памяти между регистрами ядра и SRAM. Однако 32-битная система команд имеет высокую стоимость с точки зрения объема памяти встроенного микропро-

9 Любой, кто уже играл с платами Nucleo, знает, что пользовательский светодиод LD2 (зеленый) подключен к этому выводу порта.

Введение в ассортимент микроконтроллеров STM32 |

12 |

граммного обеспечения (или, как говорят, «прошивки», firmware). Это означает, что про-

грамме, написанной с 32-битной Архитектурой системы команд (Instruction Set Architecture, ISA), требуется больший объем Flash-памяти, что влияет на энергопотребление и общие затраты на микроконтроллер (кремниевые подложки дороги, и производители постоянно сокращают размер чипов для снижения их стоимости).

Для решения указанных проблем ARM представила 16-битную систему команд Thumb, которая является подмножеством наиболее часто используемых 32-битных. Инструкции Thumb имеют длину 16 бит и автоматически «переводятся» в соответствующую 32-бит- ную инструкцию ARM, обладающую тем же эффектом в модели процессора. Это означает, что 16-битные инструкции Thumb прозрачно расширяются (с точки зрения разработчика) до полных 32-битных инструкций ARM в режиме реального времени без потери производительности. Код Thumb обычно составляет 65% размера кода ARM и обеспечивает 160% производительность последнего при работе из 16-битной системы памяти; однако в Thumb 16-битные коды операций (opcodes) имеют меньшую функциональность. Например, только ветви (branches) могут быть условными, а многие коды операций ограничены доступом только к половине всех регистров общего назначения ЦПУ.

После этого ARM представила систему команд Thumb-2, представляющую собой смесь 16- и 32-битных систем команд в одном рабочем состоянии. Thumb-2 – это система команд переменной длины, которая предлагает гораздо больше инструкций по сравнению с Thumb, что обеспечивает схожую плотность кода.

Cortex-M3/4/7 предназначен для поддержки полных систем команд Thumb и Thumb-2, а некоторые из них поддерживают другие системы команд, предназначенные для опера-

ций с плавающей точкой (Cortex-M4/7), и инструкции управления потоками данных

(Single Instruction Multiple Data, SIMD-команды) (также известными как инструкции

NEON).

Другой интересной особенностью ядер Cortex-M3/4/7 является возможность делать невыровненный доступ к памяти. Процессоры на базе ARM традиционно способны получать доступ к байту (8-разрядных), полуслову (16-разрядных) и слову (32-разрядных) знаковых и беззнаковых переменных без увеличения количества ассемблерных инструкций, как это происходит в 8-разрядных архитектурах микроконтроллеров. Однако ранние архитектуры ARM не могли осуществлять невыровненный доступ к памяти, что приводило к бесполезной трате ячеек памяти.

Рисунок 7: Разница между выровненным и не выровненным доступом к памяти

Чтобы понять проблему, рассмотрим левую диаграмму на рисунке 7. Здесь у нас есть восемь переменных. В случае выровненного доступа к памяти мы имеем в виду, что для доступа к переменным длиной в слово (1 и 4 на диаграмме) нам нужно получить доступ

Введение в ассортимент микроконтроллеров STM32 |

13 |

к адресам, кратным 32 бит (4 Байт). То есть переменная длиной в слово может быть сохранена только в 0x2000 0000, 0x2000 0004, 0x2000 0008 и так далее. Каждая попытка получить доступ к ячейке, не кратной 4, вызывает исключение отказа программы Usage Fault. Таким образом, следующая псевдокоманда ARM неверна:

STR R2, 0x20000002

То же самое относится к чтению полуслова: можно получить доступ к ячейкам памяти, хранящимся в нескольких байтах: 0x2000 0000, 0x2000 0002, 0x2000 0004 и т. д. Это ограничение вызывает фрагментацию в оперативной памяти. Чтобы решить данную проблему, микроконтроллеры на базе Cortex-M3/4/7 могут осуществлять невыровненный доступ к памяти, как показано на правой диаграмме на рисунке 7. Как мы видим, переменная 4 хранится, начиная с адреса 0x2000 0007 (в ранних архитектурах ARM это было возможно только с однобайтовыми переменными). Это позволяет нам хранить переменную 5 в ячейке памяти 0x2000 000b, в результате чего переменная 8 будет храниться в 0x2000 000e. Теперь память «упакована», и мы сэкономили 4 Байта SRAM.

Однако невыровненный доступ ограничен следующими инструкциями ARM:

•LDR, LDRT

•LDRH, LDRHT

•LDRSH, LDRSHT

•STR, STRT

•STRH, STRHT

1.1.1.5.Конвейер

Всякий раз, когда мы говорим об исполнении инструкций, мы делаем ряд нетривиальных допущений. Перед выполнением инструкции ЦПУ должно извлечь ее из памяти и декодировать. Данная процедура использует несколько тактовых циклов ЦПУ, в зависимости от памяти и архитектуры ядра ЦПУ, которая добавляется к фактической стоимости инструкции (то есть к числу тактовых циклов, необходимых для выполнения этой инструкции).

Современные ЦПУ предоставляют способ распараллеливания данных операций, чтобы увеличить их пропускную способность инструкций (количество инструкций, которые могут быть выполнены за единицу времени). Основной цикл инструкций разбит на последовательность шагов, как если бы инструкции проходили по конвейеру (pipeline). Вместо последовательной обработки каждой инструкции (по одной, заканчивая одну инструкцию перед началом следующей), каждая инструкция разбивается на последовательность шагов, так что различные шаги могут выполняться параллельно.

Рисунок 8: Трехступенчатый конвейер инструкций

Введение в ассортимент микроконтроллеров STM32 |

14 |

Все микроконтроллеры на базе Cortex-M представляют собой конвейерную форму. Наиболее распространенным является трехступенчатый конвейер, как показано на рисунке 8. Трехступенчатый конвейер поддерживается ядрами Cortex-M0/3/4. Ядра Cortex-M0+, которые предназначены для микроконтроллеров с пониженным энергопотреблением, предоставляют двухступенчатый конвейер (хотя конвейеризация помогает сократить временные затраты, связанные с циклом выборки/декодирования/исполнения инструкции, она вводит затраты энергии, которые должны быть минимизированы в приложениях с пониженным энергопотреблением). Ядра Cortex-M7 обеспечивают

шестиступенчатый конвейер.

При работе с конвейерами ветвление является проблемой, требующей решения. Выполнение программы заключается в том, чтобы идти различными путями; это достигается посредством ветвления (if equal goto – если равно, то перейти). К сожалению, ветвление вызывает аннулирование потоков конвейера, как показано на рисунке 9. Последние две инструкции были загружены в конвейер, но они отбрасываются из-за использования дополнительного пути ветвления (мы обычно называем их тенями ветвления, англ. branch shadows)

Рисунок 9: Ветвление при выполнении программы, связанное с конвейерной обработкой

Даже в этом случае есть несколько методов минимизации влияния ветвления. Их часто называют методами прогнозирования ветвления (branching prediction techniques). Идеи, ле-

жащие в основе данных методов, состоят в том, что ЦПУ начинает извлекать и декодировать как инструкции, следующие за ветвлением, так и те, которые будут достигнуты, если произойдет ветвление (на рисунке 9 либо инструкция MOV, либо ADD). Однако существуют и другие способы реализации схемы прогнозирования ветвлений. Если вы хотите глубже изучить данную тему, этот пост1011 на официальном форуме поддержки ARM станет хорошей отправной точкой.

10https://community.arm.com/developer/ip-products/processors/f/cortex-m-forum/3190/cortex-m3-pipeline- stages-branch-prediction

11В оригинальной книге автор использует укороченные ссылки на интернет-ресурсы от сервисов типа bit.ly, которые заблокированы на территории РФ Роскомнадзором. В связи с этим в переводе все заблокированные сокращенные ссылки были заменены на полные. (прим. переводчика)

Введение в ассортимент микроконтроллеров STM32 |

15 |

1.1.1.6.Обработка прерываний и исключений

Обработка прерываний и исключений – одна из самых мощных функций процессоров на базе Cortex-M. Прерывания и исключения являются асинхронными событиями, которые изменяют ход программы. Когда происходит исключение или прерывание, ЦПУ приостанавливает выполнение текущей задачи, сохраняет свой контекст (т. е. свой указатель стека) и начинает выполнение процедуры, предназначенной для обработки события прерывания. Эта процедура называется Обработчиком исключений (Exception Handler) в случае исключений и Процедурой обслуживания прерывания (Interrupt Service Routine, ISR) в случае события прерывания. После обработки исключения или прерывания ЦПУ возобновляет предыдущий поток выполнения, и предыдущая задача может продолжить свое выполнение12.

В архитектуре ARM прерывания являются одним из типов исключений. Прерывания обычно генерируются от встроенных периферийных устройств (например, таймера) или внешних входов (например, тактильного переключателя, подключенного к GPIO), и в некоторых случаях они могут запускаться программно. Исключения, напротив, связаны с выполнением программного обеспечения, а само ЦПУ может быть источником исключений. Это могут быть события отказов, такие как попытка доступа к неверной ячейке памяти, или события, сгенерированные операционной системой, если таковые имеются.

Каждое исключение (а, следовательно, и прерывание) имеет номер, который однозначно идентифицирует его. В таблице 1 показаны предопределенные исключения, общие для всех ядер Cortex-M, а также переменное число пользовательских прерываний, относящихся к управлению. Это число отражает позицию процедуры обработчика исключения внутри таблицы векторов, где хранится фактический адрес процедуры. Например, позиция 15 содержит адрес памяти области кода, содержащей обработчик исключений для прерывания от SysTick, сгенерированного при достижении таймером SysTick нуля.

Кроме первых трех, каждому исключению может быть назначен уровень приоритета, который определяет порядок обработки в случае одновременных прерываний: чем меньше число, тем выше приоритет. Например, предположим, что у нас есть две процедуры прерывания, связанные с внешними входами A и B. Мы можем назначить прерывание с более высоким приоритетом (с более низким числом) для входа A. Если прерывание, связанное с A, поступает при обработке процессором прерывания со входа B, то выполнение B приостанавливается, что позволяет немедленно выполнить процедуру обработки прерывания с более высоким приоритетом.

12 Термин задача (task) означает последовательность команд, которые составляют основной поток выполнения. Если наша микропрограмма (firmware) основана на ОС, сценарий может быть более четко сформулирован. Кроме того, в случае спящего режима с пониженным энергопотреблением, ЦПУ может быть сконфигурировано на возврат в спящий режим после выполнения процедуры обслуживания прерывания.

Введение в ассортимент микроконтроллеров STM32 |

16 |

|||

Номер |

Тип исключения |

Приоритетa |

Описание |

|

1 |

Reset |

-3 |

Сброс |

|

2 |

NMI |

-2 |

Немаскируемое прерывание |

|

|

|

|

Любой отказ, если отказ не может быть |

|

3 |

Hard Fault |

-1 |

активирован из-за приоритета или |

|

программируемый обработчик отказа не |

||||

|

|

|

||

разрешен.

4 |

Memory |

Программируемыйb |

|

Managementc |

|||

|

|

||

5 |

Bus Faultc |

Программируемый |

|

6 |

Usage Faultc |

Программируемый |

Несоответствие MPU, включая нарушение прав доступа и отсутствие совпадений. Используется, даже если модуль MPU отключен или отсутствует.

Отказ предвыборки, отказ доступа к памяти и другие, связанные с адресом/памятью.

Ошибка в программе, такая как выполнение неопределенной инструкции или недопустимая попытка перехода между состояниями.

7-10 |

— |

— |

ЗАРЕЗЕРВИРОВАНО |

11 |

SVCall |

Программируемый |

Вызов системной службы командой SVC. |

12 |

Debug monitorc |

Программируемый |

Монитор отладки – для программной отладки. |

13 |

— |

— |

ЗАРЕЗЕРВИРОВАНО |

14 |

PendSV |

Программируемый |

Отложенный запрос для системной службы |

15 |

SYSTICK |

Программируемый |

Срабатывание системного таймера |

16-[47/240]d |

IRQ |

Программируемый |

Вход внешнего прерывания |

aЧем ниже значение приоритета, тем выше приоритет.

bМожно изменить приоритет исключения, назначив другой номер. Для процессоров Cortex-M0/0+ это число колеблется от 0 до 192 с шагом 64 (т. е. доступно 4 уровня приоритета). Для Cortex-M3/4/7 колеблется от 0 до 255.

cДанные исключения не доступны в Cortex-M0/0+.

dCortex-M0/0+ допускает 32 внешних конфигурируемых прерывания. Cortex-M3/4/7 допускает 240 конфигурируемых внешних прерываний. Однако на практике количество входов прерываний, реализованных в реальном микроконтроллере, намного меньше.

Таблица 1: Типы исключений Cortex-M

И исключения, и прерывания обрабатываются отдельным модулем, который называется

Контроллер вложенных векторных прерываний (Nested Vectored Interrupt Controller, NVIC).

Контроллер NVIC обладает следующими особенностями:

•Гибкое управление исключениями и прерываниями: NVIC может обрабаты-

вать как сигналы/запросы прерываний, поступающие от периферийных устройств, так и исключения, поступающие от ядра процессора, что позволяет нам разрешать/запрещать их в программном обеспечении (кроме NMI13).

•Поддержка вложенных исключений/прерываний: NVIC позволяет назначать уровни приоритета исключениям и прерываниям (кроме первых трех типов исключений), предоставляя возможность классифицировать прерывания в зависимости от потребностей пользователя.

13 Также нельзя запретить исключение сброса Reset, т. к. говорить о запрете исключения сброса некорректно, поскольку это первое исключение, сгенерированное после сброса микроконтроллера. Как мы увидим в Главе 7, исключение сброса является фактической точкой входа для каждого приложения STM32.

Введение в ассортимент микроконтроллеров STM32 |

17 |

•Векторный переход к исключению/прерыванию: NVIC автоматически опреде-

ляет расположение обработчика исключений, связанного с исключением/прерыванием, без необходимости в дополнительном коде.

•Маскирование прерываний: разработчики могут приостанавливать выполнение всех обработчиков исключений (кроме NMI) или приостанавливать некоторые из них на основе уровня приоритета благодаря набору отдельных регистров. Это позволяет выполнять критические задачи безопасным способом, исключив асинхронные прерывания.

•Детерминированное время реакции на прерывание: еще одна интересная осо-

бенность NVIC – детерминированная задержка обработки прерывания, которая равна 12 тактовым циклам для всех ядер Cortex-M3/4, 15 тактовым циклам для Cortex-M0, 16 тактовым циклам для Cortex-M0+ независимо от текущего состояния процессора.

•Перемещение обработчиков исключений: как мы рассмотрим далее, обработ-

чики исключений могут быть перемещены в другие ячейки Flash-памяти, а также в совершенно другую, даже внешнюю память, не ПЗУ (ROM). Это обеспечивает большую степень гибкости для продвинутых приложений.

1.1.1.7.Системный таймер SysTick

Процессоры на базе Cortex-M могут дополнительно предоставлять системный таймер, также известный как SysTick. Хорошей новостью является то, что все устройства STM32 оснащены им, как показано в таблице 3.

SysTick – это 24-разрядный таймер нисходящего отсчета, используемый для предостав-

ления системного тика для операционных систем реального времени (Real Time Operating Systems, RTOS), таких как FreeRTOS. Он используется для того, чтобы генерировать периодические прерывания для запланированных задач. Программисты могут задавать частоту обновления таймера SysTick, устанавливая его регистры. Таймер SysTick также используется HAL для STM32 для генерации точных задержек, даже если мы не используем ОСРВ. Подробнее об этом таймере в Главе 11.

1.1.1.8.Режимы питания

Современная тенденция в электронной промышленности, особенно когда речь идет о разработке мобильных устройств, связана с управлением питанием. Снижение до минимума энергопотребления является основной целью всех разработчиков аппаратных средств и программистов, занимающихся разработкой устройств с батарейным питанием. Процессоры Cortex-M предоставляют несколько уровней управления питанием, которые можно разделить на две основные группы: внутренние особенности и определя-

емые пользователем режимы питания.

Говоря о внутренних особенностях, мы ссылаемся на те естественные возможности, касающиеся энергопотребления, которые определены во время проектирования как ядра Cortex-M, так и всего микроконтроллера. Например, в ядрах Cortex-M0+ устанавливается только двухступенчатый конвейер для снижения энергопотребления при предварительной выборке инструкций. Другое естественное поведение, связанное с управлением питанием, – высокая плотность кода системы команд Thumb-2, которая позволяет разработчикам выбирать микроконтроллеры с меньшей Flash-памятью для снижения энергопотребления.

Введение в ассортимент микроконтроллеров STM32 |

18 |

Рисунок 10: Потребление питания Cortex-M в различных режимах работы

Традиционно процессоры Cortex-M предоставляют определенные пользователем ре-

жимы питания через Регистр управления системой (System Control Register, SCR). При пер-

вом включении запускается Рабочий режим, англ. Run mode (см. рисунок 10), в котором ЦПУ работает на полную мощность. В Рабочем режиме энергопотребление зависит от тактовой частоты и используемых периферийных устройств. Спящий режим (Sleep mode)

— это первый доступный режим пониженного энергопотребления. При активации данного режима большинство функциональных возможностей приостанавливается, частота ЦПУ снижается, а его активность снижается до той, которая необходима для его активации. В режиме Глубокого сна (Deep sleep mode) все тактирование останавливается, и ЦПУ требуется внешнее событие для выхода из этого состояния.

Рисунок 11: Потребляемая мощность STM32F2 в различных режимах питания

Однако данные режимы питания являются только общими моделями, которые в дальнейшем реализуются в реальном микроконтроллере. Например, рассмотрим рисунок 11, отображающий энергопотребление микроконтроллера STM32F2, работающего на

Введение в ассортимент микроконтроллеров STM32 |

19 |

80МГц при 30°C14. Как мы видим, максимальное энергопотребление достигается в Рабочем режиме (т. е. в Активном режиме) при отключенном ускорителе ART™ Accelerator. Используя ускоритель ART™ Accelerator, мы можем сэкономить до 10 мАч, одновременно добиваясь лучших вычислительных характеристик. Все это четко показывает, что реальная реализация микроконтроллера может вводить различные уровни питания.

Семейства STM32Lx предоставляют несколько дополнительных промежуточных уровней питания, позволяя точно выбирать предпочтительный режим питания и, следовательно, производительность и энергопотребление микроконтроллера.

Мы углубимся в данную тему в Главе 19.

1.1.1.9.CMSIS

Одним из ключевых преимуществ платформы ARM (как для производителей интегральных схем, так и для разработчиков приложений) является наличие полного набора инструментов разработки (компиляторы, библиотеки среды выполнения (run-time libraries), отладчики и т. д.), которые могут многократно использоваться несколькими производителями.

ARM также активно работает над способом стандартизации программной инфраструктуры среди производителей микроконтроллеров. Стандарт программного интерфейса микроконтроллеров Cortex (Cortex Microcontroller Software Interface Standard, CMSIS)

представляет собой независимый от производителя уровень аппаратной абстракции для серии процессоров Cortex-M и определяет интерфейсы отладчика. CMSIS состоит из следующих компонентов:

•CMSIS-CORE: API-интерфейс для ядра и периферии процессора Cortex-M. Он обеспечивает стандартизированный интерфейс для Cortex-M0/3/4/7.

•CMSIS-Driver: Определяет общие интерфейсы периферийных драйверов для промежуточного программного обеспечения (middleware), делая их многоразовыми на поддерживаемых устройствах. API-интерфейс не зависит от ОСРВ и соединяет периферийные устройства микроконтроллера с промежуточным программным обеспечением, которое, помимо прочего, реализует стеки связи, файловые системы или графические пользовательские интерфейсы.

•CMSIS-DSP: Коллекция библиотек DSP с более чем 60 функциями для различных типов данных: с фиксированной точкой (дробная q7, q15, q31) и с плавающей точкой одинарной точности (32-разрядная). Библиотека доступна для Cortex-M0, Cortex-M3 и Cortex-M4. Реализация для Cortex-M4 оптимизирована для системы команд SIMD.

•CMSIS-RTOS API: Общий API-интерфейс для операционных систем реального времени. Он обеспечивает стандартизированный интерфейс программирования, который переносится на многие ОСРВ и, следовательно, позволяет использовать программные шаблоны, промежуточное программное обеспечение, библиотеки и другие компоненты, которые могут работать в поддерживаемых ОСРВ. Мы поговорим о данном уровне API-интерфейса в Главе 23.

•CMSIS-Pack: используя файл описания пакета на основе XML с расширением «PDSC», описывает соответствующие пользовательские компоненты и компоненты устройства из коллекции файлов (именуемых «software pack»), которые

14 Источник – ST AN3430