- •Часть II

- •Глава 1 12

- •Глава 2 30

- •Глава 3 52

- •Введение

- •Информационный обмен в промышленных контроллерах.

- •Реализация алгоритмов проверки на достоверность входной информации.

- •Реализация алгоритмов сигнализации.

- •Реализация дискретных систем управления.

- •Реализация аналоговых законов регулирования.

- •Организация связи локальной сети контроллеров с верхним уровнем.

- •Глава 1

- •1. Краткие технические характеристики и возможности контроллера

- •1.1. Блок контроллера бк-1

- •1.2. Блок питания бп-1

- •1.3. Блок переключателей бпр-10

- •1.4. Клеммно-блочные соединители

- •1.5. Модули усо

- •1.6. Схема подключения сигналов к модулю мас

- •1.7. Схема подключения сигналов к модулю мсд

- •Входные аналоговые сигналы

- •Аналоговые выходные унифицированные сигналы:

- •Входные дискретные сигналы:

- •Дискретные выходные сигналы:

- •1.7. Погрешность модулей усо

- •Глава 2

- •2.1. Проверка работоспособности каналов усо

- •2.2. Искробезопасные барьеры

- •2.3. Гальваническая развязка по входным дискретным каналам

- •2.4. Гальваническая развязка по аналоговому каналу

- •2.5. Понятие алгоблока и алгоритма

- •Каждый алгоблок имеет запретную зону, в которой невозможно провести каких-либо линий или расположить часть другого блока (см. Рис.12 и 13).

- •2.6. Алгоритмы ввода- вывода аналоговой информации

- •2.7. Алгоритмы ввода- вывода дискретной информации

- •2.8. Виды сигналов и параметров настройки

- •Диапазон изменения сигналов и параметров

- •2.9. Взаимное соответствие сигналов в контроллере р-130

- •2.10. Команды кросс-средства Редитор р-130

- •2.10.1. Назначение функциональных клавиш

- •2.10.2. Редактирование положения и параметров алгоблока

- •2.10.3. Параметры настройки и начальные значения

- •2.10.4. Соединение алгоблоков

- •2.10.4.1. Графическое конфигурирование

- •2.10.4.1. Адресное конфигурирование

- •Глава 3

- •3.1. Принципы программирования на языке fbd

- •3.2. Меню "Параметры"

- •3.2.1. Системные параметры

- •3.2.2. Ресурсы

- •3.3.3. Сохранение программы

- •3.3.4. Первоначальное сохранение программы

- •3.4.2. Удаление блока/линии

- •3.4.3. Режим перемещения блока

- •3.4.4. Просмотр всей схемы на экране пэвм

- •3.4.5. Увеличение участка программы

- •3.4.6. Поиск блока

- •3.4.7. Перемещение экрана (Перемещение схемы)

- •3.4.8. Исходный размер схемы

- •3.4.9. Загрузка программы в контроллер

- •4. Назначение и функции пульта настройки

- •4.1. Основные операции при работе с пн-1

- •4.2. Начальные установки шлюза и контроллера

- •5. Блок шлюза бш-1

- •6. Процедуры программирования

- •6.1. Приборные параметры

- •6.2. Системные параметры

- •6.3. Установка (вызов в озу) алгоритма с помощью пн-1

- •7. Программирование шлюза

- •8. Программирование контроллера

- •9. Тестирование контроллера Ремиконт р-130

- •9.1. Общий алгоритм тестирования

- •9.2. Особенности тестирования

- •9.3. Перечень тестов

- •9.4. Идентификация отказов и ошибок

- •9.4.1. Идентификация отказов

- •9.4.2. Идентификация ошибок

- •10. Ошибки оператора при работе с пультом настройки

- •Ошибки оператора при работе с пультом настройки пн-1

- •11. Ошибки оператора при работе с лицевой панелью контроллера

- •Ошибки оператора при работе с лицевой панелью контроллера

- •Ошибки оператора при работе с лицевой панелью и в управлении логической программой

- •12. Перевод программы c языка fbd в dxf-формат

- •Алгоритм действий следующий:

- •13. Порядок получения конфигурационной таблицы

- •14. Описание лабораторного стенда р-130

- •14.1. Расположение оборудования в лаборатории автоматизации

- •14.2. Лицевая панель регулирующей модели

- •14.3. Лицевая панель логической модели

- •14.4. Имитатор аналоговых и дискретных сигналов

- •16. Связь локальной сети контроллеров с пэвм

- •17. Интерфейс "Токовая петля" (ирпс)

- •18. Проверка связи пэвм с локальной сетью контроллеров

- •19. Типовые ошибки студентов

- •Литература

- •Приложение а Справочная информация по алгоритмам а1. Принятые сокращения

- •А2. Алгоритмы лицевой панели око (01) ‑ Оперативный контроль регулирования

- •Окл (02) ‑ Оперативный контроль логической программы

- •Дик (04) – Алгоритм дискретного контроля

- •А3. Алгоритмы интерфейсного ввода-вывода вин (05) ‑ Ввод интерфейсный

- •А5. Алгоритмы регулирования ран (20) ‑ Регулирование аналоговое

- •Рим (21) – Регулирование импульсное

- •Здн (24) – Задание

- •Здл (25) ‑ Задание локальное

- •Руч (26) ‑ Ручное управление

- •Прз (27) ‑ Программный задатчик

- •Инз (28) ‑ Интегрирующий задатчик

- •Пок (29) ‑ Пороговый контроль

- •Анр (30) – Автонастройка регулятора

- •А6. Динамические преобразования инт (33) – Интегрирование

- •Фил (35) – Фильтрация

- •Дин (36) ‑ Динамическое преобразование

- •Диб (37) ‑ Динамическая балансировка

- •Огс (38) – Ограничение скорости

- •Зап (39) – Запаздывание

- •А7. Статические преобразования сум (42) – Суммирование

- •Сма (43) Суммирование с масштабированием

- •Огр (48) Ограничение

- •Скс (49) Скользящее среднее

- •Дис (50) Дискретное среднее

- •Имп (61) Импульсатор

- •Заи (62) Запрет изменения

- •Заз (63) Запрет знака

- •Слз (64) Слежение-запоминание

- •Зпм (65) Запоминание

- •Вот (67) Выделение отключения

- •Бос (66) Блокировка обратного счета

- •А9. Логические операции

- •Лои (70) Логическая операция и

- •Мни (71) Логическая операция многовходовое и

- •Или (72) Логическая операция или

- •Счи (86) Сравнение чисел

- •Вчи (87) Выделение чисел

- •Удп (88) Управление двухпозиционной нагрузкой

- •Утп (89) Управление трехпозиционной нагрузкой

- •Шиф (90) Шифратор

- •Деш (91) Дешифратор

- •Лок (92) логический контроль

- •А11. Групповое непрерывно-дискретное управление шап (94) Шаговая программа

- •Инр (07) - Интерфейсный вывод радиальный

- •Ва (10) - Ввод аналоговый

- •Вд (11) - Ввод дискретный

- •Вап(12) - Ввод аналоговый помехозащищенный

- •Ав (13) - Аналоговый вывод

- •Диф (34) – Дифференцирование

- •Пен (58) - Переключатель по номеру

- •Пор (59) - Пороговый элемент

- •Нор (60) - Нуль-орган

- •Дло (70) - Двухвходовая логическая операция

- •Мло (71) - Многовходовая логическая операция

- •Выф (79) - Выделение фронта

- •Одв (83) – Одновибратор и мув (84) – Мультивибратор

- •Цсв (100) - Преобразование целого числа в вещественное

- •Вцс (101) - Преобразование вещественного числа в целое

- •Дпв (102) - Преобразование дискретного значения в вещественное

- •Дпц (103) - Преобразование дискретного значения в целое

- •Шцс (109) - Шифратор целых чисел

- •Дшц (110) - Дешифратор целых чисел

- •Шдп (111) - Шифратор дискретных переменных

- •Ддп (112) - Дешифратор дискретных переменных

- •Увч (113) - Упаковка вещественных чисел

- •Рвч (114) - Распаковка вещественных чисел

- •Мкс (115) - Многоканальный коммутатор сигналов

- •Мдс (116) - Многоканальный дешифратор сигналов

- •Алгоритмы регистрации и архивации данных

- •Рег (121) - Регистратор процессов

- •Арх (122) - Архиватор процессов

- •Рес (123) - Регистратор событий

- •Арс (124) - Архиватор событий

- •Приложение б Языки программирования промышленных контроллеров

- •Приложение в Кросс-средства UltraLogik и iSaGraf

- •В1. Основные характеристики UltraLogik

- •В2. Возможности iSaGraf

- •Приложение г Элементы математической логики

А7. Статические преобразования сум (42) – Суммирование

Алгоритм используется для суммирования (без масштабирования) нескольких (до 21) сигналов.

Выходной сигнал алгоритма равен Y = X0 + X1 + X2 +... + Xm.

Число дополнительных (к Х0) суммируемых сигналов 0 <= m <= 20 задается модификатором. При m=0 на входе имеется сигнал Х0, при m=1 - сигнал Х0 и Х1 и т.д.

Алгоритм не инициирует обратный счет, но если по инициативе других алгоритмов на каскадный выход Y приходит команда отключения со значением начальных условий Y0, алгоритм выполняет процедуру обратного счета, формируя на каскадном входе Х0 сигнал Х0 = Y0 - (Х1 + Х2 +... + Хm).

Этот сигнал вместе с командой отключения транслируется предвключенному алгоритму.

Рисунок 30

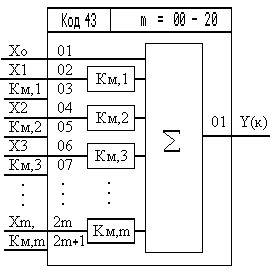

Сма (43) Суммирование с масштабированием

Рисунок 31

Км,i – коэффициент масштабирования i- го слагаемого. Алгоритм используется для получения взвешенной суммы нескольких (до 21) сигналов. В частности, он применяется вместе с алгоритмами регулирования для построения регуляторов соотношения либо для введения статической коррекции.

Число масштабируемых и суммируемых сигналов 0 <= m <= 20 и задается модификатором (немасштабируемый сигнал Х0 имеется всегда, независимо от значения модификатора).

Выходной сигнал алгоритма Y равен Х0+Км1*Х1+…+Км,m*Хm.

Алгоритм не инициирует обратный счет, но если по инициативе других алгоритмов на каскадный выход Y поступает команда отключения со значением начальных условий Y0, алгоритм выполняет процедуру обратного счета, формируя на каскадном входе Х0 сигнал рис. 10.39б

Этот сигнал вместе с командой отключения через вход Х0 транслируется предвключенному алгоритму.

Алгоритм не реагирует на команду запрета, но эта команда через вход Х0 транслируется предвключенному алгоритму.

УМД (44) Умножение-деление

Рисунок 32

КОР (45) Корень квадратный

Рисунок 33

МОД (46) Модуль

Рисунок 34

КУС (47) Кусочно-линейная функция

Рисунок 35

Алгоритм применяется для линеаризации нелинейной зависимости (например, датчика или регулирующего органа), а также для искусственного введения нелинейности (например, зоны нечувствительности, релейной характеристики и т.п.).

Выходной сигнал Y связан со значением сигнала на входе Х зависимостью, показанной на рис.36 и рис.37. Число отрезков определяется модификатором m и может задаваться в пределах 0<=m<=49. Координата конца отрезка определяется парой сигналов Хi, Yi(абсцисса и ордината конца отрезка), которые задаются соответствующими значениями сигналов на настроечных входах алгоритма.

При Х < Х1 и Х > Хm выходной сигнал Y=const. На выходе Nуч формируется число, равное номеру текущего участка кусочно-линейной зависимости (рис. 35).

Координаты Xi, Yi могут находиться в любом из четырех квадрантов. Как правило, координата Хi >= Хi-1 (i - номер отрезка). Если задано Хi < Хi-1, то формируется функция, показанная на рис.37. Можно задавать Хi=Х . В этом случае формируется функция, показанная на рис.38, причем при Хi=Х=Х выход Y=Yi. Алгоритм работает правильно, если Yi+1 - Yi <= 200%. При m=0 выходной сигнал Y=0 независимо от Х.

Рисунок 36

Рисунок 37

Рисунок 38