- •Раздел 2 принципы построения и функционирования эвм и вычислительных систем (вс)

- •2.1. Структура эвм

- •2.2. Системы счисления

- •2.3. Формы представления чисел

- •2.3.1. Форма представления чисел с фиксированной точкой

- •2.3.2. Форма представления чисел с плавающей точкой

- •2.3.3. Форматы двоично-десятичных чисел

- •2.3. Машинные коды

- •2.3.1. Прямой код

- •2.3.2. Обратный код

- •2.3.3. Дополнительный код

- •2.4. Перевод чисел из одной системы представления в другую

- •2.4.1. Перевод между основаниями, составляющими степень двойки

- •2.4.2. Перевод целого числа из десятичного счисления в другое

- •2.4.3. Перевод дробного числа из десятичного счисления в другое

- •2.4.4. Перевод чисел в десятичную систему счисления

- •2.5. Арифметические действия над двоичными числами

- •2.5.1. Сложение

- •2.5.2. Вычитание

- •2.5.3. Умножение

- •2.5.4. Деление

- •2.6. Понятие алгебры логики

- •2.7. Простейшие логические функции

- •2.7.1. Логическая операция конъюнкция (логическое умножение)

- •2.7.2. Логическая операция дизъюнкция (логическое сложение)

- •2.7.3. Логическая операция инверсия (отрицание)

- •2.7.4. Логическая операция сложение по модулю 2

- •2.7.5. Логическая операция эквивалентность (функция тождества)

- •2.7.6. Логическая операция импликация (логическое следование)

- •2.7.7. Функция Шеффера

- •2.7.8. Стрелка Пирса ав, или функция Вебба a b

- •2.8. Основные правила преобразования формул

- •2.9. Кодирование текстовой информации

- •2.10. Составные части компьютера

- •2.11. Логические элементы

- •2.12. Триггеры

- •2.12.1. Общие сведения о триггерах

- •2.12.2. Асинхронный rs-триггер

- •2.12.3. Синхронный rs-триггер

- •2.12.3. Двухтактный rs-триггер

- •2.12.4. Асинхронный и синхронный d-триггеры

- •2.12.5. T-триггер

- •2.12.6. Jk-триггер

- •2.13. Типовые узлы комбинационного типа

- •2.13.1. Дешифраторы

- •2.13.2. Одноразрядный сумматор

- •2.13.3. Полусумматор

- •2.13.4. Многоразрядные сумматоры

- •2.13.5. Двоично-десятичные сумматоры

- •2.13.6. Мультиплексоры

- •2.13.7. Демультиплексоры

- •2.14. Типовые узлы накапливающего типа

- •2.14.1. Регистры

- •2.14.2. Счетчики

- •2.14.3. Двоично-десятичные счетчики

- •2.15. Классификация архитектур системы команд

- •2.15.1. Классификация по составу и сложности команд

- •2.15.2. Классификация по месту хранения операндов

- •2.15.3. Стековая архитектура

- •2.15.4. Аккумуляторная архитектура

- •2.15.5. Регистровая архитектура

- •2.15.6. Архитектура с выделенным доступом к памяти

- •2.16. Типы команд

- •2.16.1. Команды пересылки данных

- •2.16.2. Команды арифметической и логической обработки

- •2.16.3. Операции с целыми числами

- •2.16.4. Операции с числами в форме с плавающей запятой

- •2.16.5. Логические операции

- •2.16.6. Операции сдвигов

- •2.16.7. Операции с десятичными числами

- •2.16.8. Simd-команды

- •2.16.9. Команды для работы со строками

- •2.16.10. Команды преобразования

- •2.16.11. Команды ввода/вывода

- •2.16.12. Команды управления системой

- •2.16.13. Команды управления потоком команд

- •2.17. Формат команд

- •2.17.1. Длина команды

- •2.17.2. Разрядность полей команды

- •2.17.3. Выбор адресности команд

- •2.18. Способы адресации операндов

- •2.18.1. Непосредственная адресация

- •2.18.2. Прямая адресация

- •2.18.3. Косвенная адресация

- •2.18.4. Регистровая адресация

- •2.18.5. Косвенная регистровая адресация

- •2.18.6. Адресация со смещением

- •2.18.7. Относительная адресация

- •2.18.8. Базовая регистровая адресация

- •2.18.9. Индексная адресация

- •2.18.10. Страничная адресация

- •2.18.11. Блочная адресация

- •2.18.12. Распространенность различных видов адресации

- •2.19. Способы адресации в командах управления потоком команд

- •2.20. Функциональная организация фон-неймановской вычислительной машины

- •2.20.1. Устройство управления

- •2.20.2. Арифметико-логическое устройство

- •2.20.3. Основная память

- •2.20.4. Модуль ввода/вывода

- •2.21. Цикл команды

- •2.21.1. Стандартный цикл команды

- •2.21.2. Описание стандартных циклов команды для гипотетической машины

- •2.21.3. Машинный цикл с косвенной адресацией

2.14.2. Счетчики

Счетчики предназначены для подсчета

числа входных сигналов. Обычно входными

сигналами являются импульсы напряжения.

Результат счета – это число, представленное

в двоичной или двоично-десятичной

системе счисления. В двоичном счетчике

число разрядов зависит от модуля счета

М (коэффициента пересчета), который

определяет число состояний счетчика

При поступлении на вход счетчика М

импульсов счетчик возвращается в

исходное состояние, после этого состояния

счетчика повторяются. Модуль счета на

единицу больше максимального числа

Ксч,

которое может зафиксировать счетчик.

В двоичных счетчиках с естественным

порядком счета

,

где п – разрядность счетчика. Тогда

,

где п – разрядность счетчика. Тогда

.

Такие счетчики имеют наиболее простую

схему и строятся на Т- или JK-триггерах.

.

Такие счетчики имеют наиболее простую

схему и строятся на Т- или JK-триггерах.

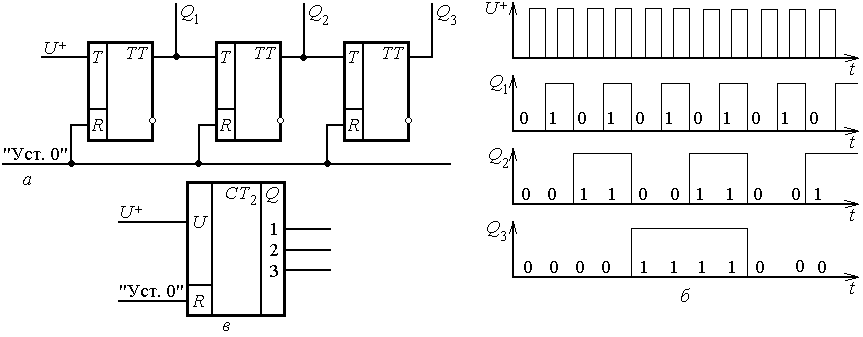

В зависимости от направления счета счетчики могут быть суммирующими, вычитающими и реверсивными. Суммирующие счетчики при поступлении каждого входного импульса увеличивают показания на единицу, вычитающие – уменьшают. Реверсивные счетчики могут работать как в режиме суммирования, так и в режиме вычитания. Схемы трехразрядных двоичных счетчиков показаны на рис. 2.40, 2.41. Счетчики построены на двухтактных T-триггерах с дополнительными входами для установки счетчика в начальное состояние.

Рис. 2.40. Суммирующий счетчик:

а – схема; б – временная диаграмма;

в – условное графическое обозначение

В суммирующем счетчике начальное

(нулевое) состояние счетчика задается

управляющим сигналом «Уст 0» (рис 2.40,

а). Входные импульсы

поступают на вход триггера младшего

разряда Т. Этот триггер изменяет

состояние по спаду каждого входного

импульса, остальные триггеры меняют

состояние по спаду сигнала на прямом

выходе триггера соседнего младшего

разряда. Таким образом, второй триггер

меняет состояние после каждого второго

импульса, третий – после каждого

четвертого и т.д. При подаче на вход

счетчика последовательности импульсов

счетчик меняет состояния в соответствии

с временной диаграммой (рис. 2.40, б).

Так как триггер с выходом Q1,

фиксирует младший разряд результата

счета, то состояния счетчика меняются

в последовательности, соответствующей

логике работы суммирующего счетчика

по модулю 8:

поступают на вход триггера младшего

разряда Т. Этот триггер изменяет

состояние по спаду каждого входного

импульса, остальные триггеры меняют

состояние по спаду сигнала на прямом

выходе триггера соседнего младшего

разряда. Таким образом, второй триггер

меняет состояние после каждого второго

импульса, третий – после каждого

четвертого и т.д. При подаче на вход

счетчика последовательности импульсов

счетчик меняет состояния в соответствии

с временной диаграммой (рис. 2.40, б).

Так как триггер с выходом Q1,

фиксирует младший разряд результата

счета, то состояния счетчика меняются

в последовательности, соответствующей

логике работы суммирующего счетчика

по модулю 8:

Условное графическое обозначение суммирующего счетчика показано на рис. 2.40, в.

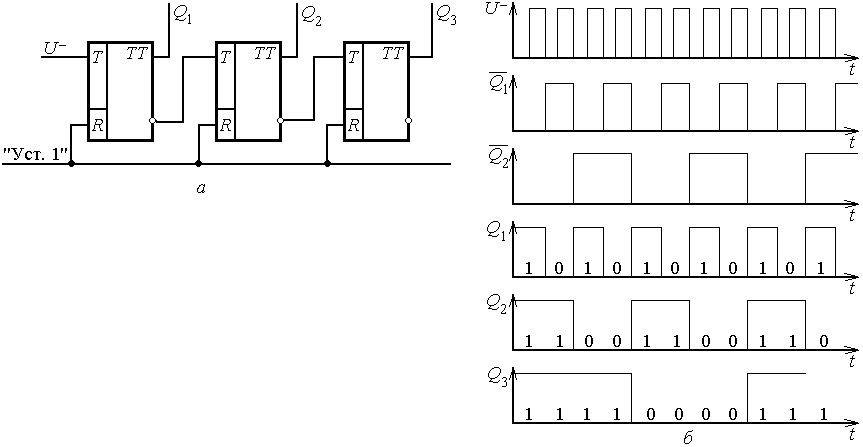

В вычитающих счетчиках на входы старших разрядов подаются сигналы с инверсных выходов триггеров младших разрядов. В начальном состоянии счетчика все триггеры установлены в состояние «1» сигналом «Уст. 1» (см. рис. 2.41, а). При поступлении входных импульсов первый триггер меняет состояние по спаду каждого входного импульса, а все остальные – по спаду сигнала на инверсном выходе триггера соседнего младшего разряда. Последовательность изменения состояний счетчика показана на временной диаграмме (рис. 2.41, б) и соответствует логике работы вычитающего счетчика по модулю 8:

Рис. 2.41. Вычитающий счетчик:

а – схема; б – временная диаграмма работы

В рассмотренных счетчиках входной сигнал (в худшем случае) должен последовательно пройти через все триггеры. Такие счетчики называются счетчиками с последовательными переносами. Для повышения быстродействия используют схемы со сквозными или параллельными переносами.

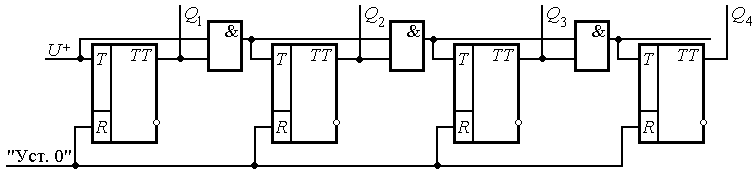

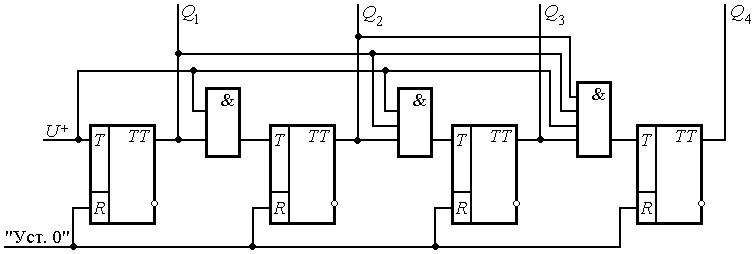

В счетчиках со сквозными переносами сигнал переноса последовательно проходит мимо каждого триггера, находящегося в состоянии «1», через вентиль на два входа. В таком счетчике время установления состояния пропорционально числу вентилей, т.е. разрядности счетчика. Схема суммирующего счетчика со сквозными переносами показана на рис. 2.42.

Рис. 2.42. Счетчик со сквозными переносами

Счетчики с параллельными переносами используют вентили с большим числом входов. Это позволяет сигналам переноса проходить мимо группы триггеров, находящихся в состоянии «1». Схема суммирующего счетчика с параллельными переносами показана на рис. 2.43.

Рис. 2.43. Счетчик с параллельными переносами