- •Раздел 2 принципы построения и функционирования эвм и вычислительных систем (вс)

- •2.1. Структура эвм

- •2.2. Системы счисления

- •2.3. Формы представления чисел

- •2.3.1. Форма представления чисел с фиксированной точкой

- •2.3.2. Форма представления чисел с плавающей точкой

- •2.3.3. Форматы двоично-десятичных чисел

- •2.3. Машинные коды

- •2.3.1. Прямой код

- •2.3.2. Обратный код

- •2.3.3. Дополнительный код

- •2.4. Перевод чисел из одной системы представления в другую

- •2.4.1. Перевод между основаниями, составляющими степень двойки

- •2.4.2. Перевод целого числа из десятичного счисления в другое

- •2.4.3. Перевод дробного числа из десятичного счисления в другое

- •2.4.4. Перевод чисел в десятичную систему счисления

- •2.5. Арифметические действия над двоичными числами

- •2.5.1. Сложение

- •2.5.2. Вычитание

- •2.5.3. Умножение

- •2.5.4. Деление

- •2.6. Понятие алгебры логики

- •2.7. Простейшие логические функции

- •2.7.1. Логическая операция конъюнкция (логическое умножение)

- •2.7.2. Логическая операция дизъюнкция (логическое сложение)

- •2.7.3. Логическая операция инверсия (отрицание)

- •2.7.4. Логическая операция сложение по модулю 2

- •2.7.5. Логическая операция эквивалентность (функция тождества)

- •2.7.6. Логическая операция импликация (логическое следование)

- •2.7.7. Функция Шеффера

- •2.7.8. Стрелка Пирса ав, или функция Вебба a b

- •2.8. Основные правила преобразования формул

- •2.9. Кодирование текстовой информации

- •2.10. Составные части компьютера

- •2.11. Логические элементы

- •2.12. Триггеры

- •2.12.1. Общие сведения о триггерах

- •2.12.2. Асинхронный rs-триггер

- •2.12.3. Синхронный rs-триггер

- •2.12.3. Двухтактный rs-триггер

- •2.12.4. Асинхронный и синхронный d-триггеры

- •2.12.5. T-триггер

- •2.12.6. Jk-триггер

- •2.13. Типовые узлы комбинационного типа

- •2.13.1. Дешифраторы

- •2.13.2. Одноразрядный сумматор

- •2.13.3. Полусумматор

- •2.13.4. Многоразрядные сумматоры

- •2.13.5. Двоично-десятичные сумматоры

- •2.13.6. Мультиплексоры

- •2.13.7. Демультиплексоры

- •2.14. Типовые узлы накапливающего типа

- •2.14.1. Регистры

- •2.14.2. Счетчики

- •2.14.3. Двоично-десятичные счетчики

- •2.15. Классификация архитектур системы команд

- •2.15.1. Классификация по составу и сложности команд

- •2.15.2. Классификация по месту хранения операндов

- •2.15.3. Стековая архитектура

- •2.15.4. Аккумуляторная архитектура

- •2.15.5. Регистровая архитектура

- •2.15.6. Архитектура с выделенным доступом к памяти

- •2.16. Типы команд

- •2.16.1. Команды пересылки данных

- •2.16.2. Команды арифметической и логической обработки

- •2.16.3. Операции с целыми числами

- •2.16.4. Операции с числами в форме с плавающей запятой

- •2.16.5. Логические операции

- •2.16.6. Операции сдвигов

- •2.16.7. Операции с десятичными числами

- •2.16.8. Simd-команды

- •2.16.9. Команды для работы со строками

- •2.16.10. Команды преобразования

- •2.16.11. Команды ввода/вывода

- •2.16.12. Команды управления системой

- •2.16.13. Команды управления потоком команд

- •2.17. Формат команд

- •2.17.1. Длина команды

- •2.17.2. Разрядность полей команды

- •2.17.3. Выбор адресности команд

- •2.18. Способы адресации операндов

- •2.18.1. Непосредственная адресация

- •2.18.2. Прямая адресация

- •2.18.3. Косвенная адресация

- •2.18.4. Регистровая адресация

- •2.18.5. Косвенная регистровая адресация

- •2.18.6. Адресация со смещением

- •2.18.7. Относительная адресация

- •2.18.8. Базовая регистровая адресация

- •2.18.9. Индексная адресация

- •2.18.10. Страничная адресация

- •2.18.11. Блочная адресация

- •2.18.12. Распространенность различных видов адресации

- •2.19. Способы адресации в командах управления потоком команд

- •2.20. Функциональная организация фон-неймановской вычислительной машины

- •2.20.1. Устройство управления

- •2.20.2. Арифметико-логическое устройство

- •2.20.3. Основная память

- •2.20.4. Модуль ввода/вывода

- •2.21. Цикл команды

- •2.21.1. Стандартный цикл команды

- •2.21.2. Описание стандартных циклов команды для гипотетической машины

- •2.21.3. Машинный цикл с косвенной адресацией

2.14. Типовые узлы накапливающего типа

2.14.1. Регистры

Регистры предназначены для приема, временного хранения и выдачи данных. Чаще всего данные сохраняются в регистре на время выполнения одной или нескольких машинных команд. Кроме хранения данных регистры могут выполнять и другие операции (сдвиг данных, логические операции). Основу регистра составляют триггеры, число которых равно разрядности хранимых данных.

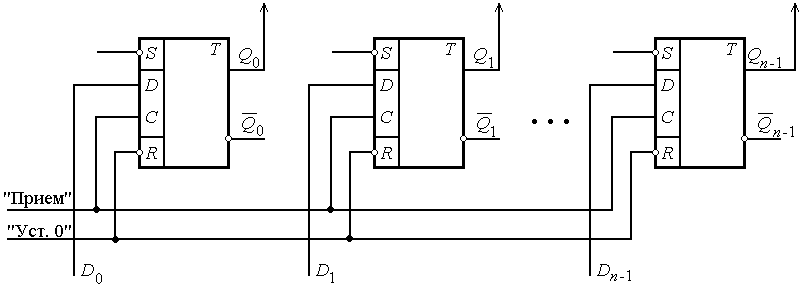

Наиболее простую схему имеет регистр с параллельной записью данных. На рис. 2.34 приведена схема регистра, построенного на синхронных D-триггерах с дополнительными асинхронными входами S и R. Записываемые данные (D0 ... Dn - 1) подаются на информационные входы триггеров. Запись производится при поступлении сигнала «Прием», подаваемого в определенный момент времени на входы синхронизации всех триггеров регистра. Для установки регистра в состояние «0» используется сигнал «Уст. 0», который подается на дополнительные входы триггеров R.

Рис. 2.34. Регистр с параллельной записью

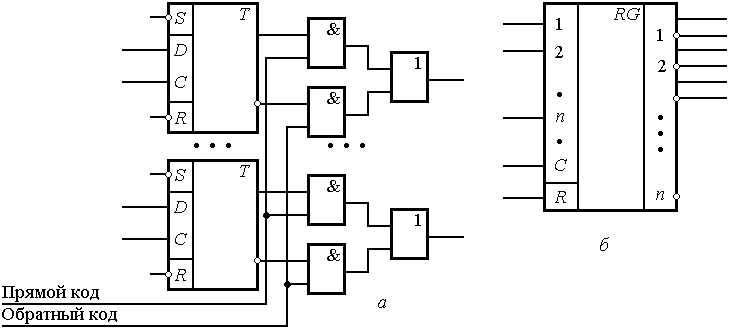

Данные из регистра с параллельной записью и входом установки в состояние «0» могут быть выданы в прямом или обратном (инверсном) коде (рис. 2.35, а). Условное графическое обозначение регистра показано на рис. 2.35, б.

Рис. 2.35. Регистр:

а – схема выдачи данных из регистра; б – условное графическое обозначение

Для выдачи данных из регистра в прямом или обратном коде подается соответствующий управляющий сигнал.

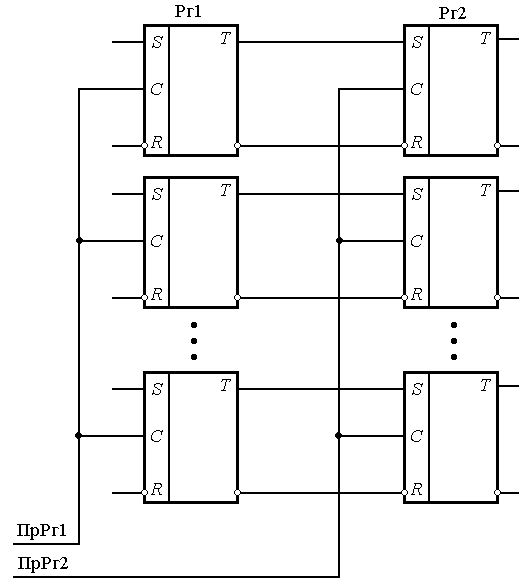

Данные обычно выдаются из одного регистра и одновременно принимаются в другой (рис. 2.36). При этом используются регистры, построенные на синхронных RS-триггерах, а передача данных осуществляется в парафазном коде. В этом случае прием данных в регистр Рг1 производится при поступлении сигнала ПрРг1, а запись данных из Рг1 в регистр Рг2 – при поступлении сигнала ПрРг2.

Рис. 2.36. Схема передачи данных из регистра в регистр

Передача данных между регистрами может выполняться как прямо, т.е. без изменения номеров разрядов, так и со сдвигом влево или вправо на один или несколько разрядов.

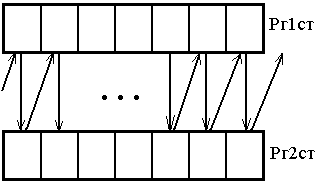

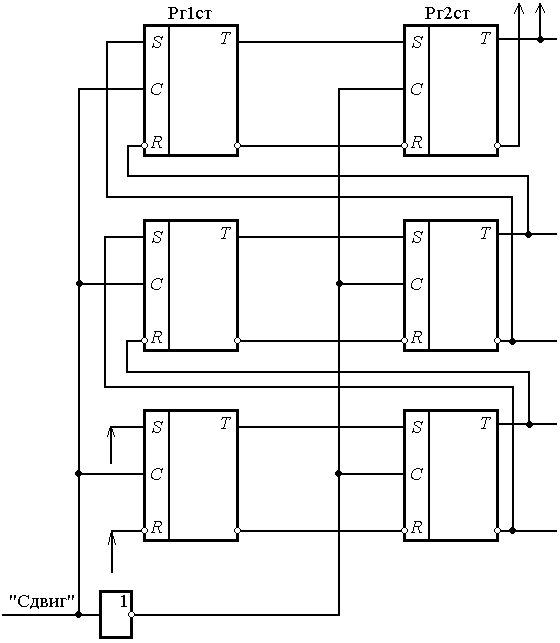

Для сдвига информации в пределах одного регистра используются сдвигающие регистры (рис. 2.37). Сложность сдвига заключается в том, что каждый разряд регистра должен одновременно принять новую и передать старую информацию. Для устойчивой работы сдвигающего регистра в каждом разряде используют два однотактных триггера или один двухтактный, т.е. сдвигающий регистр фактически состоит из двух регистров.

Сдвигающий регистр представляет собой сдвоенный регистр и состоит из регистров первой (Рг1ст) и второй (Рг2ст) ступеней, между которыми производится обмен данными. Перед сдвигом в регистрах первой и второй ступеней записана одна и та же информация. При сдвиге данные сначала передаются из Рг2ст в Рг1ст со сдвигом вправо, затем возвращаются в Рг2ст без сдвига.

Рис. 2.37. Схема сдвига данных на один разряд вправо

Схема регистра сдвига на один разряд вправо, выполненного на однотактных RS-триггерах, приведена на рис. 2.38. Сдвиг производится при поступлении сигнала «Сдвиг». Каждый сигнал «Сдвиг» вызывает сдвиг данных на один разряд. При этом в освободившийся разряд записывается «0», а данные, выходящие из регистра, теряются.

Рис. 2.38. Регистр сдвига вправо

Аналогичным образом можно построить регистр сдвига вправо, регистр со сдвигом данных на несколько разрядов в одном такте или реверсивный сдвигающий регистр, позволяющий сдвигать данные влево или вправо в зависимости от управляющего сигнала.

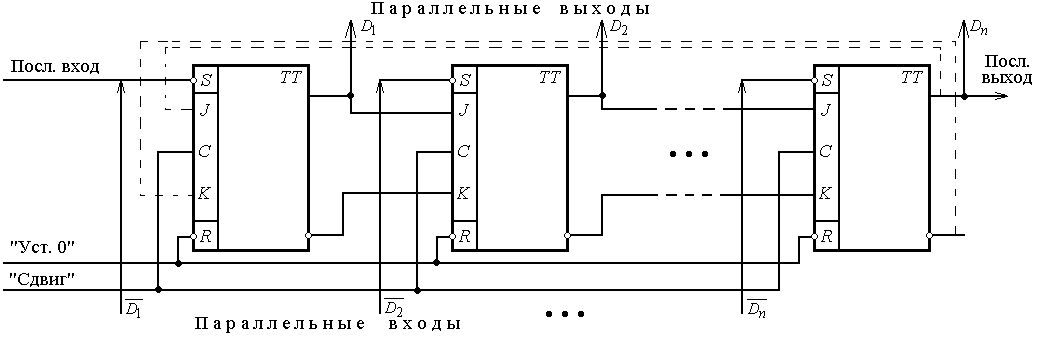

На основе сдвигающего регистра можно построить преобразователь последовательного кода в параллельный, и наоборот (рис. 2.39).

Преобразователь выполнен на основе регистра со сдвигом данных вправо на один разряд. Регистр сдвига состоит из двухтактных JK-триггеров с дополнительными асинхронными входами S и R. Для преобразования параллельного кода в последовательный регистр устанавливается в нулевое состояние сигналом «Уст. 0». Затем данные в параллельном коде поступают на дополнительные входы регистра S. При подаче сигнала «Сдвиг» данные в последовательном коде выдаются на последовательный выход регистра. Для преобразования последовательного кода в параллельный данные подаются на последовательный вход одновременно с поступлением сигналов «Сдвиг». После заполнения регистра данные могут быть выданы в параллельном коде с выходов D1, D2, ..., Dn-1.

Рис. 2.39. Преобразователь параллельного кода в последовательный

Подача сигналов с выходов последнего триггера на входы J и К первого триггера позволяет получить кольцевой регистр сдвига, в котором разряды данных последовательно проходят через все триггеры, а состояние регистра периодически повторяется.