- •Раздел 2 принципы построения и функционирования эвм и вычислительных систем (вс)

- •2.1. Структура эвм

- •2.2. Системы счисления

- •2.3. Формы представления чисел

- •2.3.1. Форма представления чисел с фиксированной точкой

- •2.3.2. Форма представления чисел с плавающей точкой

- •2.3.3. Форматы двоично-десятичных чисел

- •2.3. Машинные коды

- •2.3.1. Прямой код

- •2.3.2. Обратный код

- •2.3.3. Дополнительный код

- •2.4. Перевод чисел из одной системы представления в другую

- •2.4.1. Перевод между основаниями, составляющими степень двойки

- •2.4.2. Перевод целого числа из десятичного счисления в другое

- •2.4.3. Перевод дробного числа из десятичного счисления в другое

- •2.4.4. Перевод чисел в десятичную систему счисления

- •2.5. Арифметические действия над двоичными числами

- •2.5.1. Сложение

- •2.5.2. Вычитание

- •2.5.3. Умножение

- •2.5.4. Деление

- •2.6. Понятие алгебры логики

- •2.7. Простейшие логические функции

- •2.7.1. Логическая операция конъюнкция (логическое умножение)

- •2.7.2. Логическая операция дизъюнкция (логическое сложение)

- •2.7.3. Логическая операция инверсия (отрицание)

- •2.7.4. Логическая операция сложение по модулю 2

- •2.7.5. Логическая операция эквивалентность (функция тождества)

- •2.7.6. Логическая операция импликация (логическое следование)

- •2.7.7. Функция Шеффера

- •2.7.8. Стрелка Пирса ав, или функция Вебба a b

- •2.8. Основные правила преобразования формул

- •2.9. Кодирование текстовой информации

- •2.10. Составные части компьютера

- •2.11. Логические элементы

- •2.12. Триггеры

- •2.12.1. Общие сведения о триггерах

- •2.12.2. Асинхронный rs-триггер

- •2.12.3. Синхронный rs-триггер

- •2.12.3. Двухтактный rs-триггер

- •2.12.4. Асинхронный и синхронный d-триггеры

- •2.12.5. T-триггер

- •2.12.6. Jk-триггер

- •2.13. Типовые узлы комбинационного типа

- •2.13.1. Дешифраторы

- •2.13.2. Одноразрядный сумматор

- •2.13.3. Полусумматор

- •2.13.4. Многоразрядные сумматоры

- •2.13.5. Двоично-десятичные сумматоры

- •2.13.6. Мультиплексоры

- •2.13.7. Демультиплексоры

- •2.14. Типовые узлы накапливающего типа

- •2.14.1. Регистры

- •2.14.2. Счетчики

- •2.14.3. Двоично-десятичные счетчики

- •2.15. Классификация архитектур системы команд

- •2.15.1. Классификация по составу и сложности команд

- •2.15.2. Классификация по месту хранения операндов

- •2.15.3. Стековая архитектура

- •2.15.4. Аккумуляторная архитектура

- •2.15.5. Регистровая архитектура

- •2.15.6. Архитектура с выделенным доступом к памяти

- •2.16. Типы команд

- •2.16.1. Команды пересылки данных

- •2.16.2. Команды арифметической и логической обработки

- •2.16.3. Операции с целыми числами

- •2.16.4. Операции с числами в форме с плавающей запятой

- •2.16.5. Логические операции

- •2.16.6. Операции сдвигов

- •2.16.7. Операции с десятичными числами

- •2.16.8. Simd-команды

- •2.16.9. Команды для работы со строками

- •2.16.10. Команды преобразования

- •2.16.11. Команды ввода/вывода

- •2.16.12. Команды управления системой

- •2.16.13. Команды управления потоком команд

- •2.17. Формат команд

- •2.17.1. Длина команды

- •2.17.2. Разрядность полей команды

- •2.17.3. Выбор адресности команд

- •2.18. Способы адресации операндов

- •2.18.1. Непосредственная адресация

- •2.18.2. Прямая адресация

- •2.18.3. Косвенная адресация

- •2.18.4. Регистровая адресация

- •2.18.5. Косвенная регистровая адресация

- •2.18.6. Адресация со смещением

- •2.18.7. Относительная адресация

- •2.18.8. Базовая регистровая адресация

- •2.18.9. Индексная адресация

- •2.18.10. Страничная адресация

- •2.18.11. Блочная адресация

- •2.18.12. Распространенность различных видов адресации

- •2.19. Способы адресации в командах управления потоком команд

- •2.20. Функциональная организация фон-неймановской вычислительной машины

- •2.20.1. Устройство управления

- •2.20.2. Арифметико-логическое устройство

- •2.20.3. Основная память

- •2.20.4. Модуль ввода/вывода

- •2.21. Цикл команды

- •2.21.1. Стандартный цикл команды

- •2.21.2. Описание стандартных циклов команды для гипотетической машины

- •2.21.3. Машинный цикл с косвенной адресацией

2.15.6. Архитектура с выделенным доступом к памяти

В архитектуре с выделенным доступом к памяти обращение к основной памяти возможно только с помощью двух специальных команд: load и store. Команда load (загрузка) обеспечивает считывание значения из основной памяти и занесение его в регистр процессора (в команде обычно указывается адрес ячейки памяти и номер регистра). Пересылка информации в противоположном направлении производится командой store (сохранение). Операнды во всех командах обработки информации могут находиться только в регистрах процессора (чаще всего в регистрах общего назначения). Результат операции также заносится в регистр.

В архитектуре отсутствуют команды обработки, допускающие прямое обращение к основной памяти. Допускается наличие в архитектуре структуры команд ограниченного числа команд, где операнд является частью кода команды.

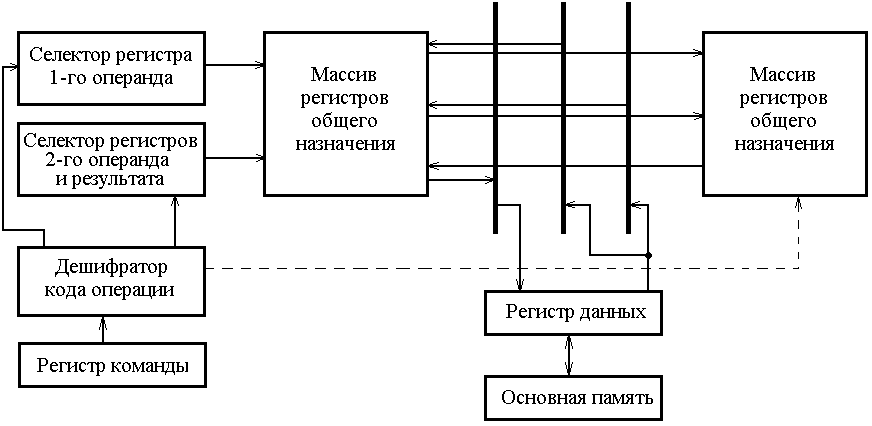

Состав и информационные тракты вычислительной машины с выделенным доступом к памяти показаны на рис. 2.52.

Рис. 2.52. Архитектура вычислительной машины с выделенным доступом

к памяти

Архитектура с выделенным доступом к памяти характерна для всех вычислительных машин с RISC-архитектурой. Команды в таких вычислительных машин, как правило, имеют длину 32 бита и трехадресный формат. В качестве примеров вычислительных машин с выделенным доступом к памяти можно отметить HP PA-RISC, IBM RS/6000, SPARC, MIPS R4000, DEC Alpha и т. д. К достоинствам архитектуры следует отнести простоту декодирования и исполнения команды.

2.16. Типы команд

Для описания основных типов операций примем следующую классификацию:

• команды пересылки данных;

• команды арифметической и логической обработки;

• команды работы со строками;

• команды SIMD;

• команды преобразования;

• команды ввода/вывода;

• команды управления потоком команд.

2.16.1. Команды пересылки данных

Это наиболее распространенный тип машинных команд. В таких командах должна содержаться следующая информация:

• адреса источника и получателя операндов – адреса ячеек памяти, номера регистров процессора или информация о том, что операнды расположены в стеке;

• длина подлежащих пересылке данных (обычно в байтах или словах), заданная явно или косвенно;

• способ адресации каждого из операндов, с помощью которого содержимое адресной части команды может быть пересчитано в физический адрес операнда.

Эта группа команд обеспечивает передачу информации между процессором и основной памятью, внутри процессора и между ячейками памяти. Пересылочные операции внутри процессора имеют тип «регистр-регистр». Передачи между процессором и памятью относятся к типу «регистр-память», а пересылки в памяти – к типу «память-память».

2.16.2. Команды арифметической и логической обработки

В данную группу входят команды, обеспечивающие арифметическую и логическую обработку информации в различных формах ее представления. Для каждой формы представления чисел в архитектуре системы команд обычно предусматривается некий стандартный набор операций.

Помимо вычисления результата выполнение арифметических и логических операций сопровождается формированием в АЛУ признаков (флагов), характеризующих этот результат. Наиболее часто фиксируются такие признаки, как: Z (Zero) – нулевой результат; N (Negative) – отрицательный результат; V (oVerflow) – переполнение разрядной сетки; С (Carry) – наличие переноса.