- •Раздел 2 принципы построения и функционирования эвм и вычислительных систем (вс)

- •2.1. Структура эвм

- •2.2. Системы счисления

- •2.3. Формы представления чисел

- •2.3.1. Форма представления чисел с фиксированной точкой

- •2.3.2. Форма представления чисел с плавающей точкой

- •2.3.3. Форматы двоично-десятичных чисел

- •2.3. Машинные коды

- •2.3.1. Прямой код

- •2.3.2. Обратный код

- •2.3.3. Дополнительный код

- •2.4. Перевод чисел из одной системы представления в другую

- •2.4.1. Перевод между основаниями, составляющими степень двойки

- •2.4.2. Перевод целого числа из десятичного счисления в другое

- •2.4.3. Перевод дробного числа из десятичного счисления в другое

- •2.4.4. Перевод чисел в десятичную систему счисления

- •2.5. Арифметические действия над двоичными числами

- •2.5.1. Сложение

- •2.5.2. Вычитание

- •2.5.3. Умножение

- •2.5.4. Деление

- •2.6. Понятие алгебры логики

- •2.7. Простейшие логические функции

- •2.7.1. Логическая операция конъюнкция (логическое умножение)

- •2.7.2. Логическая операция дизъюнкция (логическое сложение)

- •2.7.3. Логическая операция инверсия (отрицание)

- •2.7.4. Логическая операция сложение по модулю 2

- •2.7.5. Логическая операция эквивалентность (функция тождества)

- •2.7.6. Логическая операция импликация (логическое следование)

- •2.7.7. Функция Шеффера

- •2.7.8. Стрелка Пирса ав, или функция Вебба a b

- •2.8. Основные правила преобразования формул

- •2.9. Кодирование текстовой информации

- •2.10. Составные части компьютера

- •2.11. Логические элементы

- •2.12. Триггеры

- •2.12.1. Общие сведения о триггерах

- •2.12.2. Асинхронный rs-триггер

- •2.12.3. Синхронный rs-триггер

- •2.12.3. Двухтактный rs-триггер

- •2.12.4. Асинхронный и синхронный d-триггеры

- •2.12.5. T-триггер

- •2.12.6. Jk-триггер

- •2.13. Типовые узлы комбинационного типа

- •2.13.1. Дешифраторы

- •2.13.2. Одноразрядный сумматор

- •2.13.3. Полусумматор

- •2.13.4. Многоразрядные сумматоры

- •2.13.5. Двоично-десятичные сумматоры

- •2.13.6. Мультиплексоры

- •2.13.7. Демультиплексоры

- •2.14. Типовые узлы накапливающего типа

- •2.14.1. Регистры

- •2.14.2. Счетчики

- •2.14.3. Двоично-десятичные счетчики

- •2.15. Классификация архитектур системы команд

- •2.15.1. Классификация по составу и сложности команд

- •2.15.2. Классификация по месту хранения операндов

- •2.15.3. Стековая архитектура

- •2.15.4. Аккумуляторная архитектура

- •2.15.5. Регистровая архитектура

- •2.15.6. Архитектура с выделенным доступом к памяти

- •2.16. Типы команд

- •2.16.1. Команды пересылки данных

- •2.16.2. Команды арифметической и логической обработки

- •2.16.3. Операции с целыми числами

- •2.16.4. Операции с числами в форме с плавающей запятой

- •2.16.5. Логические операции

- •2.16.6. Операции сдвигов

- •2.16.7. Операции с десятичными числами

- •2.16.8. Simd-команды

- •2.16.9. Команды для работы со строками

- •2.16.10. Команды преобразования

- •2.16.11. Команды ввода/вывода

- •2.16.12. Команды управления системой

- •2.16.13. Команды управления потоком команд

- •2.17. Формат команд

- •2.17.1. Длина команды

- •2.17.2. Разрядность полей команды

- •2.17.3. Выбор адресности команд

- •2.18. Способы адресации операндов

- •2.18.1. Непосредственная адресация

- •2.18.2. Прямая адресация

- •2.18.3. Косвенная адресация

- •2.18.4. Регистровая адресация

- •2.18.5. Косвенная регистровая адресация

- •2.18.6. Адресация со смещением

- •2.18.7. Относительная адресация

- •2.18.8. Базовая регистровая адресация

- •2.18.9. Индексная адресация

- •2.18.10. Страничная адресация

- •2.18.11. Блочная адресация

- •2.18.12. Распространенность различных видов адресации

- •2.19. Способы адресации в командах управления потоком команд

- •2.20. Функциональная организация фон-неймановской вычислительной машины

- •2.20.1. Устройство управления

- •2.20.2. Арифметико-логическое устройство

- •2.20.3. Основная память

- •2.20.4. Модуль ввода/вывода

- •2.21. Цикл команды

- •2.21.1. Стандартный цикл команды

- •2.21.2. Описание стандартных циклов команды для гипотетической машины

- •2.21.3. Машинный цикл с косвенной адресацией

2.18.1. Непосредственная адресация

При непосредственной адресации (НА) в адресном поле команды вместо адреса содержится непосредственно сам операнд (рис. 2.62). Этот способ может применяться при выполнении арифметических операций, операций сравнения, а также для загрузки констант в регистры.

Код операции |

Способ адресации |

Непосредственный операнд |

Рис. 2.62. Непосредственная адресация

Когда операндом является число, оно обычно представляется в дополнительном коде. При записи в регистр, имеющий разрядность, превышающую длину непосредственного операнда, операнд размещается в младшей части регистра, а оставшиеся свободными позиции заполняются значением знакового бита операнда.

Помимо того, что в адресном поле могут быть указаны только константы, еще одним недостатком данного способа адресации является то, что размер непосредственного операнда ограничен длиной адресного поля команды, которое в большинстве случаев меньше длины машинного слова.

В 50-60% команд с непосредственной адресацией длина операнда не превышает 8 бит, а в 75-80% – 16 бит. Таким образом, в подавляющем числе случаев шестнадцати разрядов вполне достаточно, хотя для вычисления адресов могут потребоваться и более длинные константы.

Наиболее интенсивно данный вид адресации используется в арифметических операциях и командах сравнения. В то же время загрузка констант в большинстве программ, очевидно, не такая частая операция.

Непосредственная адресация сокращает

время выполнения команды, так как не

требуется обращение к памяти за операндом.

Кроме того, экономится память, поскольку

отпадает необходимость в ячейке для

хранения операнда. В плане эффективности

этот способ можно считать «идеальным»

,

и его можно рекомендовать к использованию

во всех ситуациях, когда тому не

препятствуют вышеупомянутые ограничения.

,

и его можно рекомендовать к использованию

во всех ситуациях, когда тому не

препятствуют вышеупомянутые ограничения.

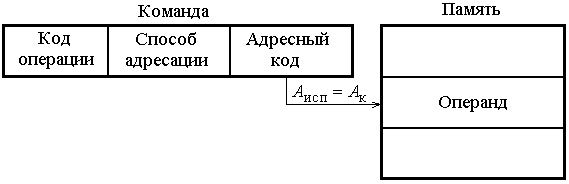

2.18.2. Прямая адресация

При прямой или абсолютной адресации (ПА) адресный код прямо указывает номер ячейки памяти, к которой производится обращение (рис. 2.63), то есть адресный код совпадает с исполнительным адресом.

Рис. 2.63. Прямая адресация

При всей простоте использования способ имеет существенный недостаток – ограниченный размер адресного пространства, так как для адресации к памяти большой емкости нужно «длинное» адресное поле. Однако более существенным несовершенством можно считать то, что адрес, указанный в команде, не может быть изменен в процессе вычислений. Это ограничивает возможности по произвольному размещению программы в памяти.

Прямую адресацию характеризуют следующие

показатели эффективности:

,

,

- где

– количество адресуемых операндов.

- где

– количество адресуемых операндов.

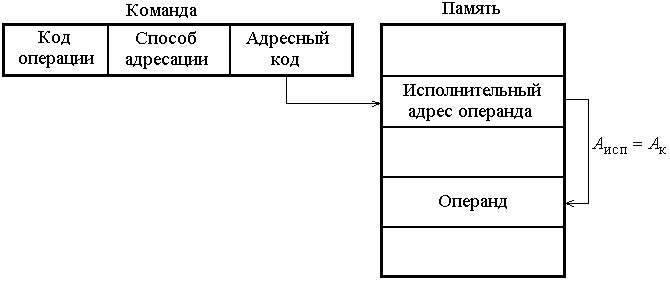

2.18.3. Косвенная адресация

Одним из путей

преодоления проблем, свойственных

прямой адресации, может служить прием,

когда с помощью ограниченного адресного

поля команды указывается адрес ячейки,

в свою очередь, содержащей полноразрядный

адрес операнда (рис. 2.64). Этот способ

известен как косвенная

адресация

(КА). Запись ( )

означаетчает содержимое ячейки, адрес

которой указан в скобках.

)

означаетчает содержимое ячейки, адрес

которой указан в скобках.

При косвенной адресации содержимое адресного поля команды остается неизменным, в то время как косвенный адрес в процессе выполнения программы можно изменять. Это позволяет проводить вычисления, когда адреса операндов заранее неизвестны и появляются лишь в процессе решения задачи. Дополнительно такой прием упрощает обработку массивов и списков, а также передачу параметров подпрограмм.

Недостатком косвенной адресации

является необходимость в двукратном

обращении к памяти: сначала для извлечения

адреса операнда, а затем для обращения

к операнду ( ).

Сверх того задействуется лишняя ячейка

памяти для хранения исполнительного

адреса операнда. Способу свойственны

следующие затраты оборудования:

).

Сверх того задействуется лишняя ячейка

памяти для хранения исполнительного

адреса операнда. Способу свойственны

следующие затраты оборудования:

, (2.15)

, (2.15)

где

– разрядность

ячейки памяти, хранящей исполнительный

адрес;

–

количество ячеек для хранения

исполнительных адресов;

– количество адресуемых операндов.

Здесь выражение

– разрядность

ячейки памяти, хранящей исполнительный

адрес;

–

количество ячеек для хранения

исполнительных адресов;

– количество адресуемых операндов.

Здесь выражение

определяет разрядность сокращенного

адресного поля команды (обычно

определяет разрядность сокращенного

адресного поля команды (обычно

).

).

Рис. 2.64. Косвенная адресация

В качестве варианта

косвенной адресации, правда, достаточно

редко используемого, можно упомянуть

многоуровневую

или каскадную

косвенную адресацию:

,

когда к исполнительному адресу цепочка

косвенных адресов. В этом случае один

из битов в каждом адресе служит признаком

косвенной адресации. Состояние бита

указывает, является ли содержимое ячейки

очередным адресом в цепочке адресов

или это уже исполнительный адрес

операнда. Особых преимуществ у такого

подхода нет, но в некоторых специфических

ситуациях он оказывается весьма удобным,

например, при обработке многомерных

массивов. В то же время очевиден и его

недостаток – для доступа к операнду

требуется три и более обращений к памяти.

,

когда к исполнительному адресу цепочка

косвенных адресов. В этом случае один

из битов в каждом адресе служит признаком

косвенной адресации. Состояние бита

указывает, является ли содержимое ячейки

очередным адресом в цепочке адресов

или это уже исполнительный адрес

операнда. Особых преимуществ у такого

подхода нет, но в некоторых специфических

ситуациях он оказывается весьма удобным,

например, при обработке многомерных

массивов. В то же время очевиден и его

недостаток – для доступа к операнду

требуется три и более обращений к памяти.