- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

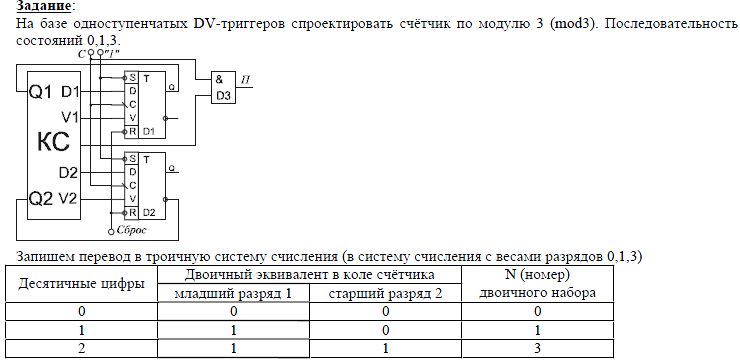

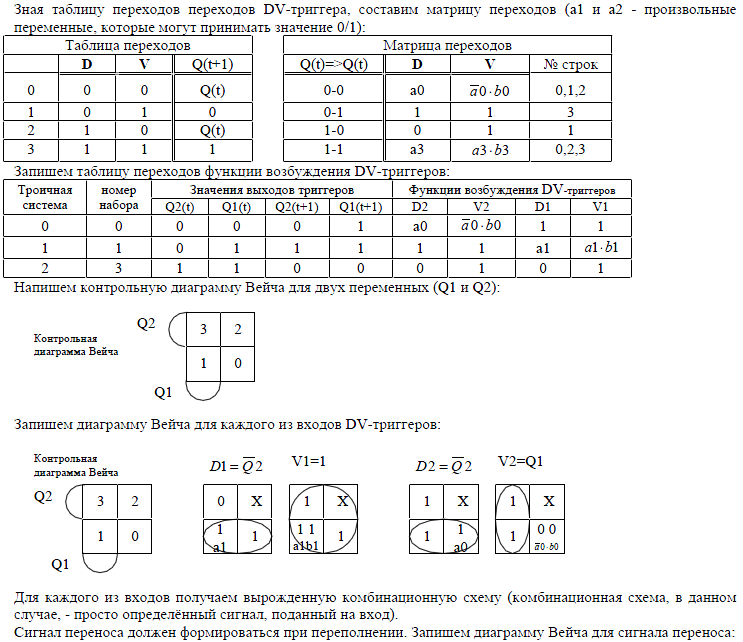

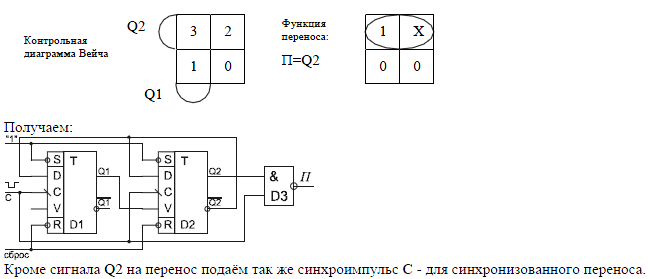

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

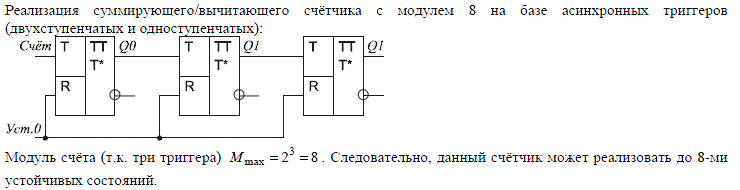

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

Модуль счёта (М) - число устойчивых состояний счётчика.

Например, счётчик по модулю 10 имеет 10 устойчивых состояний; счётчик по модулю 3 - три устойчивых состояния.

В основе счётчика - линейка триггеров, связанных схемой управления и логическими связями (запрещают/разрешают прохождение импульса):

Для 4-х триггеров - максимальный модуль счёта определяется как два в степени числа триггеров: 24 16

Mmax . Минимальный модуль счёта - два в первой степени - т.е. 2: 21 2

Mmin . То есть для 4-х триггеров модуль счёта лежит в пределах от 2 до 16-ти: 2 ≤M ≤16 . Например, при организации счётчика модуль счёта может быть М=10. В синхронных счётчиках триггеры, входящие в счётчик, переключаются по общему синхроимпульсу - т.е. почти одновременно. Для асинхронных счётчиков срабатывание триггеров не одновременное.

Изменение коэффициента пересчета

Самый простой способ изменить модуль счетчика — увеличить его разрядность путем каскадирования его с другим счетчиком или отключить некоторые разряды усложнив функции формирования сброса счетчика, переноса и заема.

25.Проектирование счетчика с заданным набором состояний на rs триггерах.

27.Проектирование счетчика с заданным набором состояний на jk триггерах.

Счётчиком называют последовательную схему, предназначенную для увеличения/уменьшения хранимого кода на единицу или заданную константу.

Модуль счёта (М) - число устойчивых состояний счётчика

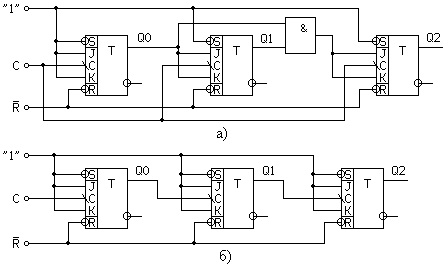

Счётчики могут быть: а) Синхронными б) асинхронными:

В синхронных схемах все изменения

согласуются по времени с подачей

считаемого сигнала на общую шину,

объединяющую синхронизирующие входы

С

триггеров счетчика (рис. а).

синхронных схемах все изменения

согласуются по времени с подачей

считаемого сигнала на общую шину,

объединяющую синхронизирующие входы

С

триггеров счетчика (рис. а).

В асинхронном счетчике отсутствует общая шина, на которую поступает считаемый сигнал. На вход С триггеров асинхронного счетчика сигналы могут поступать как с выхода другого триггера, так и от схем, непосредственно не связанных с синхронизирующими импульсами (рис. б).

Для проектирования синхронных счётчиков используют стандартные методы. Для асинхронных счётчиков удобных систематизированных методов нет, из-за различий во внутреннем строении триггеров проявляющихся при асинхронной работе. По этому при разработке надо иметь чёткое представление о внутреннем строении триггера и не ограничиваться таблицей переходов, которая описывает только синхронную работу триггера.

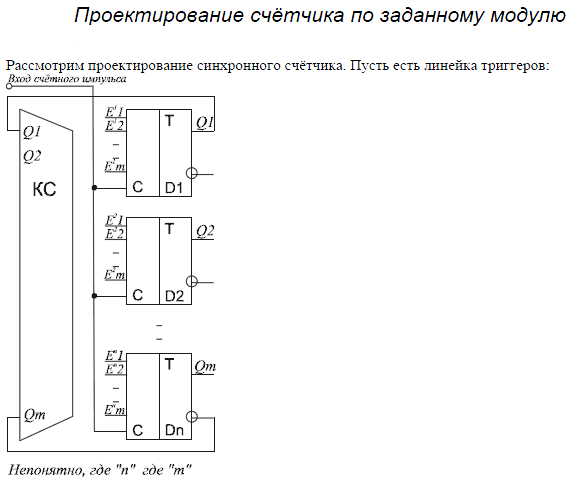

Сигналы с выходов триггеров поступают на вход комбинационной схемы, которая преобразует поступившую информацию. С выходов комбинационной схемы сигналы подаются на логические входы триггеров. Преобразованная информация не воспринимается триггером до тех пор, пака на синхронизирующие входы триггеров не поступит считываемый сигнал. Информация находящаяся на входах каждого триггера, сформирована комбинационной схемой так , что бы по приходу очередного считываемого сигнала счётчик перешёл из текущего состояния в следующее

Функции возбуждения входов i-го триггера:

E1(t) = f1[Q1(t), Q2(t), ... ,Qn(t)] ,

E2(t) = f2[Q1(t), Q2(t), ... ,Qn(t)] .

Функции возбуждения являются переключательными функциями, которым соответствуют комбинационные схемы.

Задача синтеза счётчика собранного на определённом типе триггеров заключается в составлении функций возбуждения в заданном базисе.

При синтезе синхронных схем используются матрицы переходов триггеров. Матрица переходов составляется исходя из таблицы переходов данного триггера.

Далее составляются таблица переходов функций возбуждения.

Проводим минимизацию функций возбуждения триггеров.

Находим функцию переноса для возможности каскадирования счётчиков. Например, счётчик по модулю 10 имеет 10 устойчивых состояний; счётчик по модулю 3 - три устойчивых состояния.

Пример:

Пусть необходимо на базе одноступенчатых RS(JK)-триггеров спроектировать двухразрядный двоично-десятичный счётчик c заданным набором состояний.

Необходимо сделать перевод в соответствующую систему счисления (двоичную, троичную). В данной системе кодирования каждая десятичная цифра представляется четырехразрядным двоичным эквивалентом.

Представление двоично-десятичного кода

Десятичные |

Двоичный эквивалент в коде 2421 |

Номера двоичных |

|||

цифры |

2 |

4 |

2 |

1 |

наборов |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

2 |

0 |

0 |

1 |

0 |

2 |

3 |

0 |

0 |

1 |

1 |

3 |

4 |

0 |

1 |

0 |

0 |

4 |

5 |

1 |

0 |

1 |

1 |

11 |

6 |

1 |

1 |

0 |

0 |

12 |

7 |

1 |

1 |

0 |

1 |

13 |

8 |

1 |

1 |

1 |

0 |

14 |

9 |

1 |

1 |

1 |

1 |

15 |