- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

Триггер - основа функциональных узлов последовательного типа

Триггером называется устройство с двумя устойчивыми состояниями. Триггеры представляют собой простейшие последовательностные устройства и широко используются в электронных устройствах различного назначения как в виде самостоятельных узлов, так и в качестве элементов для построения более сложных цифровых устройств (счетчиков, регистров, запоминающих устройств).

Асинхронный триггер – триггер, состояние которого определяется в каждый момент времени состоянием входов, т.е изменения входного сигнала непосредственно передаются на выход триггера

С

&

&

&

&

С

С

инхронный

RS

–триггер

инхронный

RS

–триггер

О дноступенчатый

синхронный триггер.

дноступенчатый

синхронный триггер.

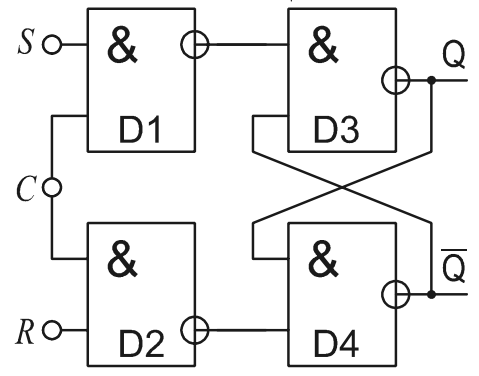

Одноступенчатый синхронный RS триггер состоит из 2 частей – комбинационной схемы и запоминающей ячейки. КС представлена элементами D1 и D2, запоминающая ячейка (в дальнейшем ЗЯ) элментами D3 и D4.

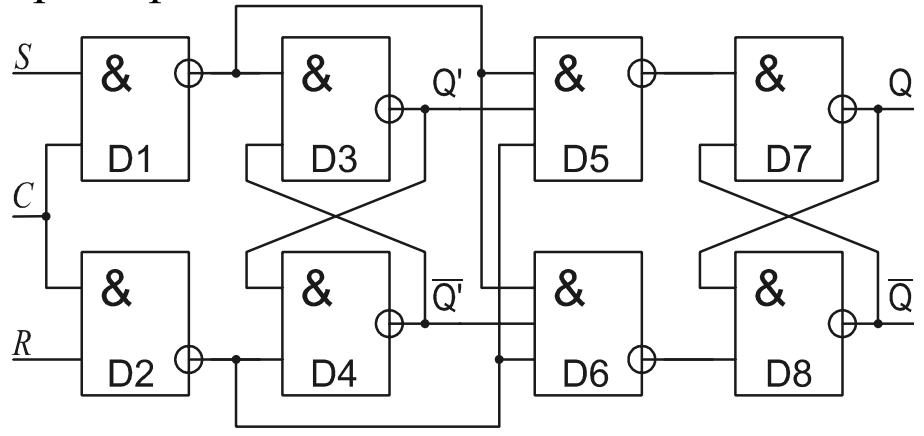

Двухступенчатые синхронный триггер.

Двухступенчатые синхронные триггеры обозначаются «ТТ» . Это триггеры типа «Master-Slave» или MS-триггеры.

При С=0 прием входной информации в первую ступень закрыт, а поскольку на синхронизирующий вход второй ступени благодаря инвертору поступает 1, то приём информации во вторую ступень открыт. Вторая ступень принимает информацию, хранимую в первой ступени триггера.

При С=1 первая ступень открыта, а вторая закрыта. Информация, находящаяся на логических входах двухступенчатого триггера принимается в первую ступень.

Двухступенчатые триггер.

Д вухступенчатые

синхронные триггеры обозначаются «ТТ»

. Это триггеры типа «Master-Slave»

или MS-триггеры.

вухступенчатые

синхронные триггеры обозначаются «ТТ»

. Это триггеры типа «Master-Slave»

или MS-триггеры.

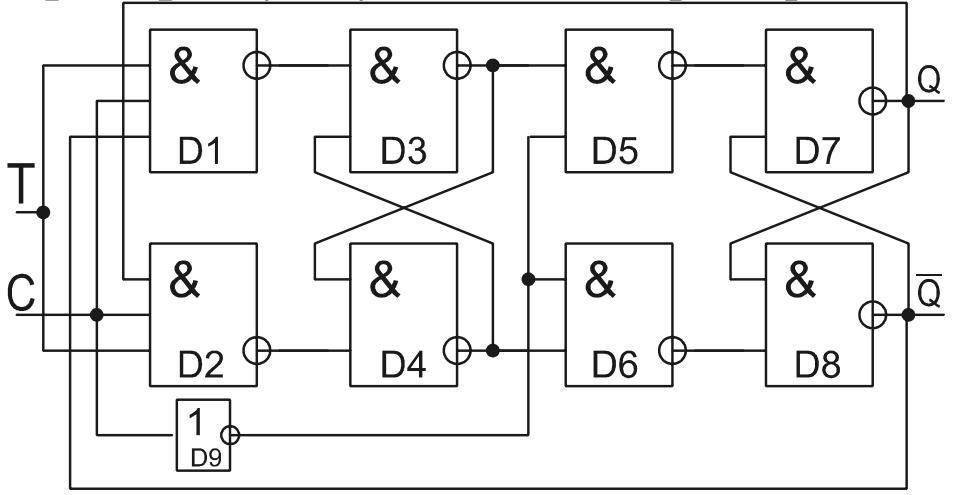

Пример: двухступенчатый Т-триггер.

Достоинством двухступенчатого триггера является то что нет ограничения сверх на длительность импульса (как в одноступенчатых триггерах)

Недостаток: то что он более медленный чем одноступенчатый.

Для улучшения временных характеристик двухступенчатые триггеры делают с динамическим управлением, т.е. такие триггеры работают по перепаду сигнала С (синхроимпульс).

17. Схемы триггеров со статическим и динамическим управлением.

Входная информация в рассматриваемых триггерах принимается только тогда, когда значение СИ соответствует единице, т.е. в течение всей длительности СИ. Это означает, что при С = 1 переключения сигналов на логических входах вызывает изменение состояния триггера, т.е. выхода Q. Поэтому информацию на логических входах триггера, как правило, меняют при С = 0.

RS-триггер

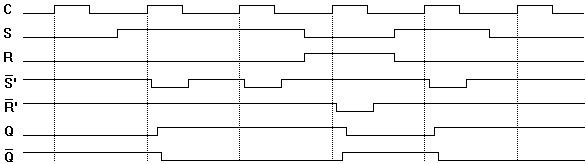

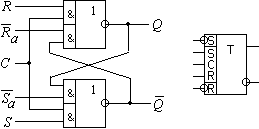

Синхронный RS-триггер со статическим управлением записью реализуется подключением двух элементов И-НЕ к ЗЯ (рис. 3.3). Смена сигналов на логических входах R и S разрешена между СИ. Временная диаграмма работы этого триггера приведена на рис. 3.4.

Рис. 3.3. Синхронный RS-триггер со статическим управлением записью, его условное графическое обозначение и таблица переходов

Рис.3.4. Временная диаграмма работы синхронного RS-триггера со статическим управлением записью

Схема синхронного RS-триггера

с дополнительными инверсными асинхронными

входами

![]() и

и

![]() (входами предварительной установки

триггера в 0 или 1) на элементах 2-2И-2ИЛИ-НЕ

показана на рис. 3.5.

(входами предварительной установки

триггера в 0 или 1) на элементах 2-2И-2ИЛИ-НЕ

показана на рис. 3.5.

Рис.

3.5. Синхронный RS-триггер

со статическим управлением записью и

асинхронными входами

![]() и

и

![]() и его условное графическое обозначение

и его условное графическое обозначение

D-триггер

На практике наибольшее распространение получила схема синхронного D-триггера со статическим управлением записью. D-триггер имеет один логический вход D (Delay - задержка), состояние которого с каждым СИ передается на выход, т.е. выходные сигналы представляют собой задержанные входные сигналы. Схему D-триггера можно получить из RS-триггера, если на вход R подать инвертированный сигнал входа S. Однако целесообразно использовать для инвертирования уже имеющиеся элементы (рис. 3.6).

Рис. 3.6. Синхронный D-триггер со статическим управлением записью (пунктиром показан вход V для DV-триггера):

а) логическая схема; б) условное графическое обозначение D-триггера и его таблица переходов; в) условное графическое обозначение DV-триггера и его таблица переходов

DV-триггер

Если к D-триггеру добавить еще один вход V (Vorentscheidung - предварительное разрешение) для блокирования СИ (пунктирная линия на рис 3.6), то получим синхронный DV-триггер со статическим управлением записью. Легко заметить, что входы С и V можно поменять местами без нарушения логики работы триггера.