- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

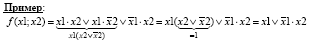

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

Задача анализа состоит в написании системы функций, отражающей логику работы схемы. Эта задача имеет однозначное решение.

Задача синтеза (обратная анализу) состоит в построении реальной схемы на основе заданных законов её функционирования. Синтез не имеет однозначного решения.

При синтезе схемы нужно получить минимальное число элементов в заданном базисе.

Задача синтеза произвольного устройства сводится к математической задачи построения произвольной функции алгебры-логики.

Какое количество связок необходимо, чтобы построить произвольную функцию алгебры-логики? Ответ на этот вопрос однозначен.

Совокупность элементов алгебры-логики называется базисом.

Наиболее распространённый базис - дизъюнкция, конъюнкция, отрицание. Базисы могут быть одноэлементными, например, одноэлементные: базисы стрелка Пирса (базис "И-НЕ") и штрих Шеффера (базис "ИЛИ-НЕ").

Технический синтез устройств (?) - некоторый набор элементов, реализующих функции алгебры-логики, и образующих базис.

Задача синтеза устройства должна быть дополнена задачей уменьшения оборудования в нём (задача минимизации). Устройство, которое реализует соответствующую функцию, используя меньше оборудования, будет работать надёжнее (?). С математической точки зрения - это задача построения минимальной функции алгебры-логики.

Под минимальной функцией алгебры-логики понимается такая форма, в которой содержится меньшее количество букв и членов по сравнению с исходной формой. Речь идёт именно о буквах, а не о количестве переменных.

Замечание:

Если какое-либо элементарное произведение входит в функцию, то при добавлении к нему новых сомножителей, полученное произведение так же будет входить в функцию (т.е. в функцию можно ввести любое число аргументов).

СИНТЕЗ НЕ ПОЛНОСТЬЮ ЗАДАННЫХ ЛОГИЧЕСКИХ ФУНКЦИЙ

По условиям работы логического устройства некоторые наборы значений аргументов могут оказаться запрещенными для данного устройства и никогда не появится на его входах. В этом случае функция задана не на всех наборах аргументов. Такие функции будем называть не полностью заданными.

При синтезе логического устройства, реализующего не полностью заданную функцию, допустимо задавать произвольными значениями функции на запрещенных наборах аргументов. При этом в зависимости от способа задания этих функций минимальная форма может оказаться простой или более сложной. Таким образом, возникает проблема целесообразного доопределения функции на запрещенных наборах аргументов.

Обозначается запрещенный набор: Х

Может быть использован следующий способ получения минимальной формы не полностью заданной функции f:

а) записывается СДНФ (СКНФ) функции f0, полученное их f заданием значения 0 (значения 1 в случае СКНФ) на всех запрещенных наборах аргументов;

б) записывается СДНФ (СКНФ) функции f1, полученной из f заданием значения 1 (значения 0 в случае СКНФ) на всех запрещенных наборах аргументов;

в) функция f1 приводится к сокращенной форме (к форме, содержащей все простые импликанты);

г) Составляется импликантная таблица из всех членов функции f0 и простых импликант функции f1;

д) искомая минимальная форма составляется из простых импликант функции f1, поглащающих все члены СДНФ (СКНФ) функции f0.

е) Производится проверка доопределённой функции на её соответствие исходному набору, т.к. при проектировании и минимизации мы работаем не с исходной функцией, то в процессе преобразования могут возникнуть ошибки, наличие/отсутствие которых и определяется построением таблицы истинности полученной ФАЛ