- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

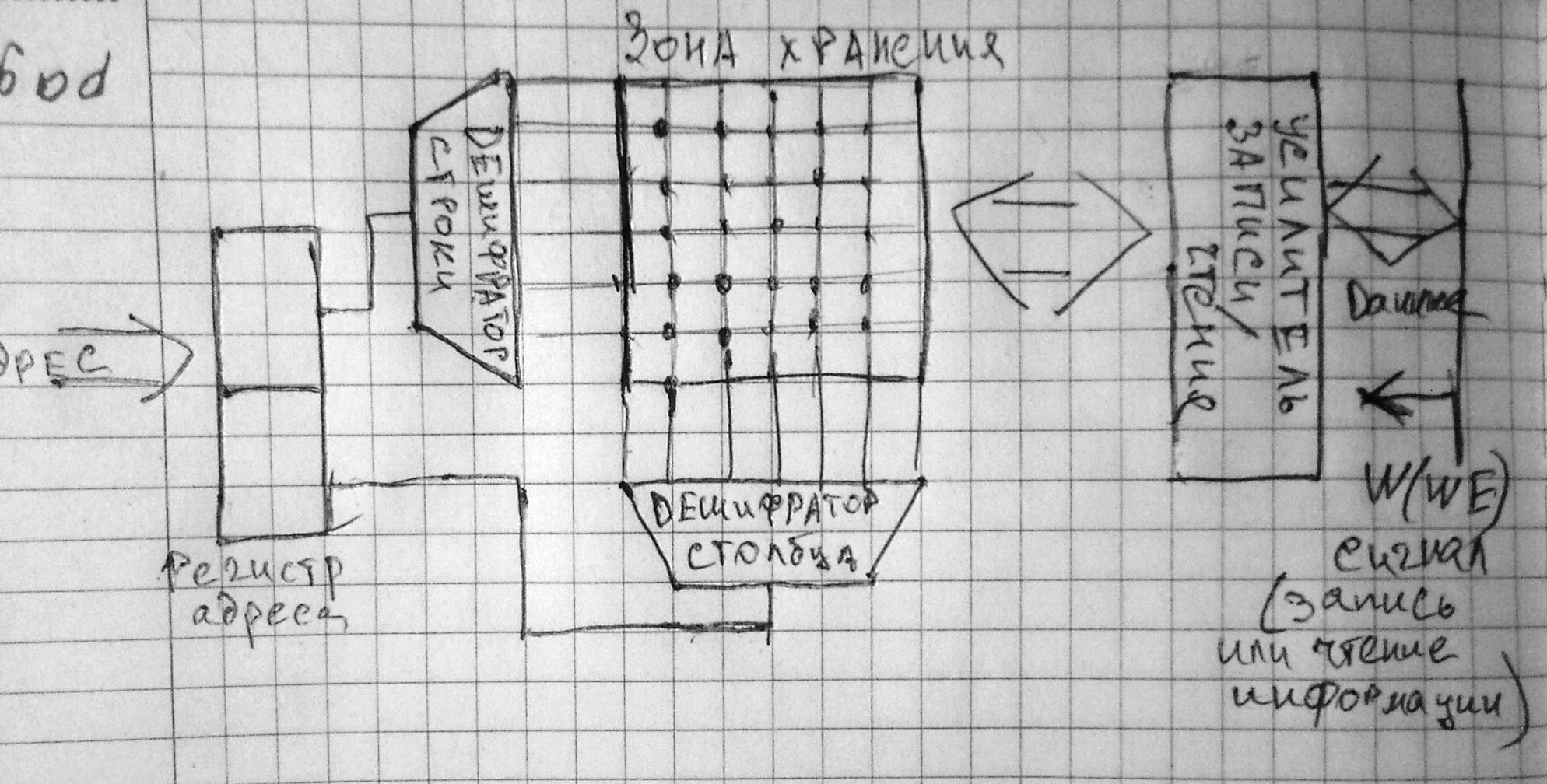

30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

Ячейки памяти составляют двумерный массив, т.е. матрицу и те из них, что находятся на одной строке условно называются строкой, а те, что друг под другом - условно столбцом и образуют зону хранения.

Функция выборки обеспечивается дешифраторами.

Усилители записи/чтения необходимы для преобразования уровня сигнала в понятный для других устройств вид.

Регистр адреса содержит адрес ячейки к которой нужно получить доступ, при этом часть регистра – это адрес строки а вторая часть – адрес столбца.

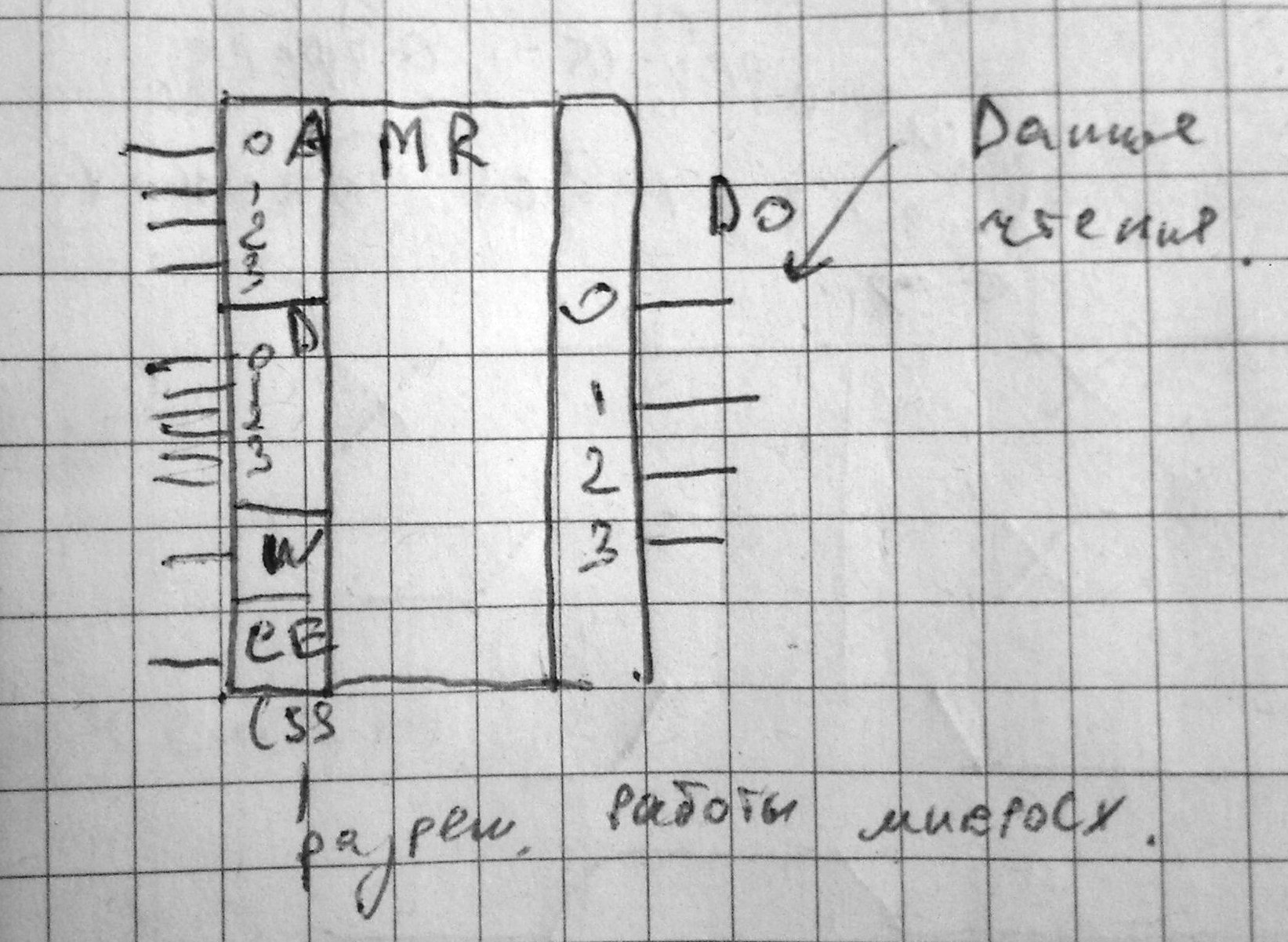

Уго микросхемы памяти.

Разрядность памяти – разрядность ячейки памяти, т.е. разрядность минимальной адресуемой единицы памяти..

Слово памяти – адресуемая единица.

Количество слов = 2^n входов.

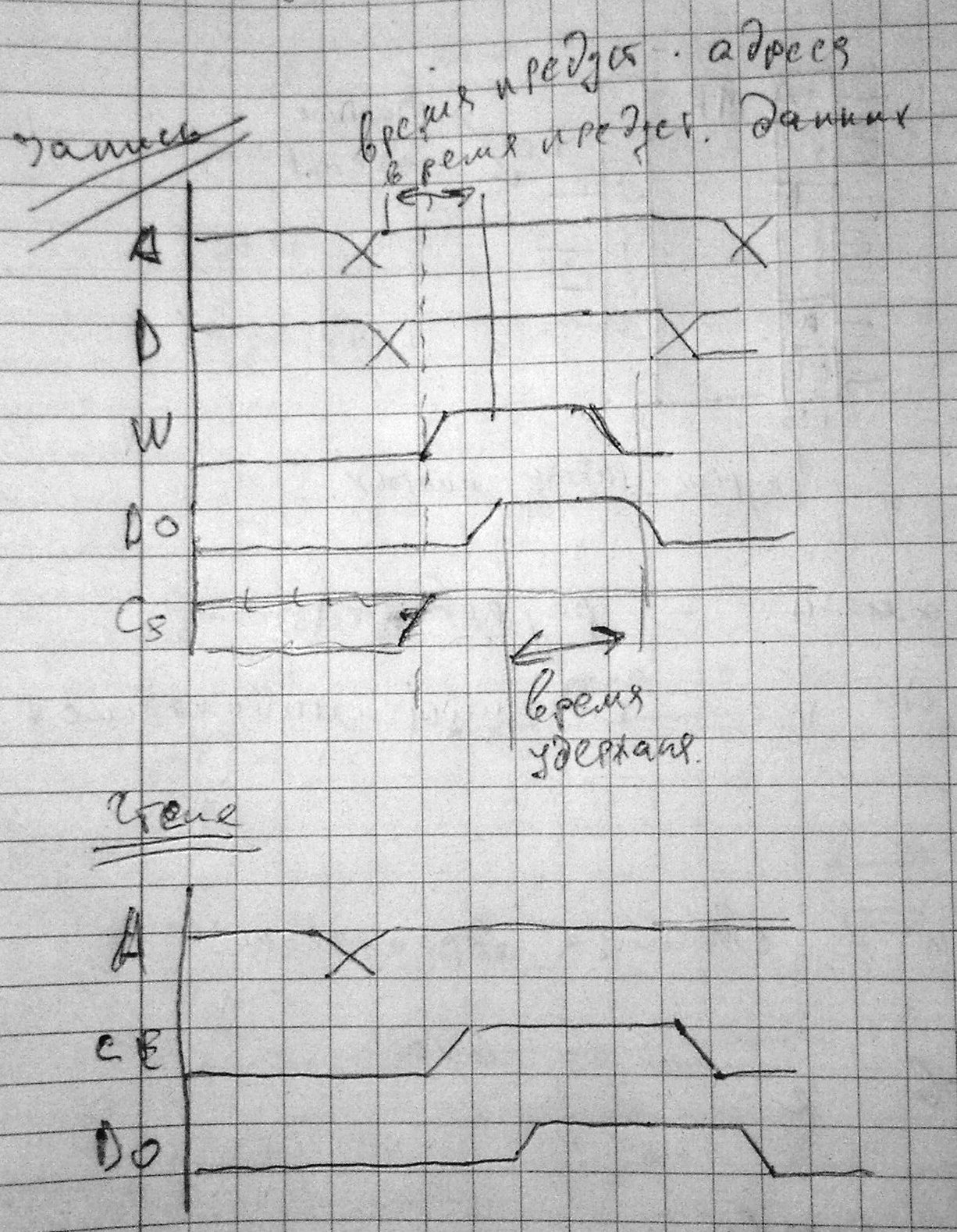

Цикл чтения/записи ПП запоминающего ус-ва.

Память имеет 3 режима работы: запись чтение и хранение.

Временные диаграмы чтения записи:

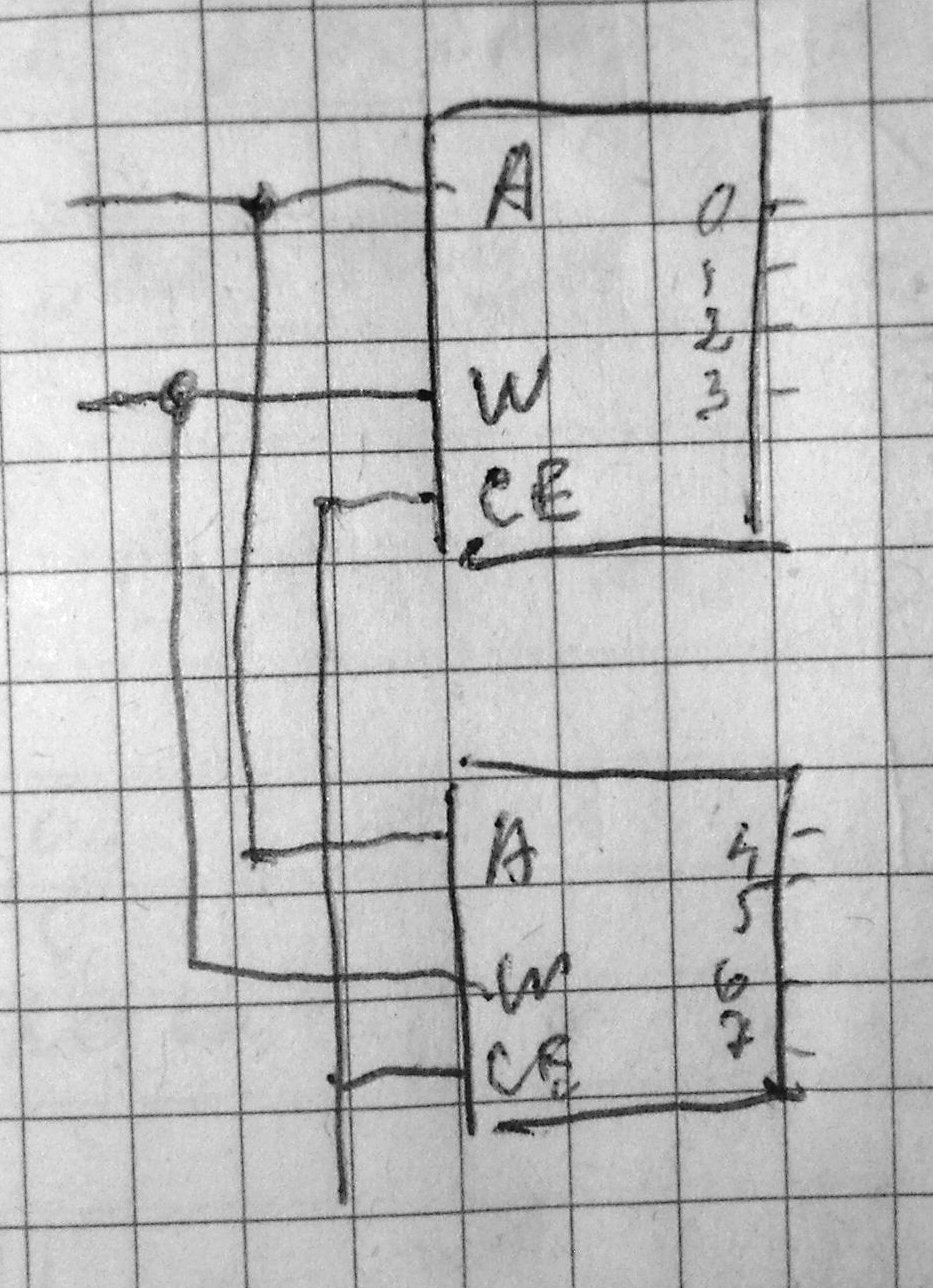

Для построения ЗУ произвольной емкости применяют:

- Увеличение разрядности микросхем

- Увеличение адресности ЗУ

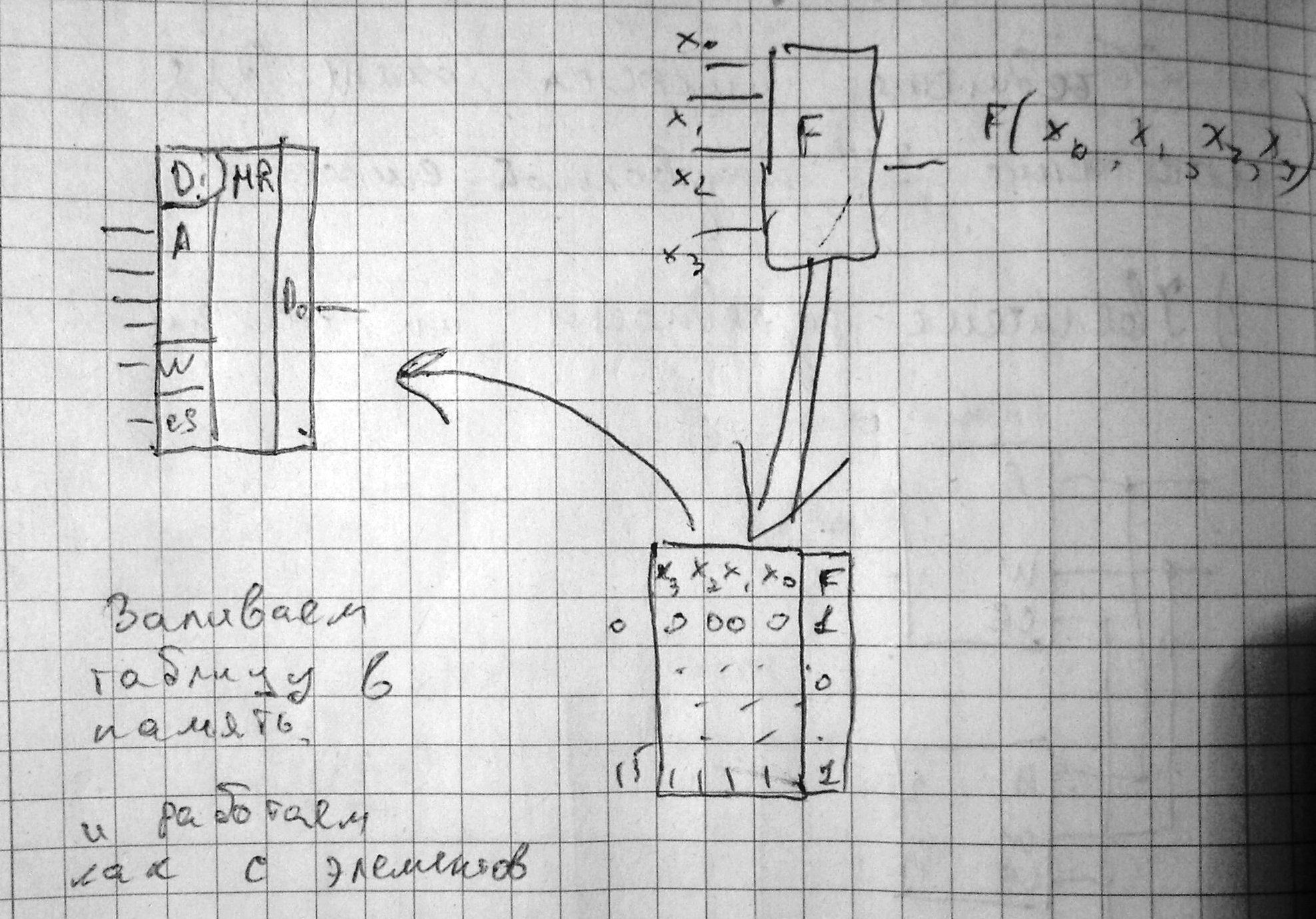

32.Реализация фал на микросхемах памяти.

Функции алгебры логики можно также реализовать с помощью ячеек памяти. Для этого мы создаем таблицу истиности для нашей функции и записываем ее в память, после чего просто работаем с этим элементом.

= F(x0,x1,x2,x3)

F(x0,x1,x2,x3)

Таким образом получается свойство, что с помощью одной микросхемы можно реализовать 2^n логических схем.

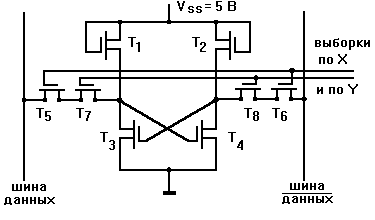

33.Запоминающая ячейка статического типа, устройство и принцип работы.

Элементарной ячейкой статического ОЗУ с произвольной выборкой является триггер на транзисторах Т1-Т4 (рис. 3.7) с ключами Т5-Т8 для доступа к шине данных. Причем Т1-Т2 - это нагрузки, а Т3-Т4 - нормально закрытые элементы.

Рис. 4.7. Ячейка статического ОЗУ.

Сопротивление элементов Т1-Т2 легко регулируется в процессе изготовления транзистора путем подгонки порогового напряжения при легировании поликремниевого затвора методом ионной имплантации. Количество транзисторов (6 или 8) на ячейку зависит от логической организации памяти микропроцессорной системы.

Статические ОЗУ требуют для своего построения большой площади кристалла, поэтому их ёмкость относительно невелика. Статические ОЗУ применяются для построения микроконтроллерных схем из-за простоты построения принципиальной схемы и возможности работать на сколь угодно низких частотах, вплоть до постоянного тока. Кроме того статические ОЗУ применяются для построения КЭШ-памяти в универсальных компьютерах из-за высокого быстродействия статического ОЗУ.

34. Запоминающая ячейка динамического типа, устройство и принцип работы.

Запоминающая ячейка Динамического типа.

Cn – бумажного типа и находится в транзисторе.

Конденсатора на самом деле нет.

Это паразитная емкость, возникшая из параллельной емкости транзистора.

Полевой транзистор может хранить заряд емкости.

Значение хранится некоторое время и требует периодического восстановления информации - регенерация.

Обычно ячейки памяти динамического типа объединяют динамическую матрицу,

Что при любом обращении ячейки, находящейся в строке, выполняется цикл регенерации для всех ячеек в этой строке.