- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

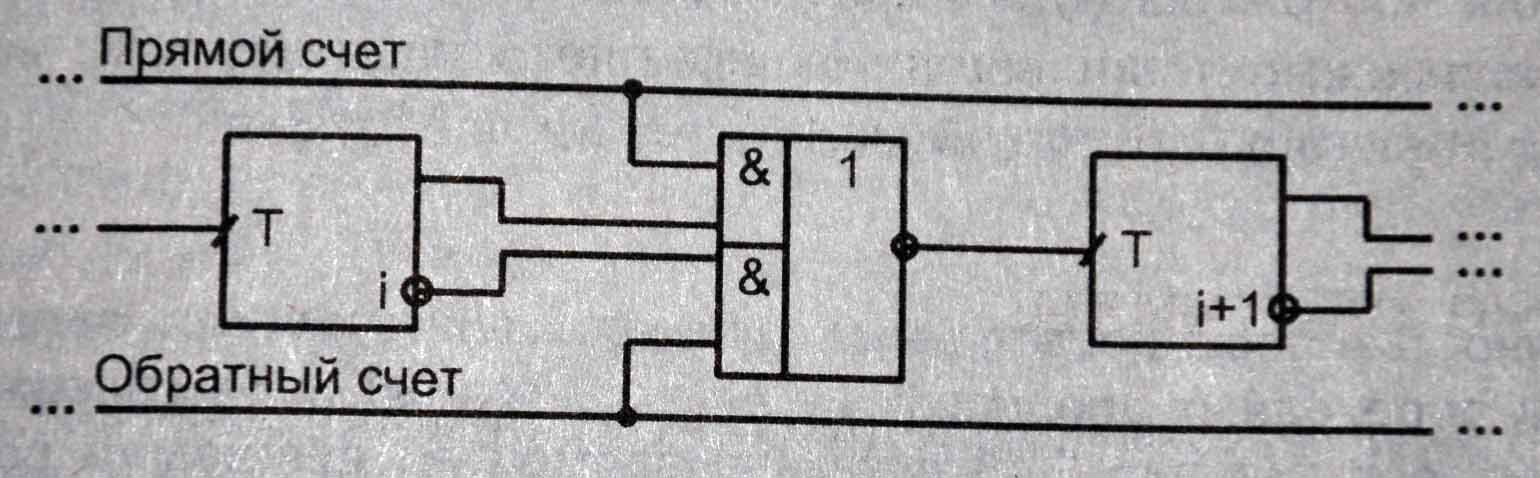

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

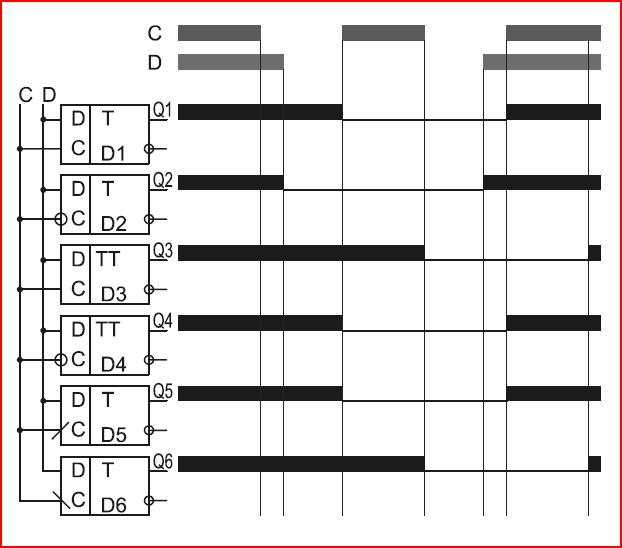

20. Триггер с динамическим управлением записью. Временная диаграмма.

Триггеры с динамическим управлением

Недостаток двухступенчатого триггера - более медленный выход. Решение: двухступенчатый триггер с динамическим управлением. Триггер с динамическим управлением срабатывает либо по переходу сигнала из О в 1 (по фронту); либо - из 1 в 0 (по спаду).

Реакция триггеров с различной структурой на входное воздействие (временная диаграмма)

21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

22. Последовательный и параллельный сдвигающие регистры.

Регистр — устройство для хранения данных. Представляет собой набор триггеров, к-ый позволяет хранить и видоизменять многорязрядный бинарный код (слово).

Регистры выполняют 2 функции:

1)Хранение данных

2)Сдвиг (видоизменение хранимого многорязрядного бинарного кода :)

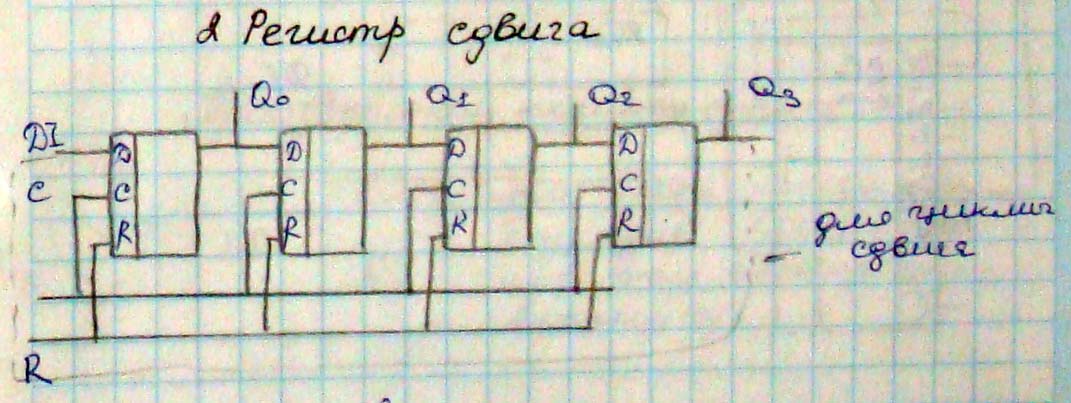

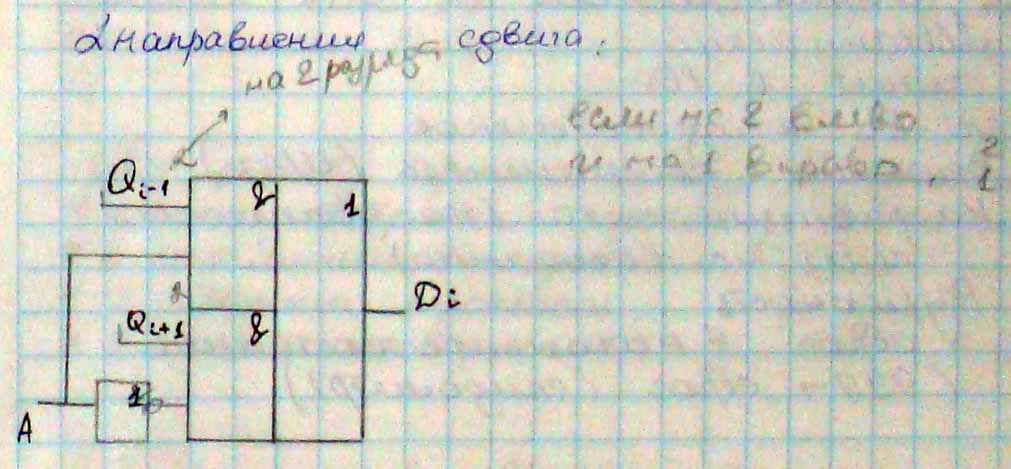

Сдвиг — операция при к-рой значение каждого разряда записывается в старший/младший (в зависимости от направления сдвига) разряд.

Сдвиги:

1)В сторону старших разрядов («сдвиг влево»).

2)В сторону младших («сдвиг вправо»).

а)Циклические — биты, выходящие за пределы разрядной сетки, записываются в последний рязряд регистра, противоположный направлению сдвига (Выход старшего/ младшего разряда — на вход младшего/старшего).

б)Нециклические — биты, выходящие за пределы разрядной сетки, теряются безвозвратно. Разряды, значение к-рых было сдвинуто, заполняются, например нулями.

Регистры:

1)Хранения — только хранит слов.

2)Сдвиговые — то же + сдвиг вправо/влево. Сдвиг происходит во время синхросигнала.

3)Реверсивные — то же + возможность указать направление сдвига.

Разрядность регистра — количество хранимых значений, набор образующих этот регистр триггеров (>=2).

Регистры по способу приема и выдачи данных:

1)параллельные — прием и выдача слов производится по всем разрядам одновременно.

2)последовательные — слова принимаются и выдаются разряд за разрядом.

3)послед.-параллельные — такие регистры имеют входы/выходы одновременно последовательного и параллельного типа. Имеются такие варианты как SIPO, PISO.

DI |

RG |

Q0 |

D0 |

||

... |

... |

|

Dn |

||

L |

Qn |

|

WE |

||

C |

|

|

R |

D0 |

RG |

Q0 |

... |

... |

|

Dn |

||

CE |

Qn |

|

C |

|

|

R |

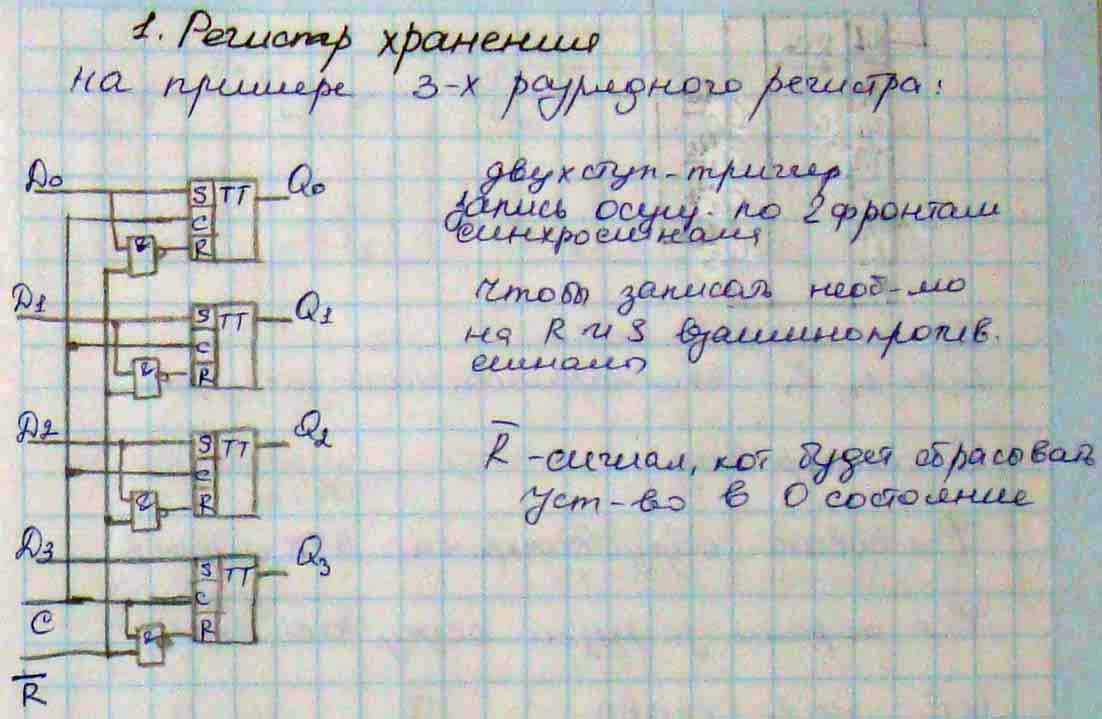

R(CLS) — Reset(Clear), сигнал обнуления всех разрядов регистра (R=1),

CE — Chip Enabled, регистр принимает управляющие сигналы, отличные от «СЕ» (СЕ=1),

Di — параллельный информационный вход,

Qi — разряд регистра.

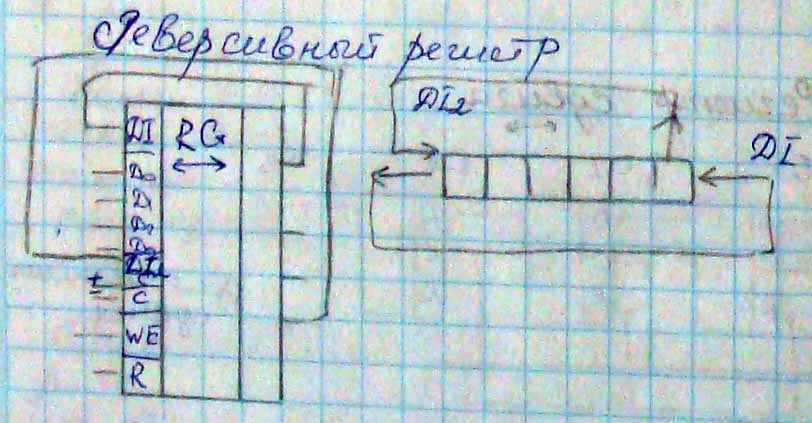

В сдвиговых и реверсивных регистрах (рис. справа):

L — Load, режим загрузки данных в регистр (1 — для параллельной загрузки, 0 — для последовательной (сдвиг)),

DI — последовательный информационный вход. При циклическом сдвиге на этот вход подается значение старшего/младшего разряда.

WE — Write Enabled — сигнал, разрешающий сдвиг.

в реверсивных:

S — вход управления направлением сдвига (как вариант, можно использовать два синхровхода),

DI2 — второй последовательный информационный вход.

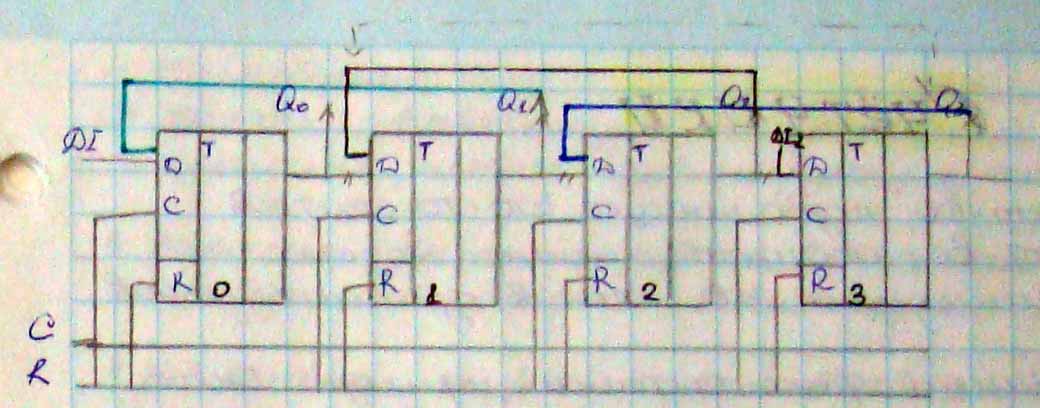

Схема регистра хранения

Схема сдвигового регистра

С

хема

реверсивного регистра

хема

реверсивного регистра

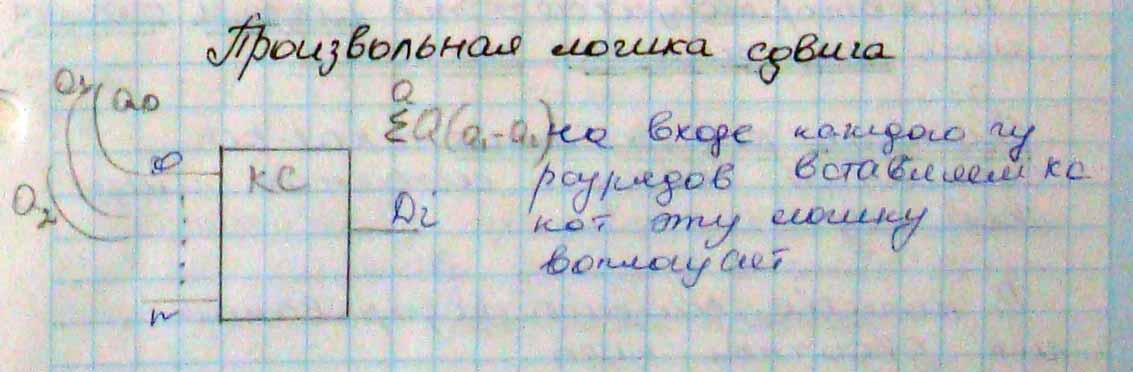

С двиг

на произвольное число разрядов

двиг

на произвольное число разрядов

23. Счетчики. Классификация счетчиков. Понятие модуля. Схемы суммирующих и вычитающих счетчиков. Временные параметры.

Счетчик — устройство, к-ое под действием входных импульсов переходит из одного состояние в другое, фиксируя тем самым число поступивших на его счетный вход импульсов в том или ином коде.

Выполняют 2 функции:

1)Хранение

2)Видоизменение хранимого числа

Классификация счетчиков

По способу кодирования внутренних состояний:

1)Двоичные

2)Двоично-десятичные

3)Джонсона

4)Прочие

По направлению счета:

1)Суммирующие

2)Вычитающие

3)Реверсивные (суммирует и вычитает)

По способу счета:

1)Синхронные

2)Асинхронные

По способу переноса:

1)Последовательного переноса

2)Параллельного

3)Сквозного

4)Комбинированного

Счетчик также характеризуется:

1)Модулем счета М — определяет число возможных состояний счета. После поступления на счетчик М счетных сигналов начинается новый цикл, повторяющий предыдущий.

2)Разрядностью.

3)Величиной инкремента/декремента.

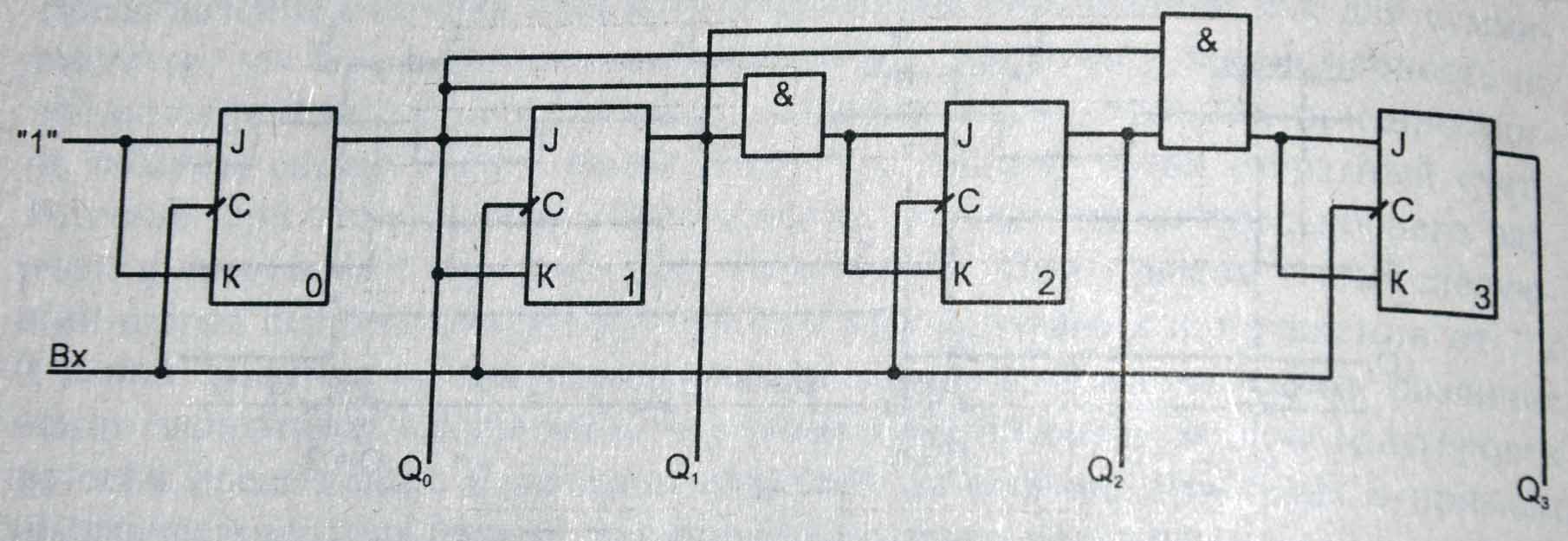

С хема

суммирующего синхронного счетчика с

параллельным переносом, реализованного

на триггерах с управлением фронтом.

хема

суммирующего синхронного счетчика с

параллельным переносом, реализованного

на триггерах с управлением фронтом.

Схема вычитающего счетчика

То же самое, только используются инвертированные выходы

Схема реверсивного счетчика

Временные параметры