- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

Мультиплексор реализует некоторая комбинационная схема (мультиплексорная схема), которая будет иметь n входов адреса (на которые будут подаваться сигналы x1,..., xn ), 2n входов DI - Data Input (вход данных -информационный сигнал) и один выход DO - это Data Out (выход данных - информационный выход). По существу, эта схема коммутирует 2n входных каналов на выходной канал.

Номер коммутируемого канала будет определяться набором сигналов x1,..., xn . Запишем функцию, реализуемую мультиплексором:

![]()

Мультиплексор выполняет функцию, обратную демультиплексору. Там у нас один вход коммутируется на один из 2n выходов, а здесь, наоборот - 2n входов коммутируется на один выход.

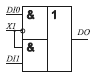

Из той функции, которую выполняет мультиплексор, понятна его реализация в схеме. Допустим, имеем мультиплексор на два входа и один выход:

D I0

- первый информационный вход. DI1

- второй информационный вход. При подаче

0 на адресный вход X1,на выход DO будет

передаваться сигнал с первого

информационного входа DIo; при подаче 1

- со второго информационного входа DI1.

I0

- первый информационный вход. DI1

- второй информационный вход. При подаче

0 на адресный вход X1,на выход DO будет

передаваться сигнал с первого

информационного входа DIo; при подаче 1

- со второго информационного входа DI1.

Аналогично рассмотрим мультиплексор, имеющий четыре информационных входа (адресных входа два - x1и x2) и один выход:

Первый элемент имеет адрес 00 ( x1=0 , т.е. x1 ; и x2=0 , т.е. x2 ); второй - 01; третий 10; четвёртый - 11.

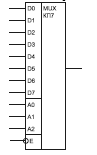

Мультиплексоров существует достаточно большое разнообразие. Например, типичный мультиплексор, имеющий 8 входов и один выход - это мультиплексор типа 155КП5.

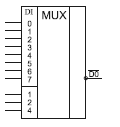

УГО: (см. рисунок 4)

Н а

основное поле ставится обязательно

"MUX" - т.к. это мультиплексор. Имеется

так же поле DI – поле информационных

входов. Нумеруются информационные

входы по номерам наборов. Так же –

имеется адресное поле; в адресном поле

указываются веса соответствующих

разрядов (весовые

коэффициенты).

А на выходе, в данном случае, стоит

инверсия. То есть при коммутации

какого-то сигнала DIi, будет передаваться

на выход инверсия этого сигнала.

а

основное поле ставится обязательно

"MUX" - т.к. это мультиплексор. Имеется

так же поле DI – поле информационных

входов. Нумеруются информационные

входы по номерам наборов. Так же –

имеется адресное поле; в адресном поле

указываются веса соответствующих

разрядов (весовые

коэффициенты).

А на выходе, в данном случае, стоит

инверсия. То есть при коммутации

какого-то сигнала DIi, будет передаваться

на выход инверсия этого сигнала.

Мультиплексор коммутирует на выход один из информационных входов.

E - вход разрешения.

Между n (количество информационных входов) и k (количество адресных входов) существует зависимость: максимальное количество входов данных n=2k; количество адресных входов k=log2n

Увеличение разрядности мультиплексоров

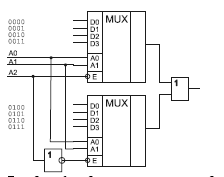

А если у нас есть только элемент КП2? Нам нужно построить мультиплексор общий, чтобы он имел один выход. И на нём реализовать функцию. Как на базе элемента КП2 (4→1)х2 построить 8→1 ? Прежде всего, должен быть объединяющий элемент. Какой это будет элемент, зная работу мультиплексора? Элемент "ИЛИ" (1).

А как нам поступить с E входами (входами разрешения), если их два? Нужно сделать так, чтобы работал либо один, либо второй - следовательно, между ними надо поставить инвертер:

Если будет 0 - работает верхняя половина; будет 1 - работает нижняя половина. А что будет на выходе того, который не работает? Ноль. А чтобы разрешить второму проходить при нуле? Поэтому соединяющий элемент должен быть, конечно "ИЛИ".

П ри

таком соединении E - окажется старшим

адресным разрядом (в данном случае,

A2).

ри

таком соединении E - окажется старшим

адресным разрядом (в данном случае,

A2).

То есть мы реализовали схему следующего мультиплексора: