- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

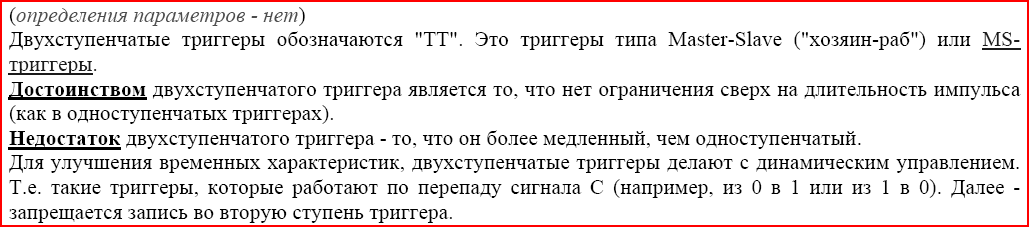

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

Синхронные триггеры с динамическим управлением записью

Изменяет свое состояние не по потенциалу а по фронту, т.е. переходу синхросигнала из одного состояния в другое. В зависимости от конструкции приггера активным фронтом может быть как передний так и задний фронт импульса синхронизации.

Отличительной чертой триггеров с динамическим управлением записью является то, что информация в триггер поступает только в момент изменения сигнала на входе С или из 0 в 1 или из 1 в 0. В первом случае триггер имеет прямой динамический вход С, а во втором - инверсный динамический вход С.

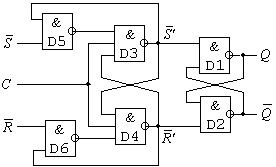

Рассмотрим более подробно принцип действия синхронного триггера с динамическим управлением записью на примере RS-триггера (рис. 3.12).

Рис.

3.12. Синхронный

![]() -триггер

с прямым динамическим управлением

записью

-триггер

с прямым динамическим управлением

записью

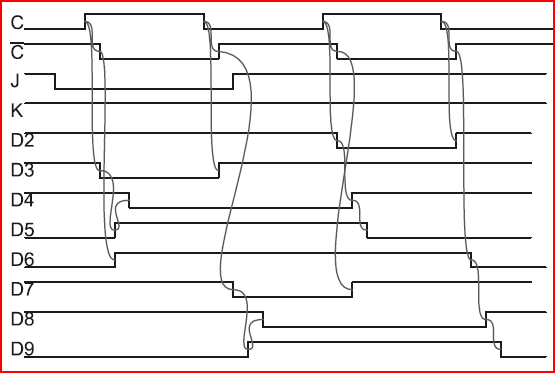

Временная диаграмма его работы приведена на рис. 3.13. Будем говорить, элемент ИНЕ закрыт, если хотя бы на одном из его входов находится сигнал 0 и открыт, если на всех его входах находится сигнал 1. В первом случае на выходе элемента будет сигнал 1, а во втором - сигнал 0.

Рис. 3.15. Временная диаграмма работы D-триггера

DV-триггер и JK-триггер

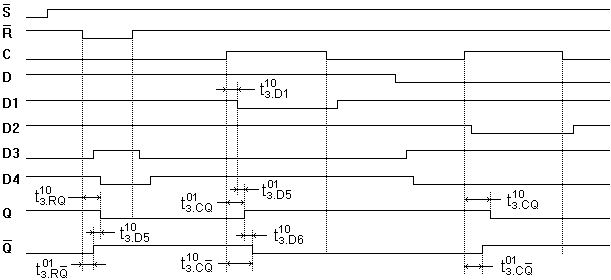

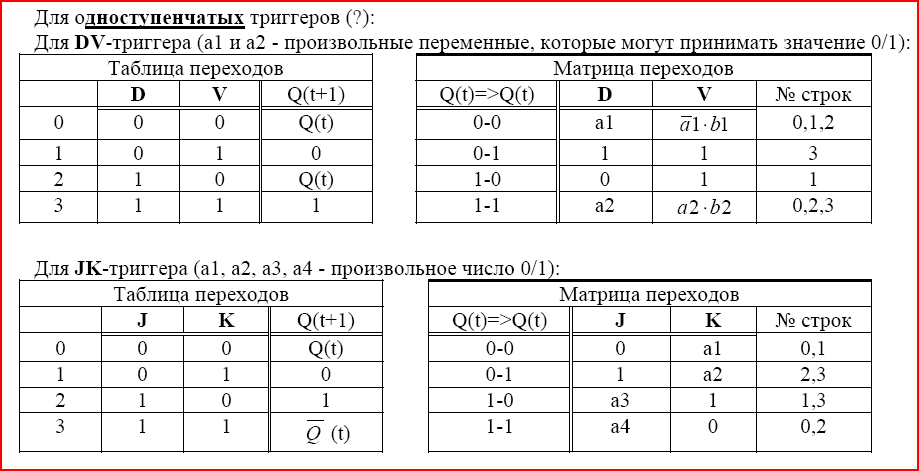

Структура D-триггера может служить основой для получения синхронных DV-триггера (рис. 3.16) и JK-триггера (рис. 3.17) с динамическим управлением записью.

Рис. 3.16. Синхронный DV-триггер с инверсным динамическим входом С и его условное графическое обозначение

Рис.

3.17.Синхронный

![]() -триггер

с прямым динамическим входом С и его

условное графическое обозначение

-триггер

с прямым динамическим входом С и его

условное графическое обозначение

18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

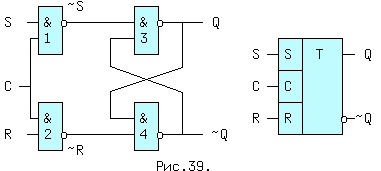

Если незадействованные входы элементов И-НЕ 1 и 2 соединить вместе (рис. 36), получится синхронный RS - триггер со статическим управлением (синхронизируемый уровнем). Схема и условное обозначение приведены на рис.39.

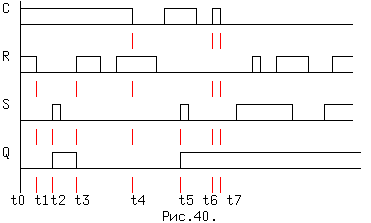

Нетрудно убедиться, что при C=0 сигнал Q=~(~Q*1)=Q, а ~Q=~(Q*1)=~Q, т.е. независимо от значений S и R, выходы сохраняют старые значения и триггер находится в режиме памяти. При C=1 он функционирует, как асинхронный RS-триггер. Триггеры со статическим управлением называют, также "прозрачными", т.к. при активном уровне синхросигнала C, информация с входов беспрепятственно проходит на выходы. Временные диаграммы приведены на рис.40.

До момента времени t4 сигнал C = 1 и выходное значение определяется комбинациями сигналов R и S. В течение интервала времени t0...t1 на входе R действует 1, а сигнал S = 0, поэтому Q тоже равно 0. Начиная с момента t1 и до момента t2 R = S = 0 и действует режим памяти (Q не изменяется). В момент t2 R = 0,а S = 1 и триггер устанавливается (Q = 1). С момента окончания импульса S и до момента t3 триггер хранит эту единицу, а в момент t3 сбрасывается, т.к.R = 0, а S = 1. Аналогично можно проанализировать и все остальные состояния выхода.

АСИНХРОННЫЙ RS - ТРИГГЕР

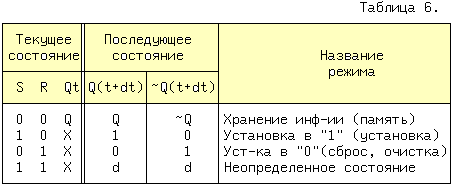

Асинхронный триггер имеет два входа S(et) - установка и R(eset) - сброс и два выхода прямой - Q и инверсный - ~Q. Триггер переходит из текущего состояния X на выходе к состоянию 0, при подаче на вход S нуля и на вход R единицы, а при поступлении на вход S единицы и на вход R нуля триггер переходит к состоянию 1. При нулевых значениях, когда S=R=0 триггер должен сохранять старое значение. Комбинация сигналов S=R=1 не определена. В соответствии с описанием составим таблицу состояний триггера (таблица 6).

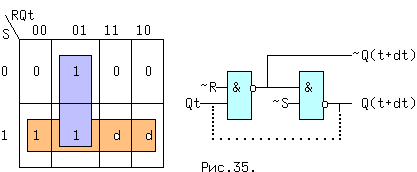

Q и X - могут принимать любые значения, но Q в пределах одной строки, неизменно. Значения d будут доопределены на этапе минимизации. Входных переменных три - S,R и текущее состояние выхода Qt, поэтому всего должно быть восемь состояний при различных значениях Q и X. Последующее состояние выходов отделено от текущего временем задержки сигнала dt. Таблица Карно функции Q(t+dt) с учетом всех возможных состояний приведена на рис.35, слева.

Доопределяем значения d единицей и находим характеристическое уравнение RS - триггера:

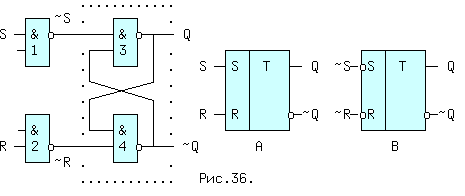

Q(t+dt) = S + ~R*Qt = ~(~S * ~(~R*Q)). (26)

Этому уравнению соответствует схема на рис.35, справа. Учитывая, что Qt и Q(t+dt) сигналы на одном и том же выходе, но в разные моменты времени, свяжем их. Окончательно схема триггера и его условное обозначение будет выглядеть, как на рис.36.

Условное обозначение B соответствует части рисунка, обведенной точками, т.е. RS триггеру с инверсными входами, а обозначение A - всему рисунку, или RS триггеру с прямыми входами.

Если на триггер с прямыми входами подать сигналы R=S=1 или на входы инверсного - нули, то оба выхода Q и ~Q будут установлены в 1, что противоречит аксиоме Q*~Q = 0. Поэтому такой режим, иногда называют запрещенным. Однако ничто не мешает разработчику использовать его, например для сигнализации об одновременном и нежелательном поступлении единичных сигналов на RS входы, введением дополнительной схемы И.

Временные диаграммы RS триггера с инверсными входами приведены на рис.37. Через время tзд.р., обозначенное "-", от поступления сигнала ~S = 0 на вход элемента И-НЕ с номером 3, выход Q переключится первым, а следом через такой же промежуток времени переключится и выход ~Q. Спустя интервал времени t2 - t0 = dt на выходах установятся новые значения. Также протекает процесс при ~R = 0, но выход ~Q переключится первым. Отсюда вытекает, что изменение входных сигналов не должно происходить быстрее времени dt.

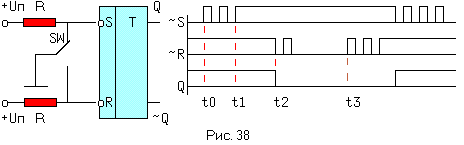

Одним из применений RS триггера с инверсными входами служит схема подавления "дребезга" контактов клавиатуры. Процесс многократного размыкания и замыкания контактов при их переключении называется дребезгом. Схема и диаграммы показаны на рис.38.

В момент t0 нажатия на клавишу, начинаются соударения верхнего и среднего контактов. До момента t1 сигналы ~S,~R поочередно принимают значения 1,1 и 0,1 что соответствует режимам памяти и установки в 1. При этом, естественно начальное значение Q = 1 не изменится, что и требуется. В интервале t1..t2 средний контакт находится в "свободном полете". Первое его касание нижнего контакта в момент t2 сбросит триггер (~S = 1, ~R = 0). До момента t3 сигналы ~S,~R поочередно принимают значения 1,0 и 1,1 что соответствует режимам сброса и памяти, т.е. Q = 0. При отпускании клавиши (момент t3) развивается обратный процесс. В результате действия схемы выходной сигнал чист от импульсных помех.

D-триггер

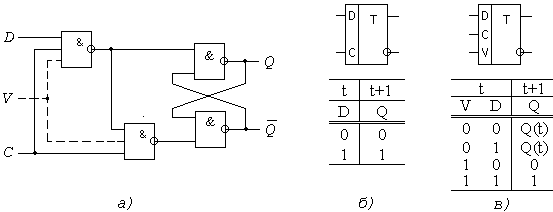

На практике наибольшее распространение получила схема синхронного D-триггера со статическим управлением записью. D-триггер имеет один логический вход D (Delay - задержка), состояние которого с каждым СИ передается на выход, т.е. выходные сигналы представляют собой задержанные входные сигналы. Схему D-триггера можно получить из RS-триггера, если на вход R подать инвертированный сигнал входа S. Однако целесообразно использовать для инвертирования уже имеющиеся элементы (рис. 3.6).

Рис. 3.6. Синхронный D-триггер со статическим управлением записью (пунктиром показан вход V для DV-триггера):

а) логическая схема; б) условное графическое обозначение D-триггера и его таблица переходов; в) условное графическое обозначение DV-триггера и его таблица переходов

DV-триггер

Если к D-триггеру добавить еще один вход V (Vorentscheidung - предварительное разрешение) для блокирования СИ (пунктирная линия на рис 3.6), то получим синхронный DV-триггер со статическим управлением записью. Легко заметить, что входы С и V можно поменять местами без нарушения логики работы триггера.

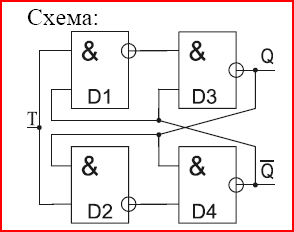

Одноступенчатый асинхронный T – триггер.

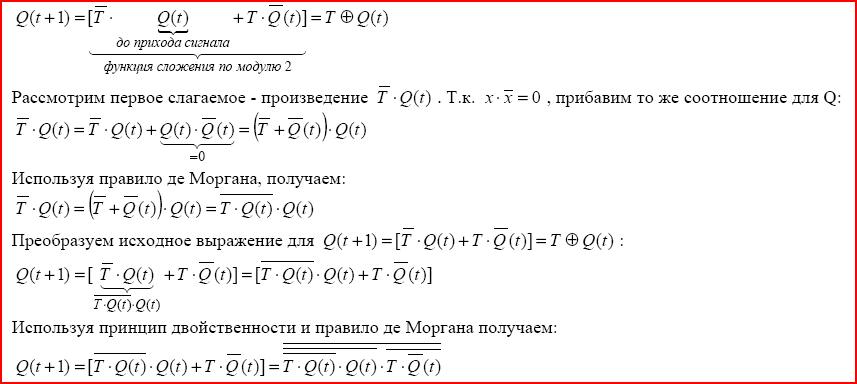

Счетный Т-триггер. Его называют также триггером со счетным входом. Он имеет один управляющий вход Т и два выхода Q и -Q. Информация на выходе такого триггера меняет свой знак на противоположный при каждом положительном (или при каждом отрицательном) перепаде напряжения на входе. Триггер такого типа может быть создан на базе тактируемого D-триггера, если его инверсный выход соединить с информационным входом . Как видно из диаграммы, частота сигнала на выходе Т-триггера в два раза ниже частоты сигнала на входе, поэтому такой триггер можно использовать как делитель частоты и двоичный счетчик.

Таким образом мы получаем различные пути синтеза одноступенчатых триггерных схем. В одноступенчатом триггере ограничение на длительность входного импульса будет с двух сторон(задается не только минимсальная но и максимальная длительность импульса при которой триггер будет вести себя как триггер, т.е. на выходе неQ будет инверсное состояние Q)

Одноступенчатый синхронный T – триггер.

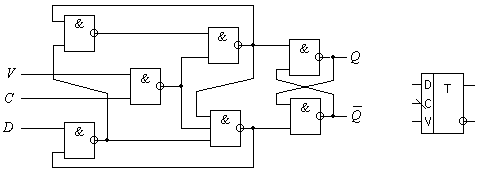

Чтобы сгладить проблему ограничения по длине импульса в асинхронном одноступенчатом триггере можно усовершенствовать схему и сделать триггер синхронным. Т.е. взяли и добавили ещё вход С на элементы D1 и D2. Тогда действительно управляющий вход Т который разрешает работу этому Т-триггеру в счетном режиме. А вход синхронизации будет выполнять ту же самую роль что и вход Т в асинхронном режиме.

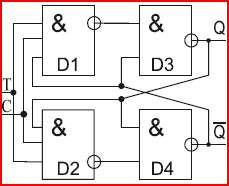

19. JK-MS и DV-MS триггеры. Схема, Временная диаграмма, определение параметров.

DV-триггер

Временная диаграмма

Алгоритм построения временной диаграммы

Ключевые понятия для построения временной диаграммы:

Событие - это изменение любого сигнала любого сигнала.

Момент времени, для которого определяется состояние схемы, называется текущим.

Для построения временной диаграммы, сначала необходимо задать начальное состояние схемы для запоминающих элементов с учётом обратных связей. Например, Q(t0)=0.

Алгоритм построения временной диаграммы:

1. По входной диаграмме определить первое событие;

2. Поместить в список элементы, на которые поступает это событие;

3. Взять один из элементов списка и вычислить его выход (реализовать событие).

a. если новое значение не равно старому, то отметить это изменение через время задержки

![]() и

и

![]() относительно текущего момента времени;

относительно текущего момента времени;

b. если новое значение равно старому, то оно сохраняется.

4. Повторить шаг 3 для других элементов списка;

5. По выходной диаграмме и диаграммам выходов элементов найти ближайшее событие и перейти к шагу 2.