- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

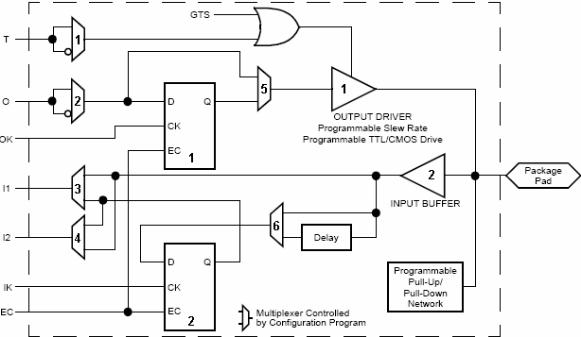

Блоки ввода/вывода сигналов

ПЛИС FPGA находят широкое применение также благодаря тому, что имеют большое число блоков ввода/вывода сигналов, настраиваемых под различные стандарты электрического соединения микросхем. Блоки ввода/вывода (БВВ) обеспечивают интерфейс между выводами корпуса ПЛИС FPGA и ее внутренними логическими схемами. Каждому выводу корпуса придается блок ввода/вывода БВВ, который может быть конфигурирован как вход, выход или двунаправленный вывод.

На рис. 1.4 показана упрощенная функциональная блок-схема одного блока ввода/вывода (I/O block, IOВ). Сигнальный вывод ПЛИС получил название PAD. С помощью настройки к нему можно подключать внутренний нагрузочный резистор PULL-UP или резистор PULL-DOWN, соединенные с шиной питания или шиной земли, соответственно. Эти резисторы обеспечивают режим выхода с открытым коллектором (стоком) для систем с различными уровнями логики.

Р ис.

1.4. Упрощенная

структура блока ввода/вывода Работа

БВВ как выходного блока обслуживается

следующими элементами: выходным буфером

1,

триггером 1,

мультиплексорами 1,

2, 5 и

логической схемой ИЛИ (см. рис. 1.4).

Выводимый сигнал О

можно

получать в прямой или инверсной форме

в зависимости от программирования

мультиплексора 2.

Этот сигнал может передаваться на

выходной буфер непосредственно или

сниматься с триггера при соответствующем

программировании мультиплексоpa 5.

Сигналы Т

и

GTS

(Global

Tri-State), согласно логике ИЛИ, управляют

переводом буфера в третье состояние,

причем активный уровень сигнала Т

программируется

с помощью мультиплексора 1.

Внутренние программируемые цепи триггера

(на рисунке не показаны) позволяют

изменять полярность тактирующего

фронта. Сам буфер имеет программируемые

крутизну фронта выходного сигнала и

его уровни — КМОП/ТТЛ. Крутизна фронтов

в некритичных к скорости передачи цепях

снижается для уменьшения уровня помех

на шинах питания и земли. Тракт ввода

сигналов содержит входной буфер 2,

триггер 2,

программируемые мультиплексоры 3,

4, 6,

элемент задержки Delay

(см.

рис. 1.4). Вводимый сигнал в зависимости

от программирования мультиплексоров

3

и

4

или

поступает непосредственно в систему

коммутации FPGA по входным линиям I1

и I2,

или же фиксируется триггером и с его

выхода передается в эти линии. Для

обеспечения временного сдвига входного

сигнала относительно фронта синхросигнала,

гарантирующего надежный прием сигнала

во внутренний триггер, в цепь входного

сигнала может включаться специальная

схема задержки. Входной буфер может

конфигурироваться для приема входных

сигналов с пороговым значением ТТЛ (1,2

В) или КМОП (0,5 Ucc).

ис.

1.4. Упрощенная

структура блока ввода/вывода Работа

БВВ как выходного блока обслуживается

следующими элементами: выходным буфером

1,

триггером 1,

мультиплексорами 1,

2, 5 и

логической схемой ИЛИ (см. рис. 1.4).

Выводимый сигнал О

можно

получать в прямой или инверсной форме

в зависимости от программирования

мультиплексора 2.

Этот сигнал может передаваться на

выходной буфер непосредственно или

сниматься с триггера при соответствующем

программировании мультиплексоpa 5.

Сигналы Т

и

GTS

(Global

Tri-State), согласно логике ИЛИ, управляют

переводом буфера в третье состояние,

причем активный уровень сигнала Т

программируется

с помощью мультиплексора 1.

Внутренние программируемые цепи триггера

(на рисунке не показаны) позволяют

изменять полярность тактирующего

фронта. Сам буфер имеет программируемые

крутизну фронта выходного сигнала и

его уровни — КМОП/ТТЛ. Крутизна фронтов

в некритичных к скорости передачи цепях

снижается для уменьшения уровня помех

на шинах питания и земли. Тракт ввода

сигналов содержит входной буфер 2,

триггер 2,

программируемые мультиплексоры 3,

4, 6,

элемент задержки Delay

(см.

рис. 1.4). Вводимый сигнал в зависимости

от программирования мультиплексоров

3

и

4

или

поступает непосредственно в систему

коммутации FPGA по входным линиям I1

и I2,

или же фиксируется триггером и с его

выхода передается в эти линии. Для

обеспечения временного сдвига входного

сигнала относительно фронта синхросигнала,

гарантирующего надежный прием сигнала

во внутренний триггер, в цепь входного

сигнала может включаться специальная

схема задержки. Входной буфер может

конфигурироваться для приема входных

сигналов с пороговым значением ТТЛ (1,2

В) или КМОП (0,5 Ucc).

Программируемые соединения

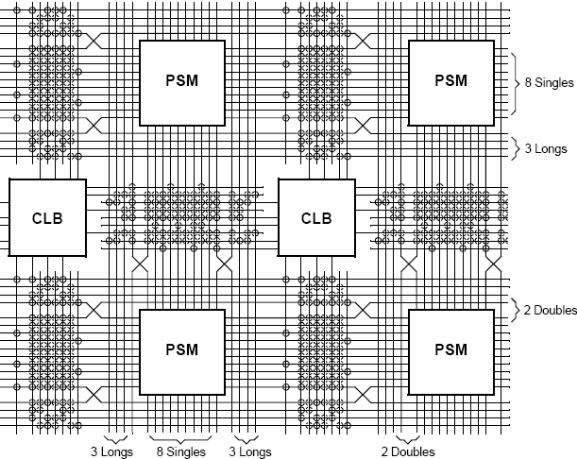

Как показано на рис. 1.5, логические блоки в ПЛИС FPGA окружены системой каналов, которые состоят из совокупности металлических сегментов («проводов»), соединяемых друг с другом

программируемым элементом связи (ключом). Трассировочные каналы вокруг CLB состоят из трех типов соединительных проводов: одинарной длины, двойной длины и длинные сегменты, пересекающие кристалл по всей его длине или ширине. Кружками на рис. 1.5 отмечены программируемые точки связи.

На пересечении каждого вертикального и горизонтального каналов находится матрица программируемых переключателей (PSM, Programmable Switching Matrix).

Л инии

одинарной длины осуществляют соединения

соседних или близлежащих CLB. Линии

двойной длины огибают переключательные

блоки PSM, соседние по отношению к данному,

и проходят к следующим, чем облегчается

установление более длинных связей. Три

длинные линии, пересекающие весь кристалл

по длине (ширине), предназначены на

передачу сигналов на большие расстояния

и при большой нагрузке. Выводы логических

блоков (CLB) пересекают горизонтальные

и вертикальные каналы трассировки,

проходящие непосредственно около них,

и могут программируемыми элементами

связи (ключами) подключаться к линиям

каналов. Дальнейшее направление сигналов

в нужные цепи осуществляется матрицей

программируемых переключателей.

инии

одинарной длины осуществляют соединения

соседних или близлежащих CLB. Линии

двойной длины огибают переключательные

блоки PSM, соседние по отношению к данному,

и проходят к следующим, чем облегчается

установление более длинных связей. Три

длинные линии, пересекающие весь кристалл

по длине (ширине), предназначены на

передачу сигналов на большие расстояния

и при большой нагрузке. Выводы логических

блоков (CLB) пересекают горизонтальные

и вертикальные каналы трассировки,

проходящие непосредственно около них,

и могут программируемыми элементами

связи (ключами) подключаться к линиям

каналов. Дальнейшее направление сигналов

в нужные цепи осуществляется матрицей

программируемых переключателей.

Рис. 1.5. Упрощенная система коммутации ПЛИС FPGA

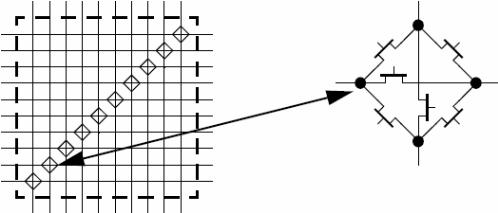

В матрице программируемых переключателей (рис. 1.6) пересекаются вертикальные и горизонтальные линии связи, и в каждом пересечении имеется цепь из 6 транзисторов для установления того или иного соединения. Сигнал, поступающий в матрицу переключателей по какой-либо линии (например, горизонтальной), может быть направлен вверх, вниз или прямо в зависимости от того, какой транзистор будет открыт при конфигурировании FPGA. Возможна и одновременная передача сигнала по нескольким направлениям, если требуется его разветвление.

Хотя матрица программируемых переключателей является необходимым компонентом, но за его использование приходится платить: при каждом прохождении сигналов через такую матрицу вносится небольшая задержка. Поэтому программа компоновки ищет не только возможные размещения логических блоков и какую-то комбинацию соединений, которые будут работать. Программа «размещения и трассировки» затрачивает много времени, пытаясь оптимизировать характеристики устройства путем нахождения такого размещения, которое позволило бы сделать соединения короткими, и только после этого осуществляет реализацию самих соединений.

Р ис.

1.6. Матрица

программируемых переключателей PSM

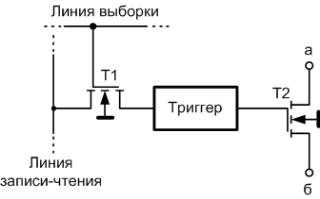

Транзисторный ключ,

управляемый триггером памяти

конфигурации, показан на рис. 1.7. Ключевой

транзистор Т2 замыкает или размыкает

участок аb

в

зависимости от состояния триггера,

выход которого подключен к затвору

транзистора Т2. При программировании

на линию выборки подается высокий

потенциал, и транзистор Т1 включается.

С линии записи-чтения подается сигнал,

устанавливающий триггер в состояние

логической "1" или "0". В рабочем

режиме транзистор Т1 заперт, триггер

сохраняет неизменное состояние. Так

как от триггера памяти конфигурации

высокое быстродействие не требуется,

он проектируется с оптимизацией по

параметрам компактности и максимальной

устойчивости стабильных состояний.

Помехи в несколько вольт для такого

триггера не влияют на его состояние.

ис.

1.6. Матрица

программируемых переключателей PSM

Транзисторный ключ,

управляемый триггером памяти

конфигурации, показан на рис. 1.7. Ключевой

транзистор Т2 замыкает или размыкает

участок аb

в

зависимости от состояния триггера,

выход которого подключен к затвору

транзистора Т2. При программировании

на линию выборки подается высокий

потенциал, и транзистор Т1 включается.

С линии записи-чтения подается сигнал,

устанавливающий триггер в состояние

логической "1" или "0". В рабочем

режиме транзистор Т1 заперт, триггер

сохраняет неизменное состояние. Так

как от триггера памяти конфигурации

высокое быстродействие не требуется,

он проектируется с оптимизацией по

параметрам компактности и максимальной

устойчивости стабильных состояний.

Помехи в несколько вольт для такого

триггера не влияют на его состояние.

Р ис.

1.7. Схема

ключевого транзистора, управляемого

триггером памяти конфигурации Триггеры

памяти конфигурации распределены по

всему кристаллу СБИС вперемешку с

элементами схемы, которые они конфигурируют.

Загрузка соответствующих данных в

память конфигурации программирует

ПЛИС. Процесс оперативного программирования

может производиться неограниченное

число раз. В ПЛИС FPGA с триггерной памятью

конфигурация разрушается при каждом

выключении питания. При включении

питания необходим процесс

программирования (инициализации,

конфигурирования) схемы

— загрузка данных конфигурации.

ис.

1.7. Схема

ключевого транзистора, управляемого

триггером памяти конфигурации Триггеры

памяти конфигурации распределены по

всему кристаллу СБИС вперемешку с

элементами схемы, которые они конфигурируют.

Загрузка соответствующих данных в

память конфигурации программирует

ПЛИС. Процесс оперативного программирования

может производиться неограниченное

число раз. В ПЛИС FPGA с триггерной памятью

конфигурация разрушается при каждом

выключении питания. При включении

питания необходим процесс

программирования (инициализации,

конфигурирования) схемы

— загрузка данных конфигурации.

Обобщая представленную вводную информацию, можно еще раз отметить основные особенности ПЛИС:

возможность быстрого изменения принципиальной электрической схемы устройства на стадии проектирования, в том числе с использованием языков описания аппаратуры (HDL);

малое время цикла «редактирование схемы — программирование ПЛИС — тестирование» при полном отсутствии каких-либо монтажных работ и материальных затрат;

поддержка внутри одного кристалла практически всего спектра современных технических решений в области цифровой электроники с гарантированными временными характеристиками;

относительно дешевые (в том числе и бесплатные) средствасквозной разработки, работающие на платформе ПК под управлением Windows, простые средства загрузки кристалла, дающие возможность с минимальными затратами провести освоение данной технологии.

ПЛИС существует теневая (конфигурационная) память, хранящая

таблицу соединений.