- •1.Способы представления цифровой информации. Основные характеристики элементов эвм. Логическая модель элементов с потенциальным представлением информации.

- •2.Переключательная характеристика цифрового элемента. Понятие Базиса. Таблицы Истинности, Прямые и инверсные входы и выходы логических э лементов. Уго элементов.

- •3.Реализация функций Алгебры логики (фал) на элементах эвм. Способы задания функций. Переход от одних способов задания фал к другим.Минимизация Методом Квайна Мак-Класски.

- •4.Построение комбинационных схем на логических элементах. Технологии минимизации комбинационных схем. Использование диаграмм Вейча для минимизации фал.

- •Использование диаграмм вейча для минимизации.

- •5.Задачи анализа и синтеза цифровых схем. Минимизация не полностью определенных фал.

- •6.Мультиплексоры и их назначение. Уго. Увеличение разрядности мультиплексоров. Реализация фал на мультиплексоре.

- •Увеличение разрядности мультиплексоров

- •7. Дешифраторы и их назначение, построение, увеличение разрядности дешифраторов. Реализация фал на дешифраторе.

- •8.Использование мультиплексоров, дешифраторов и запоминающих устройств для построения логических функций.

- •9.Сумматоры. Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •Комбинационные сумматоры. Принципы организации цепей переноса в сумматорах.

- •10 Сумматоры. Накапливающие сумматоры. Принципы организации цепей переноса в сумматорах.

- •11 Сумматоры. Комбинированные сумматоры. Принципы организации цепей переноса в сумматорах.

- •12 Элементарные триггерные ячейки на элементах и-не и или-не. Rs- триггер, таблица и матрица переходов.

- •13.14.15. Триггерные схемы. Классификация. Таблицы и матрицы переходов. Построение произвольного триггера на базе rs – триггера, dv триггера, jk триггера.

- •16.Асинхронные и синхронные триггерные схемы. Двухступенчатые триггерные схемы.

- •17. Схемы триггеров со статическим и динамическим управлением.

- •Синхронные триггеры с динамическим управлением записью

- •18. Синхронные и асинхронные одноступенчатые триггеры тиво rs, dv,t синхронный rs - триггер

- •20. Триггер с динамическим управлением записью. Временная диаграмма.

- •21.Регистры. Классификация. Уго регистров. Регистры хранения и сдвига.

- •22. Последовательный и параллельный сдвигающие регистры.

- •24. Счетчик по модулю м. Проектирование счетчиков. Изменение коэффициента пересчета.

- •25.Проектирование счетчика с заданным набором состояний на rs триггерах.

- •27.Проектирование счетчика с заданным набором состояний на jk триггерах.

- •Составление функций возбуждения триггеров счетчика

- •26.Проектирование счетчика с заданным набором состояний на dv триггерах.

- •28.Счетчики. Реверсивный счетчик. Функция параллельной загрузки. Увеличение разрядности.

- •Реверсивный счетчик

- •29. Асинхронные счетчики. Построение счетчика произвольной разрядности. Организация цепей переноса в асинхронных счетчиках.

- •Межразрядные связи реверсивного асинхронного счетчика с последовательным переносом.

- •30. Микросхемы памяти. Организация микросхемы памяти с произвольной выборкой. Временная диаграмма цикла записи.

- •31. Общая структура микросхемы памяти с произвольной выборкой. Временная диаграмма цикла чтения.

- •Уго микросхемы памяти.

- •32.Реализация фал на микросхемах памяти.

- •33.Запоминающая ячейка статического типа, устройство и принцип работы.

- •34. Запоминающая ячейка динамического типа, устройство и принцип работы.

- •35. Программируемые логические интегральные схемы. Основные принципы построения плм.

- •38.Реализация логических функций в плис, lut- назначение и устройство

- •39.Блоки ввода вывода Плис, Теневая память. Программируемые соединения

35. Программируемые логические интегральные схемы. Основные принципы построения плм.

Микросхемы программируемой логики или ПЛИС (программируемые логические интегральные схемы) — одно из наиболее динамично развивающихся направлений современной цифровой электроники. Привлекательность данной технологии заключается в предоставляемой конечному пользователю возможности быстрого создания цифровых устройств с произвольной внутренней структурой. По сравнению со специализированными цифровыми микросхемами (Application Specific Integral Circuit, ASIC), цикл разработки устройств на ПЛИС занимает значительно меньшее время и неизмеримо дешевле (благодаря тому, что изменение принципиальной электрической схемы выполняется путем перепрограммирования одного и того же экземпляра микросхемы). Таким образом, вместо металлических соединений, реализуемых в процессе производства ASIC, в ПЛИС используются соединения, коммутируемые программируемыми ключами. Для задания этих соединений в ПЛИС существует теневая (конфигурационная) память, хранящая таблицу соединений.

В настоящее время наиболее распространенные серии ПЛИС имеют следующую архитектуру:

CPLD (Complex Programmable Logic Device) устройства, использующие для хранения конфигурации энергонезависимую память (Flash или EEPROM);

FPGA (Field Programmable Gate Array) устройства, использующие для хранения конфигурации энергозависимую память, которая требует инициализации после включения питания.

Поскольку универсальный лабораторный стенд, содержит ПЛИС FPGA, то ниже рассматривается только этот тип микросхем программируемой логики.

36.Обобщенная структура ПЛИС FPGA. Основные элементы, их назначение принцип работы.

37.Обобщенная структура ПЛИС FPGA. Назначение и устройство CLB.

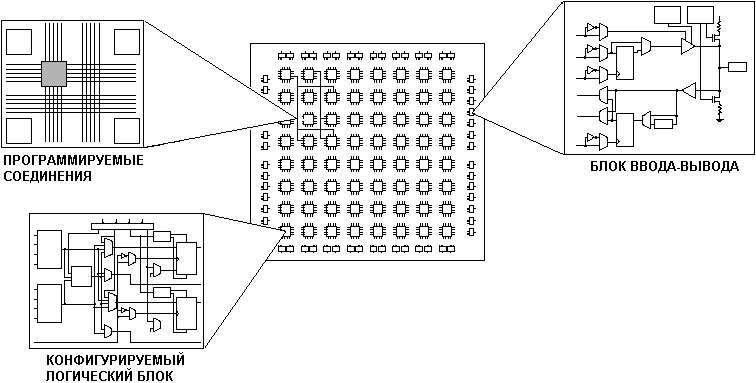

Интегральные схемы типа FPGA

В наиболее типичном варианте ПЛИС,

выполненная по технологии FPGA,

состоит из прямоугольной матрицы

конфигурируемых логических блоков

(Configurable

Logic Blocks,

CLB),

окруженной блоками ввода-вывода

(Input/Output

Block,

IOB).

Между CLB

располагаются программируемые

трассировочные линии (рис. 1).

Между

матрицей CLB

и блоками ввода-вывода имеются отдельные

межсоединения, которые и обеспечивают

подключение внешних сигналов.

наиболее типичном варианте ПЛИС,

выполненная по технологии FPGA,

состоит из прямоугольной матрицы

конфигурируемых логических блоков

(Configurable

Logic Blocks,

CLB),

окруженной блоками ввода-вывода

(Input/Output

Block,

IOB).

Между CLB

располагаются программируемые

трассировочные линии (рис. 1).

Между

матрицей CLB

и блоками ввода-вывода имеются отдельные

межсоединения, которые и обеспечивают

подключение внешних сигналов.

Рис. 1. Обобщенная структура ПЛИС FPGA

Все части FPGA (конфигурируемые логические блоки, система межсоединений и блоки ввода/вывода) являются конфигурируемыми или реконфигурируемыми, причем средствами самих пользователей.

При конфигурировании FPGA логические блоки настраиваются на выполнение необходимых операций преобразования данных, а система межсоединений — на требуемые связи между логическими блоками. В результате во внутренней области FPGA реализуется схема нужной конфигурации. Расположенные по краям кристалла блоки ввода/вывода обеспечивают интерфейс FPGA с внешней средой. Блоки ввода/вывода современных FPGA можно программировать на выполнение требований множества стандартов передачи данных (число таких стандартов может доходить до 20).

К онфигурирование

— это процесс загрузки битовой

последовательности, полученной с помощью

программного обеспечения проектирования,

во внутреннюю энергозависимую

конфигурационную память кристалла

FPGA.

При выключении питания конфигурация в

ПЛИС

FPGA

разрушается. Поэтому при включении

питания необходим процесс

программирования (инициализации,

конфигурирования) кристалла

FPGA

— загрузка данных конфигурации. Для

отладки спроектированной схемы используют

специальный кабель для загрузки

конфигурационных данных. Этот кабель

соединяет персональный компьютер с

микросхемой FPGA.

В конечном устройстве отлаженные данные

конфигурации хранятся

в ПЗУ, которое непосредственно

подключается к ПЛИС

FPGA,

и

после включения питания они автоматически

загружаются

в ПЛИС.

Процесс конфигурирования может

производиться неограниченное число

раз.

онфигурирование

— это процесс загрузки битовой

последовательности, полученной с помощью

программного обеспечения проектирования,

во внутреннюю энергозависимую

конфигурационную память кристалла

FPGA.

При выключении питания конфигурация в

ПЛИС

FPGA

разрушается. Поэтому при включении

питания необходим процесс

программирования (инициализации,

конфигурирования) кристалла

FPGA

— загрузка данных конфигурации. Для

отладки спроектированной схемы используют

специальный кабель для загрузки

конфигурационных данных. Этот кабель

соединяет персональный компьютер с

микросхемой FPGA.

В конечном устройстве отлаженные данные

конфигурации хранятся

в ПЗУ, которое непосредственно

подключается к ПЛИС

FPGA,

и

после включения питания они автоматически

загружаются

в ПЛИС.

Процесс конфигурирования может

производиться неограниченное число

раз.

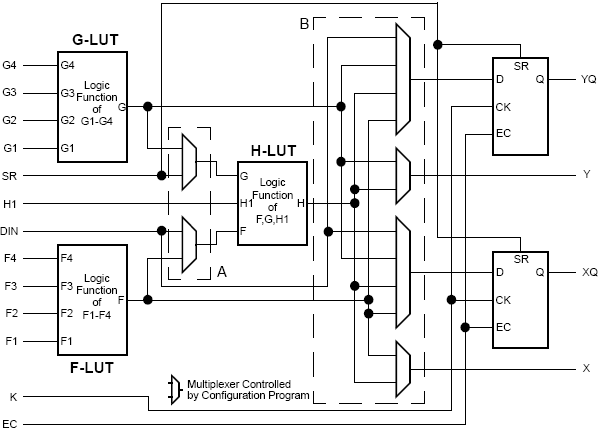

ПЕРЕСТРАИВАЕМЫЙ ЛОГИЧЕСКИЙ БЛОК

Основным элементом ПЛИС FPGA фирмы Xilinx является конфигурируемый логический блок (CLB). На рис. 2 показана упрощенная внутренняя структура логического блока ПЛИС семейства Spartan.

Рис. 2. Структура CLB ПЛИС семейства Spartan

В состав CLB входят:

три таблицы преобразования LUT (Look-Up Table), которые используются как генераторы логических функций;

два триггера;

две группы А и В программируемых мультиплексоров, играющих роль средств конфигурирования CLB.