- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

4.1.2 Проектування центрального процесора

Для побудови центрального процесора (ЦП) на основі МП КР580ВМ80А додатково необхідні мікросхеми формування сигналів синхронізації і спряження з системними магістралями. Структура ЦП показана на рисунку 4.8

Рисунок 4.8 – Структура ЦП на ВІС КР580ВМ80А

Вона містить МП КР580ВМ80А, схеми синхронізації та схеми спряження і узгодження з системними магістралями.

Схема синхронізації призначена для формування двох послідовностей тактових імпульсів з необхідними часовими і амплітудними параметрами, які подаються на входи F1, F2 МП, а також для синхронізації зовнішніх кіл шляхом формування синхроімпульсів фазових послідовностей ТТЛ-рівня F1ТТЛ, F2ТТЛ; формування і синхронізації сигналів готовності та обнуління; керування покроковою роботою МП.

Для реалізації вказаних функцій в склад мікропроцесорного комплекту входить мікросхема системного генератора КР580ГФ24 (рисунок 4.9 - 4.10)

Рисунок 4.9 - Умовне зображення мікросхеми КР580ГФ24

Рисунок 4.10 – Функціональна схема КР580ГФ24

Мікросхема має задаючий генератор (ЗГ) – стабілізований зовнішнім кварцовим резонатором з максимальною частотою 18МГц; формувач синхроімпульсів (ФСІ) F1, F2, F2ТТЛ; тригери (Т) синхронізації сигналів початкової установки та готовності, а також схему формування стробу стану STSTB, яка використовується для запису байта в регістр стану.

Кола спряження (інтерфейс ЦП) з системними шинами реалізують наступні основні функції: формування сигналів адрес і пам’яті і пристроїв вводу-виводу, які поступають на адресну магістраль, приймання і передачі даних в двонаправлену шину даних; формування керуючих сигналів на системну шину керування.

Апаратні засоби інтерфейсу ЦП з системними шинами реалізуються шинними формувачами, регістром стану і схемою формування сигналів керування (див. рисунок 4.8).

Шинні формувачі (ШФ) призначені для узгодження магістралей ЦП з навантаженнями, з адресними та інформаційними колами модулів пам’яті та вводу-виводу.

Формувач адресної системної шини виконує функції адресного буфера і застосовується для збільшення навантажувальної спроможності США. Такий формувач працює на передачу в одному напрямку.

В комплекті К580 є низка інтегральних схем, які можуть виконувати функції шинних формувачів, зокрема це мікросхеми КР580ВА86, КР580ВА87 та КР580 ИР82.

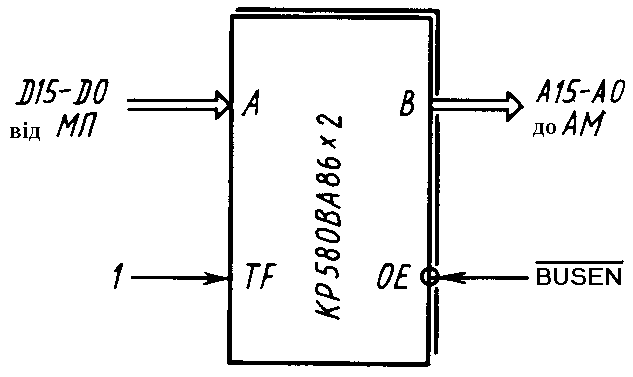

Мікросхеми КР580ВА86, КР580ВА87 є 8-розрядними двонаправленими формувачами, які забезпечують струм навантаження 32 мА. Вони мають двонаправлений канал А, який під’єднується до МП, і двонаправлений канал В, що під’єднується до системних шин ( рисунок 4.11- 4.13 ).

Рисунок

4.11–Умовне зображення мікросхемиКР580ВА86

Рисунок

4.12 - Функціональна схема КР580ВА86

Рисунок 4.13 – Схема підключення КР580ГФ86

Формувач

має виходи з трьома станами і керується

сигналами напрямку передачі даних і

відключення, які подаються на входи TF

i

![]() відповідно. Передачу інформації дозволено

при

відповідно. Передачу інформації дозволено

при

![]() =0;

причому якщо TF=1, то напрямок передачі

АВ,

якщо TF=0, то передача ведеться в напрямку

ВА.

При

=0;

причому якщо TF=1, то напрямок передачі

АВ,

якщо TF=0, то передача ведеться в напрямку

ВА.

При

![]() =1

виходи каналів А і В переводяться в

третій стан.

=1

виходи каналів А і В переводяться в

третій стан.

В адресному буфері (рисунок 4.14) вхід TF підключений до кола логічної одиниці. У формувачі СШД (рисунок 4.15) на вхід TF подається інвертований сигнал з виходу DBIN МП КР580ВМ80А.

Рисунок

4.14 – Схема підключення КР580ВА86 як

формувача США

Рисунок

4.15 - Схема підключення КР580ВА86 як

формувача СШД

Сигнали

керування формуються на основі байта

стану, який видає МП шиною даних і

сигналів керування DBIN та

![]() .

Для запам’ятовування і зберігання

байта стану використовується регістр

слова стану (Рr СС), в якості якого можна

використати різні інтегральні схеми

регістрів або тригерів.

.

Для запам’ятовування і зберігання

байта стану використовується регістр

слова стану (Рr СС), в якості якого можна

використати різні інтегральні схеми

регістрів або тригерів.

Найчастіше застосовують універсальні ВІС 8-розрядних регістрів К589ИР12 і КР580ИР82 (КР580ИР83).

Мікросхема КР580ИР82 є 8-розрядним регістром з керованими вихідними формувачами (рисунок 4.16 – 4.17).

Рисунок

4.16 – Умовне зображення мікросхеми

КР580ИР82

Рисунок

4.17 – Схема підключення

КР580ИР82

Запис

інформації відбувається за стробом,

який подається на вхід

![]() ;

читання інформації на виходах D0 можлива

при ОЕ=0. При використанні КР580ИР82 як

регістра РrCC (рисунок 4.18) необхідно

установити ОЕ=0, а на вхід

;

читання інформації на виходах D0 можлива

при ОЕ=0. При використанні КР580ИР82 як

регістра РrCC (рисунок 4.18) необхідно

установити ОЕ=0, а на вхід

![]() подати строб стану, який формується

системним генератором КР580ГФ24 або

спеціальною логічною схемою.

подати строб стану, який формується

системним генератором КР580ГФ24 або

спеціальною логічною схемою.

Рисунок 4.18 – Схема включення КР580ИР82 як РrCC і формувача СШК

Оскільки

адреси комірок пам’яті і пристроїв

вводу-виводу передаються загальною

адресною шиною, вони розділяються

сигналами керування

![]() ,

,

![]() ,

,

![]() ,

,

![]() ,

які формуються на основі бітів стану

Чт, вивід, ввід та сигналів з виходів

DBIN і

,

які формуються на основі бітів стану

Чт, вивід, ввід та сигналів з виходів

DBIN і

![]() МП. Реалізація схеми формувача США на

базі КР580ИР82 показана на рисунку 4.19.

МП. Реалізація схеми формувача США на

базі КР580ИР82 показана на рисунку 4.19.

Рисунок 4.19 - Схема включення КР580ИР82 в якості адресного буфера

Рисунок 4.20 – Мікросхема КР580ВК28

Для

спрощення інтерфейсу ЦП розроблена

спеціальна ВІС системного контролера

КР580ВК28 і КР580ВК38 (рисунок 4.20), яка

забезпечує формування вихідних сигналів

СШД, сигналів керування запам’ятовуючими

пристроями і пристроями вводу-виводу.

Мікросхема має двонаправлений шинний

формувач Ф, регістр стану (РгСС) і схему

формування керуючих сигналів (СФКС).

Формувач керується сигналами, які

подаються на входи DBIN, HLDA з відповідних

виходів КР580ВМ80А і зовнішнім сигналом

дозволу шини, який подається на вхід

BUSEN з контролера ПДП. Байт слова стану

запам’ятовується за стробом

![]() ,

що формується генератором КР580ГФ24.

,

що формується генератором КР580ГФ24.

Мікросхема

формує сигнали

![]() ,

,

![]() ,

,

![]() та

та

![]() .

Реалізація центрального процесора на

ВІС комплекту К580 приведена на рисунку

4.21.

.

Реалізація центрального процесора на

ВІС комплекту К580 приведена на рисунку

4.21.

Рисунок 4.21 – Структура центрального процесора на ВІС К580