- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

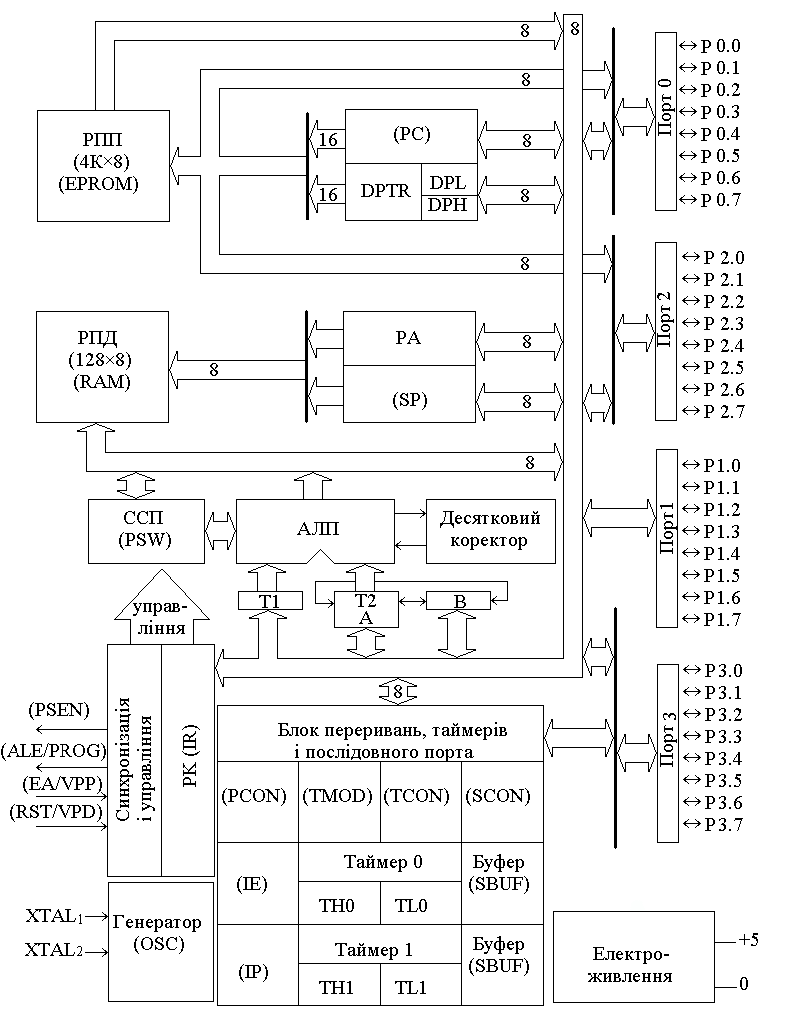

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

Арифметико-логічний пристрій

АЛП, розрядністю у 8-бітів, може виконувати арифметичні операції додавання, віднімання, множення і ділення; логічні операції І, АБО, ВИКЛЮЧАЮЧЕ АБО, циклічні зсуви, обнуління, інвертування тощо. В АЛП

Рисунок 8.2 Структурна схема МК51

є програмно недоступні регістри Т1 і Т2, що використовуються для тимчасового зберігання операндів, а також схема десяткової корекції і схема формування ознак.

АЛП може оперувати чотирма типами інформаційних об’єктів: булевими (1біт), цифровими (4 біти), байтовими (8 біт) і адресними (16 біт).

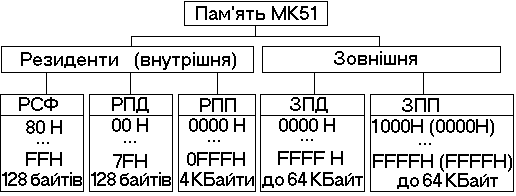

Структура пам’яті МК51

Загальну пам’ять МК можна розділити на п’ять фізичних адресних просторів, які розрізняються програмно, оскільки мають різні способи адресації, так і апаратно, тому що використовуються різні сигнали запису та читання (рисунок 8.3): зовнішня пам’ять програм (ЗПП); зовнішня пам’ять даних (ЗПД); резидентна пам’ять програм (РПП); резидентна пам’ять даних (РПД); регістри спеціальних функцій (РСФ).

Рисунок 8.3 Структура пам’яті

Внутрішня і зовнішня пам’яті програм утворюють єдиний адресний простір ємністю до 64 Кбайт і не розрізняються програмістом, але обов’язково відокремлюються на етапі проектування апаратних засобів.

Резидентна пам’ять

Пам’ять програм і даних (резидентна, тобто внутрішня) фізично і логічно розділені і мають різні механізми адресації.

Пам’ять програм (ПЗП) має ємність 4 Кбайти і використовується для зберігання команд, констант, керуючих слів ініціалізації тощо. Резидентна пам’ять програм (РПП) має 16-бітову шину адреси, яку генерує лічильник команд РС або команд, що формують пряму 8 або 16-розрядну адресу. Комірки 0000...0023Н зарезервовані під вектори переривань при їх обслуговуванні (тобто реалізуються переходи на підпрограми обслуговування переривань).

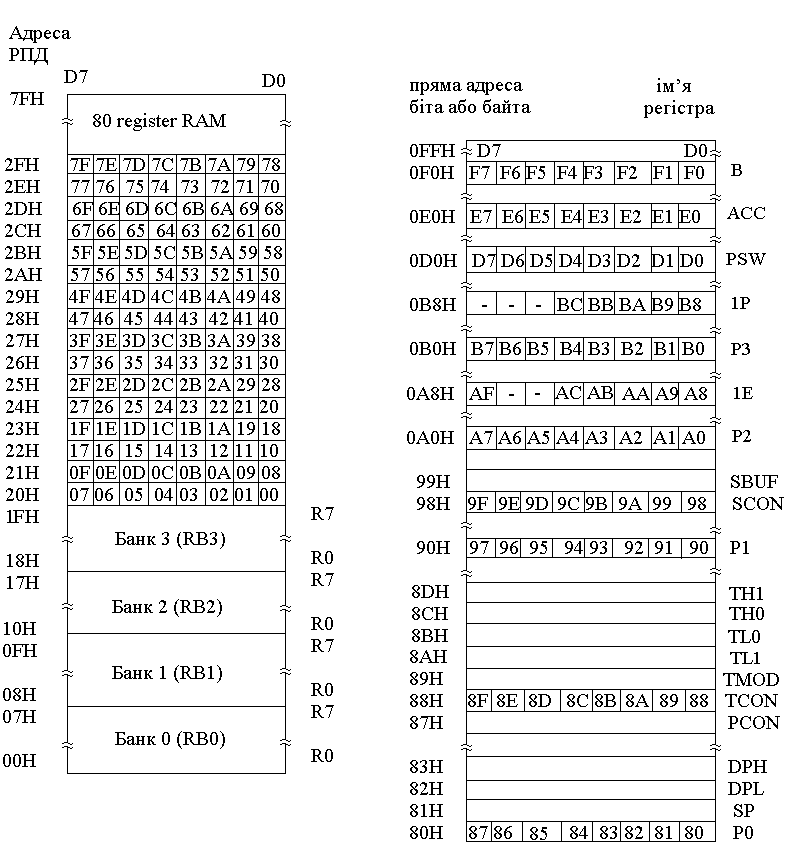

Резидентна пам’ять даних (РПД) виконує функції оперативної пам’яті і забезпечує зберігання проміжних результатів. Адресується одним байтом і має ємність 128 байтів. Вона складається з трьох частин (рисунок 8.4).

- 4 банки регістрів оперативного призначення з адресами 00...1FH;

- 16 байтових комірок з адресами 20...2FH, що одночасно утворюють область з 128 однобітових комірок окремої адресації з адресами 00...7FH;

- 80 байтових комірок ОЗП з адресами 30...7FH.

Регістри спеціальних функцій

Регістри спеціальних функцій займають область резидентної пам’яті з адресами 80...FFH. Перелік даних регістрів поданий в таблиці 8.5, а карта пам’яті на рисунку 8.4 - 8.5.

Таблиця 8.5- Блок регістрів спеціального призначення

|

Символ |

Назва |

Адреса |

|

*ACC |

Акумулятор |

0E0H |

|

*B |

Розширювач акумулятора |

0F0H |

|

*PSW |

Слово стану програми |

0D0H |

|

SP |

Покажчик стеку |

81H |

|

DPTR |

Регістр-покажчик даних (DPH) (DPL) |

83H 82H |

|

*P0 |

Порт 0 |

80H |

|

*P1 |

Порт 1 |

90H |

|

*P2 |

Порт 2 |

0A0H |

|

*P3 |

Порт 3 |

0B0H |

|

*IP |

Регістр пріоритетів |

0B8H |

|

*IE |

Регістр маски переривань |

0A8H |

|

TMOD |

Регістр режиму таймера/лічильника |

89H |

|

*TCON |

Регістр керування/статуса таймера |

88H |

|

THO |

Таймер 0 (ст.байт) |

8CH |

|

TLO |

Таймер 0 (мл.байт) |

8AH |

|

TH1 |

Таймер 1 (ст.байт) |

8DH |

|

TL1 |

Таймер 1 (мл.байт) |

8BH |

|

*SCON |

Регістр керування приймачем-передавачем |

98H |

|

SBUF |

Буфер приймача-передавача |

99H |

|

PCON |

Регістр керування потужністю |

87H |

Зауваження. Регістри зі значком (*), допускають адресацію окремих бітів.

Регістр В застосовується при виконанні команд множення і ділення, а також використовується як подовжувач акумулятора при обробці двобайтових чисел.

Акумулятор і ССП

Акумулятор є джерелом операнда і місцем фіксації результату при виконанні арифметичних, логічних операцій і операцій маніпулювання бітами. В МК51 акумулятор має звужене застосування, оскільки значна частина команд контролера може виконуватись без його участі.

|

бітів і байтів в РПД |

Рисунок 8.5-Карта заадресованих бітів і байтів в блоці спеціальних функцій |

Результат виконання багатьох команд в АЛП оцінюється ознаками (індикаторами), які фіксуються в регістрі слова стану програм (ССП). В таблиці поданий перелік індикаторів ССП (регістр PSW).

Таблиця 8.6- Формат слова стану програм (ССП).

|

Символ |

Позиція |

Ім’я і призначення |

|

C |

PSW.7 |

Індикатор переносу. Установлюється апаратними засобами або програмою при виконанні арифметичних і логічних команд. |

|

AC |

PSW.6 |

Індикатор додаткового переносу. Установлюється тільки апаратно при виконанні команд додавання і віднімання. |

|

F0 |

PSW.5 |

Індикатор 0. Може установлюватись програмно і визначається програмістом. |

|

RS1 RS0 |

PSW.4 PSW.3 |

Вибір банку регістрів. Установлюється програмно для вибору робочого банку регістрів (примітка). |

|

0V |

PSW.2 |

Індикатор переповнення. Установлюється апаратно за результатами виконання арифметичних команд. |

|

- |

PSW.1 |

Не використовується. |

|

P |

PSW.0 |

Індикатор паритету. Установлюється апаратно. |

Примітка. Вибір робочого банку регістрів

|

RS1 |

RS0 |

Банк |

Межі адрес |

|

0 0 1 1 |

0 1 0 1 |

0 1 2 3 |

00H-O7H 08H-0FH 10H-17H 18H-1FH |

Індикатор переносу С, крім звичайних функцій подовжувача акумулятора в командах додавання, віднімання і зсувів, виконує функції акумулятора в командах маніпуляції з однобітовими операндами. Індикатор 0V фіксує арифметичні переповнення в операціях зі знаковими числами. Крім того він установлюється в 1 також при діленні на нуль і якщо добуток в операціях множення перевищує 225.

Індикатор F0 визначається користувачем під будь-яку ознаку і може бути програмно установленим, обнуленим, перевіреним та про інвертованим.

Індикатори RS0 i RS1 визначають один з чотирьох можливих банків регістрів оперативного призначення. Індикаторами керує не АЛП, а програміст у відповідності до таблиці (див.примітку).

Функції індикатора додаткового переносу АС є аналогічними до його функцій в МП інших типів.

Необхідно зауважити, що акумулятор не відноситься до регістрів оперативного призначення, а разом з регістром PSW входить до складу регістрів спеціальних функцій.

Регістри-покажчики

8-бітовий покажчик стеку SP може адресувати будь-яку область РПД. Вміст регістра SP інкрементується завчасно ніж дані будуть записані в стек під дією команд PUSH i CALL.Вміст SP декрементується після виконання команд POP i RET. Після ініціалізації МК51 за сигналом ‘’Обнуління’’ в SP заноситься код 07Н. Тобто перший елемент даних в стеку буде розміщений в РПД за адресою 08Н.

Двобайтовий регістр-покажчик даних DPTR використовується для фіксації 16-бітової адреси в операціях зі зверненнями до зовнішньої пам’яті. Даний регістр може використовуватись як 16-бітовий або як два незалежні 8-бітових регістри DPH i DPL.

Таймери / лічильники

В складі апаратних засобів МК51 є регістрові пари з символьними іменами ТНО, TLO i TH1,TL1, що є основою двох незалежних програмно-керованих 16-бітових таймерів/лічильників подій.

Буфер послідовного порта

Регістр з символьним іменем SBUF представляє собою два незалежних регістра: буфер приймача і буфер передавача. Посилка байта в SBUF зразу ж викликає процес передачі через послідовний порт. Коли ж байт зчитується з SBUF, то джерелом є приймач послідовного порту.

Регістри спеціальних функцій.

Регістри з символьними іменами IE, IP, TMOD, TCON, SCON i PCON використовуються для фіксації і програмної зміни керуючих бітів і бітів стану схеми переривання, таймера/лічильника, приймача/передавача послідовного порта і для керування потужністю живлення МК51. Їх організація буде розглядатись далі.

Пристрій керування і синхронізації.

Кварцовий резонатор, під’єднаний до входів XTAL1 i XTAL2 МК51,керує роботою внутрішнього генератора, який формує сигнали синхронізації.

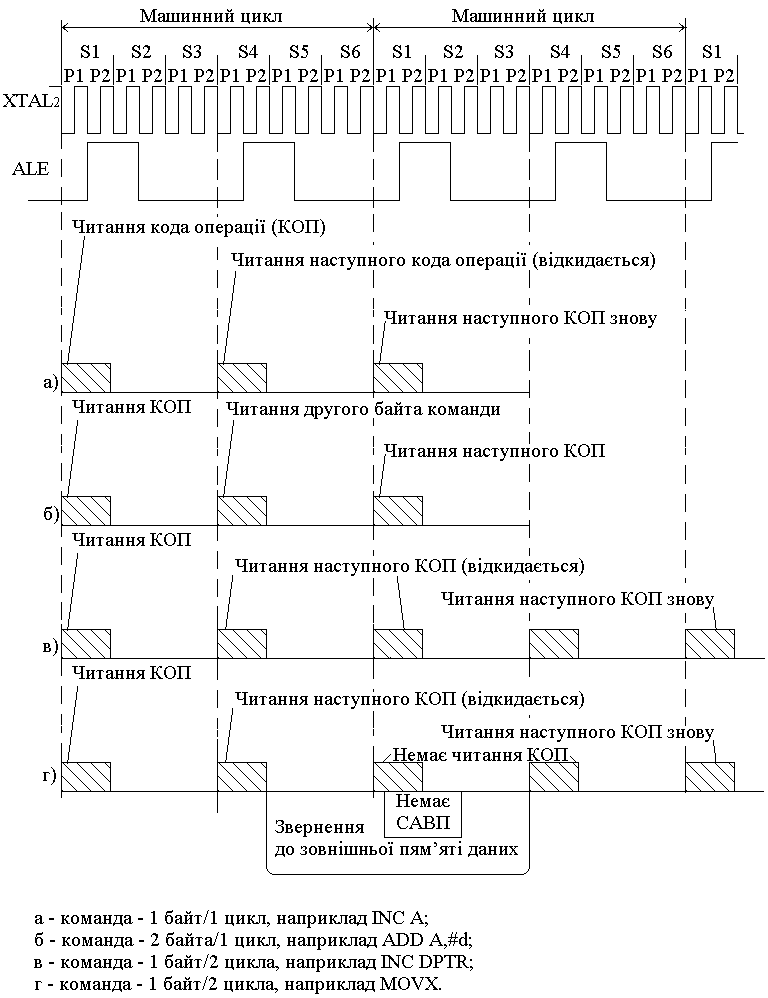

Пристрій керування МК51 на основі сигналів синхронізації формує машинний цикл фіксованої довжини, рівної 12 періодам резонатора або шести станам S1-S6 (рисунок 8.6).

Кожний стан керуючого пристрою має дві фази (Р1,Р2) сигналів резонатора. Весь машинний цикл складається з 12 фаз, починаючи з фази S1P1 і закінчуючи фазою S6P2. Зовнішніми сигналами, за якими можливе спостереження, є тільки сигнали резонатора і стробу адреси зовнішньої пам’яті ALE. Сигнал ALE формується двічі за один машинний цикл і використовується для керування процесом звернення до зовнішньої пам’яті.

Більшість команд МК51 виконуються за один машинний цикл (МЦ), деякі команди, що оперують з 2-байтовими словами виконуються за два МЦ, а команди ділення і множення за чотири МЦ.

Рисунок 8.6 Діаграма роботи керуючого пристрою при виборці і виконанні команд в МК51.

Порти вводу/виводу інформації

Всі чотири порти МК51 використовуються для вводу або виводу інформації побайтно, утворюючи 32-розрядну шину вводу-виводу. Кожний порт має керований регістр-фіксатор, вхідний буфер і вихідний драйвер. Фіксатор є 8-розрядним регістром з байтовою і бітовою адресацією для встановлення розрядів програмним шляхом. У ньому фіксуються тільки вихідні дані, але не фіксуються вхідні.

Вихідні драйвери портів 0 і 2, а також вхідний буфер порту 0 беруть участь при зверненні до зовнішньої пам’яті (ЗП). При цьому через порт 0 в режимі часового розділення спочатку виводиться молодший байт адреси комірки ЗП, а потім видається або приймається байт даних. Через порт 2 виводиться старший байт адреси в тих випадках, коли розрядність адреси рівна 16 бітам. Очевидно, що в цьому випадку дані порти не можуть бути використані для подовження шини вводу-виводу.

Всі виводи порту 3 можуть бути використані для реалізації альтернативних функцій (таблиця 8.4).

Звернення до портів вводу/виводу здійснюєьться через команди, що оперують з байтами, окремими бітами і комбінацією бітів.

Система команд МК51 дозволяє реалізувати два способи зчитування інформації з портів. Якщо в командах, порт виступає як джерело операнда, а результат формується в будь-якому іншому місці, тоді дані знімаються безпосередньо з виводів портів (наприклад, ANL A, P1-логічне І вмісту акумулятора і порта Р1 з розміщенням результату в акумуляторі). Коли ж регістр порту є одночасно операндом-джерелом і приймачем результату операції, пристрій керування реалізує спеціальний режим “читання-модифікація-запис”. Цей режим передбачає ввід сигналу не з зовнішніх виводів порта, а із його регістра-фіксатора, а потім модифікований байт перезаписується в регістр фіксатор, що виключає можливість неправильного прочитання рівнів сигналів на зовнішніх виводах.

Подібний механізм звернення до портів реалізований в таких командах:

|

ANLP1, A ; |

Логічне “І” акумулятора і вмісту Р1 |

|

ORL P2, A ; |

Логічне “АБО” акумулятора і вмісту порта Р2 |

|

JBC P1.1, LABEL ; |

Перехід на мітку LABEL, якщо в другому біті порту Р1 одиниця, з його наступним обнулінням |

|

CPL P3.3 ; |

Інверсія адресованого біта |

|

INC P2 ; |

Інкремент порта Р2 |

|

CLR PX. Y ; |

Обнуління біта Y порта X. |

Рисунок

8.4 Карта заадресованих

Рисунок

8.4 Карта заадресованих