- •Мікропроцесорна техніка

- •Мікропроцесорна техніка

- •Вступ....................................................................................5

- •Типові 8- та 16- розрядні мікропроцесори

- •5. Організація взаємодії мп з зовнішнім

- •1 Основні терміни. Структура та функціонування мікропроцесорної системи

- •2. Представлення чисел і елементи двійкової арифметики в цифрових пристроях

- •2.1 Позиційні системи числення

- •Шістнадцяткова система

- •Двійкова арифметика

- •Форми представлення чисел

- •3 Загальна характеристика та класифікація мп. Родини та комплекти мп.

- •Огляд мікропроцесорів відомих фірм-виробників

- •4 Типові 8- та 16- розрядні мікропроцесори для побудови мпс

- •4.1 Восьмирозрядний мікропроцесор 8080а

- •4.1.1 Архітектура і режими роботи мікропроцесора Архітектура мікропроцесора к580вм80а

- •4.1.2 Проектування центрального процесора

- •4.1.3 Система команд мп

- •4.2.1 Загальна характеристика ,архітектура та функціонування мікропроцесор

- •Архітектура мікропроцесора

- •Адресування пам'яті і організація вводу-виводу

- •Режими адресації

- •4.2.2 Система команд мікропроцесора вм86

- •5. Організація взаємодії мп з зовнішнім середовищем.

- •5.1 Інтерфейс

- •5.2 Порти вводу-виводу

- •5.3 Організація взаємодії елементів мпс

- •5.4 Типові методи вводу-виводу інформації в мпс

- •5.5 Інтерфейс з пзп

- •Інтерфейс з озп

- •Інтерфейс портів вводу/виводу

- •5.8 Загальні засади синтезу дешифраторів зовнішніх пристроїв

- •6 Пам’ять мікропроцесорних пристроїв

- •6.1 Основні характеристики і класифікація запам’ятовуючих

- •6.2 Надоперативні і оперативні запам’ятовуючі пристрої

- •6.3 Постійні запам’ятовуючі пристрої

- •Запам’ятовуючі пристрої з послідовним доступом

- •6.4 Організація модулів пам'яті мпс

- •7. Інтерфейсні віс для проектування мпс

- •7.1 Програмований адаптер паралельного інтерфейсу

- •7.2 Програмований зв’язковий адаптер

- •7.3 Програмований інтервальний таймер

- •8 Однокристальні мікроЕом

- •8.1.1 Мікроконтролер мк 51

- •Арифметико-логічний пристрій

- •Доступ до зовнішньої і резидентної пам’яті

- •Типи операндів та способи адресації

- •Команди логічних операцій

- •Команди операцій з бітами

- •Команди передачі керування

- •8.1.2 Родина мк52

- •8.1.3 Перспективна розробка фірми analog devices

- •8.2 Мікроконтролери фірми microchip

- •Основи програмування на мові Асемблера

- •Формат бланка асемблерної програми

- •9.2 Директиви асемблера

- •9.3 Макрокоманди

- •10 Загальні засади і особливості програмування та відлагодження мікропроцесорних пристроїв

- •10.1.2 Етапи проектування мпс

- •10.2.1 Системи програмування

- •10.2.2 Засоби трансляції і компіляції

- •10.2.3 Засоби редагування зв’язків і компоновки

- •10.3 Засоби відлагодження мікропроцесорних систем

- •Засоби для контролю та відлагодження аз мпс

- •10.3.1 Засоби відлагодження мікропроцесорних програм

- •10.3.2 Засоби комплексного відлагодження мпс

- •11.Когутяк м.І.Мікропроцесорний комплект к580 і його використання в керуванні.Навчальний посібник.- Івано-Франківськ ,2000.-96с.

- •13. Когутяк м. І.Однокристальні мікроЕом.Родина мк51 .Навчальний посібник.- Івано-Франківськ ,2000.-56с

7.2 Програмований зв’язковий адаптер

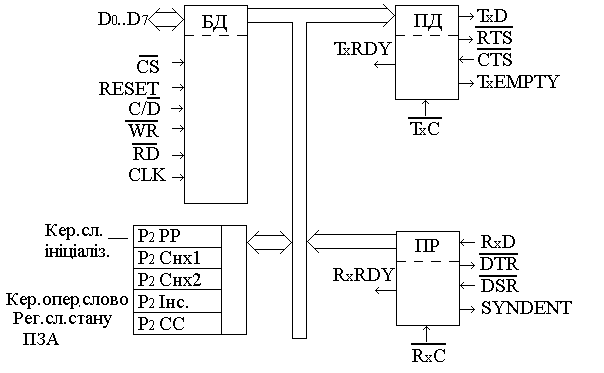

Програмований зв’язковий адаптер (ПЗА) є універсальним приймально-передавальним пристроєм, який перетворює зняту з СШД МПС інформацію з паралельної форми в послідовну, для організації передачі в лінію зв’язку, а також здійснює зворотне перетворення.

Коротко розглянемо роботу ПЗА. Універсальний приймач-передавач КР580 ВВ51А забезпечує функціонування каналу зв’язку з одно- або двонаправленим способом передачі інформації. Універсальність ПЗА полягає в тому, що завантаженням в нього керуючих слів програмується один із допустимих видів обміну (синхронний або асинхронно-синхронний), розрядність посилок, контроль за парністю, швидкість передачі і довжина стоп-сигналу (при асинхронно-синхронному обміні), а також синхросимволи і вид синхронізації (при синхрообміні).

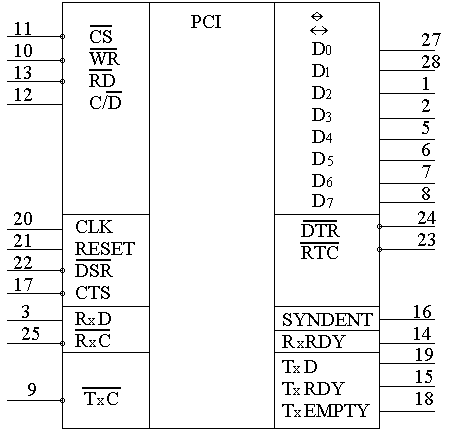

Структурна схема послідовного адаптера приведена на рисунку 7.6.Умовне графічне зображення ПЗА показане на рисунку 7.7, а призначення виводів подане в таблиці 7.3.

Рисунок 7.6

Риcунок 7.7 -Умовне графічне зображення ПЗА на принципових електричних схемах.

Таблиця 7.3 - Призначення виводів КР580 ВВ51А

|

Позначення |

Тип виводу |

Призначення |

|

D7-D0 |

вх-вих з z станом |

Шина даних |

|

|

Вхід |

Вибір мікросхеми |

|

|

Теж |

Запис |

|

|

Теж |

Читання |

|

|

Теж |

Керування/дані |

|

CLK |

Теж |

Синхросерія |

|

RESET |

Теж |

Обнуління |

|

|

Вихід |

Готовність прийняти дані |

|

|

Вхід |

Готовність модему |

|

|

Вихід |

Готовність передати інформацію |

|

|

Вхід |

Дозвіл передати інформацію |

|

TXD |

Вихід |

Синхронізація блока передавача |

|

|

Вхід |

Інформаційний вихід блока передавача |

|

TXEMTY |

Вихід |

Регістр блока передавача пустий |

|

TXRDY |

Вихід |

Готовність блока передавача до запису коду по шині даних |

|

RXD |

Вхід |

Інформаційний вхід блока приймача |

|

|

Вхід |

Синхронізація блока приймача |

|

RXRDY |

Вихід |

Готовність блока передавача до читання коду по шині даних |

|

SYNDENT |

Вихід-вхід |

Багатофункціональний вивід, призначення якого залежить від режиму роботи ПЗА та способу синхронізації |

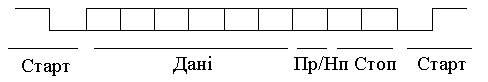

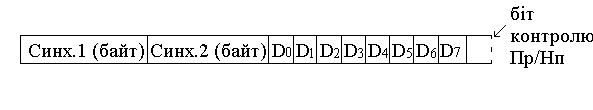

ПЗА в синхронному/асинхронному режимі роботи передає слово такого формату

П ри

синхронізованій передачі передається

посилка в такій формі

ри

синхронізованій передачі передається

посилка в такій формі

МП

зв’язаний з внутрішньою шиною адаптера

через СШД і буфер даних БД, при нульовому

керуючому сигналі вибору модуля (![]() ).

При нульових сигналах

).

При нульових сигналах

![]() i

i

![]() інформація передається з МП або в нього

відповідно (таблиця ).Сигнал

інформація передається з МП або в нього

відповідно (таблиця ).Сигнал

![]() (керування/дані) забезпечує передачу

керуючих слів або даних. Вхід CLK постійно

підключений до другої фази системного

генератора тактових імпульсів.

(керування/дані) забезпечує передачу

керуючих слів або даних. Вхід CLK постійно

підключений до другої фази системного

генератора тактових імпульсів.

Дані від периферійного пристрою приймаються через вхід RXD в приймач ПР. Дані в модем передаються з передавача ПД через вихід TXD.

Початкова установка і програмування ПЗА.

ПЗА

КР580 ВВ51 може знаходитись в таких режимах:

неробочому; програмування; обміну. В

неробочому режимі (на вхід

![]() подається сигнал високого рівня, або

подається сигнал високого рівня, або

![]() =0,

=0,

![]() =1

i

=1

i

![]() =1)

двонаправлені виводи D0-D7

ПЗА знаходяться знаходяться у

високоімнендансному стані: сигнал

високого рівня, що на вході RESET, переводить

ПЗА в режим програмування.

=1)

двонаправлені виводи D0-D7

ПЗА знаходяться знаходяться у

високоімнендансному стані: сигнал

високого рівня, що на вході RESET, переводить

ПЗА в режим програмування.

\

Таблиця 7.4 Режими роботи ПЗА.

|

|

|

|

|

Напрям передачі. Стан виводів D0..D7 |

|

1 |

0 |

1 |

1 |

Запис в ППА керуючих слів і синхросимволів СШДРгРР, Рг Синх1, РгСинх2) ПЗА |

|

0 |

0 |

1 |

0 |

Запис даних в буфер ПЗА СШДПЗА |

|

0 |

1 |

0 |

1 |

Читання слова стану СШДРг СС |

|

0 |

1 |

0 |

0 |

Читання даних з ПЗА (буфера) СШДПЗА |

|

0 1 |

1 * |

1 * |

* * |

z - стан виводів D0..D7 |

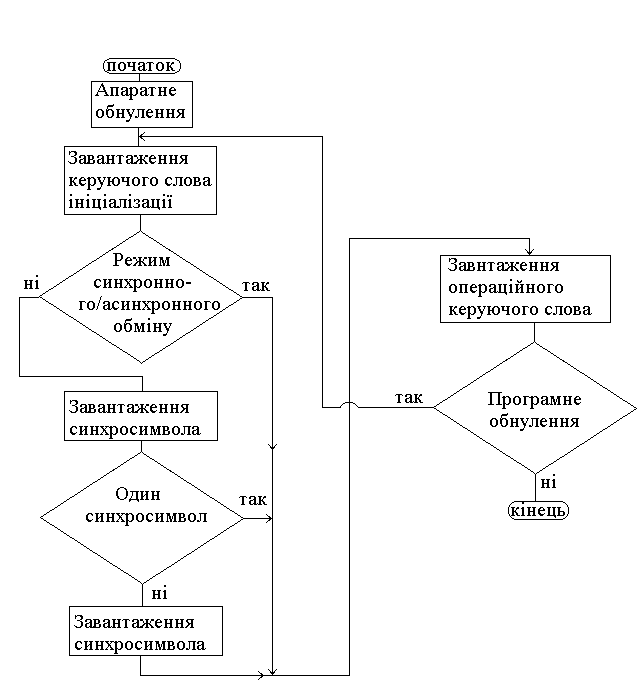

Процес програмування представляє собою завантаження керуючих слів і синхросимволів в послідовності, що визначається алгоритмом (рисунок 7.8).

Рисунок

7.8 Алгоритм програмування ПЗА.

Рисунок

7.8 Алгоритм програмування ПЗА.

Після

початкової установки, ПЗА сприймає

інформацію, що подається СШД як керуюче

слово ініціалізації (![]() =1)

і розміщує його у відповідний регістр.

Структура керуючих слів ініціалізації,

які визначають режими асинхронно-синхронного

і синхронного обмінів, зображені на

рисунку 7.9.

=1)

і розміщує його у відповідний регістр.

Структура керуючих слів ініціалізації,

які визначають режими асинхронно-синхронного

і синхронного обмінів, зображені на

рисунку 7.9.

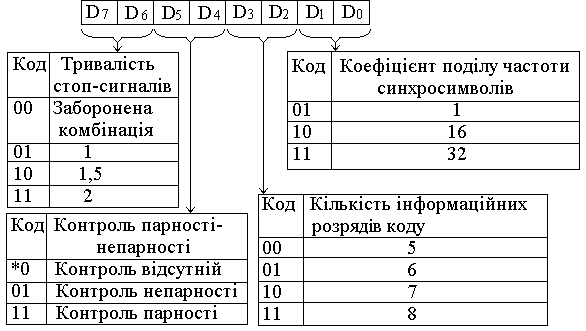

а)

асинхронно - синхронний обмін.

а)

асинхронно - синхронний обмін.

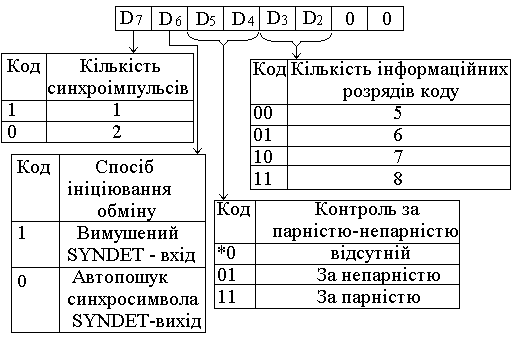

б) синхронний обмін

Рисунок 7.9 Структура керуючого слова ініціалізації ПЗА.

З рисунка видно,що керуюче слово ініціалізації задає:

1) режими роботи блоків приймання та передачі (асинхронно-синхронний, синхронний - розряди D0,D1) і крім того, в асинхронно-синхронному режимі коефіцієнт ділення частоти синхронізації, який визначає швидкість приймання (передавання) кодів з каналу зв’язку;

2) розрядність інформаційного коду (5, 6, 7 або 8- розряди D2, D3);

3) наявність в коді біта контролю за парністю (непарністю) (розряди D4, D5);

4) в режимі асинхронно-синхронного обміну - тривалість сигналу в кінці кодової посилки (1; 1,5 або 2 періоди синхросерії - розряди D6, D7) - програмується тільки для блоку передавача, оскільки блок приймача аналізує один стоп-біт. В режимі синхронного обміну - кількість синхросимволів на початку кодової посилки (1 або 2 - розряди D6, D7).

Після

завантаження керуючого слова ініціалізації

(для синхронного режиму і синхроімпульсів),

інформація, яка є на ШД системи,

інтерпретується як операційне керуюче

слово і заноситься (![]() =1

i

=1

i

![]() =0)

у відповідний регістр інструкцій. Формат

і функціональне призначення розрядів

операційного керуючого слова зображені

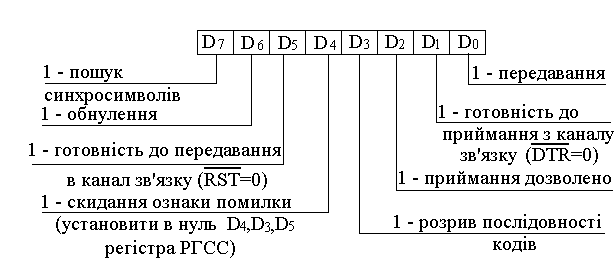

на рисунку 7.10.

=0)

у відповідний регістр інструкцій. Формат

і функціональне призначення розрядів

операційного керуючого слова зображені

на рисунку 7.10.

Рисунок 7.10 Формат операційного керуючого слова.

Завантаження слова з D6=1 аналогічні за дією апаратному обнулінню, тобто формуванню високого рівня на вході RESET.

При

організації режиму обміну між МП і

зовнішніми пристроями при допомозі ПЗА

часто виникає необхідність проаналізувати

його слово стану, яке можна зчитати з

РГСС командою IN (![]() =1;

=1;

![]() =0).

Одиничні сигнали в певних бітах

відповідають наступним станам:

=0).

Одиничні сигнали в певних бітах

відповідають наступним станам:

|

D0=1 |

сигнал TXRDY=1, що свідчить про готовність передавача адаптера прийняти дані від МП; |

|

D1=1 |

сигнал RXRDY=1, що свідчить про готовність передати дані в МП |

|

D2=1 |

сигнал TXEMPTY=1, свідчить про завершення передачі інформації з передатчика і відсутність в ньому даних; |

|

D3=1 |

в прийнятому символі виявлено порушення паритету (помилка паритету) |

|

D4=1 |

МП не прочитав попередню посилку даних до приходу наступної посилки даних (втрата символу) |

|

D5=1 |

в кінці посилки даних адаптер не виявив стопових бітів (помилка в форматі) |

|

D6=1 |

Сигнал виявлення синхронізації SYNDENT=1 (при внутрішній синхронізації цей сигнал є вихідним і фіксує появу символу синхронізації; при зовнішній синхронізації цей сигнал є вхідним і визначає періоди приймання даних з периферійного пристрою); |

|

|

RTS=0, свідчить про готовність передавача передати дані |

Послідовність зміни сигналів керування в різних режимах роботи МП така.

При

асинхронній і синхронній передачах

сигнал TXRDY

інформує МП про готовність адаптера

прийняти інформацію з СШД. Сигнал

TXRDY=1,

коли сигнал готовності приймача термінала

![]() =0,

в слові інструкцій D0=1

і передавач порожній (TXEMPTY=1).

Сигнали TXRDY

і TXEMPTY

стають низького рівня при формуванні

сигналу запиту переривання від МП

рівного нулю.

=0,

в слові інструкцій D0=1

і передавач порожній (TXEMPTY=1).

Сигнали TXRDY

і TXEMPTY

стають низького рівня при формуванні

сигналу запиту переривання від МП

рівного нулю.

Далі

за імпульсами на вході

![]() при умові, що

при умові, що

![]() =0

і в слові інструкцій D0=1,

дані побітно поступають на вихід (TXD).

Після передавання останнього біта

сигнал TXEMPTY

стане рівним одиниці.

=0

і в слові інструкцій D0=1,

дані побітно поступають на вихід (TXD).

Після передавання останнього біта

сигнал TXEMPTY

стане рівним одиниці.

При

асинхронному прийманні, коли в слові

інструкцій D2=1

імпульси на вході (RXC)

побітно вводять інформацію з входу

(RXD).

Наявність на цьому вході логічного нуля

свідчить про появу старт-біта. Подальша

поява стоп-біта викликає на виході RXRDY

сигнал одиничного рівня. Сигнал

![]() =0 обнулює вихід RXRDY.

Сигнали

=0 обнулює вихід RXRDY.

Сигнали

![]() ,

,

![]() ,

,

![]() забезпечують додаткові можливості при

взаємодії МП з периферійними пристроями.[

].

забезпечують додаткові можливості при

взаємодії МП з периферійними пристроями.[

].

Приклади програм налаштування ПЗА:

1. Режим асинхронно-синхронного обміну з дуплексним каналом зв’язку. В переданому коді заходяться: старт-біт, 8 інформаційних розрядів, біт контролю за парністю і два стоп-біти. Коефіцієнт поділу частоти рівний 16.

|

SUB 1: |

DI |

; |

|

|

XRA |

; обнуління акумулятора |

|

|

OUT ADR1 |

; Програмоване скидання |

|

|

OUT ADR1 |

; ADR1 - адреса ППА для запису |

|

|

OUT ADR1 |

; керуючих слів і слова стану |

|

|

MVI A,40 H |

; |

|

|

OUT ADR1 |

; |

|

|

MVI A,0FE H |

; 11111110 В - керуюче слово ініціалізації |

|

|

OUT ADR1 |

; |

|

|

MVI A,15 H |

; 00010101 В - операційне керуюче слово |

|

|

OUT ADR1 |

; |

|

|

EI |

; |

|

|

RET |

|

2. Режим синхронного приймання з автопошуком синхросимвола. Формат передаваної інформації: 8 інформаційних розрядів, біт контролю за парністю. Використовується синхросимвол 1000 0000.

|

SUB 2: |

DI |

; |

|

|

XRA |

; |

|

|

OUT ADR1 |

; Програмні обнуління |

|

|

OUT ADR1 |

; |

|

|

OUT ADR1 |

; |

|

|

MVI A,40 H |

; |

|

|

OUT ADR1 |

; |

|

|

MVI A,09C H |

; 10011100 - керуюче слово ініціалізації |

|

|

OUT ADR1 |

; |

|

|

MVI A,80 H |

; завантаження синхросимвола |

|

|

OUT ADR1 |

; |

|

|

MVI A,94 H |

; 10010100 - операційне керуюче слово OUT ADR1 |

|

|

OUT ADR1 |

; |

|

|

EI |

; |

|

|

RET |

|

CS

CS WR

WR RD

RD C/D

C/D DTR

DTR DSR

DSR RST

RST CTS

CTS TXC

TXC RXC

RXC D7=1

D7=1